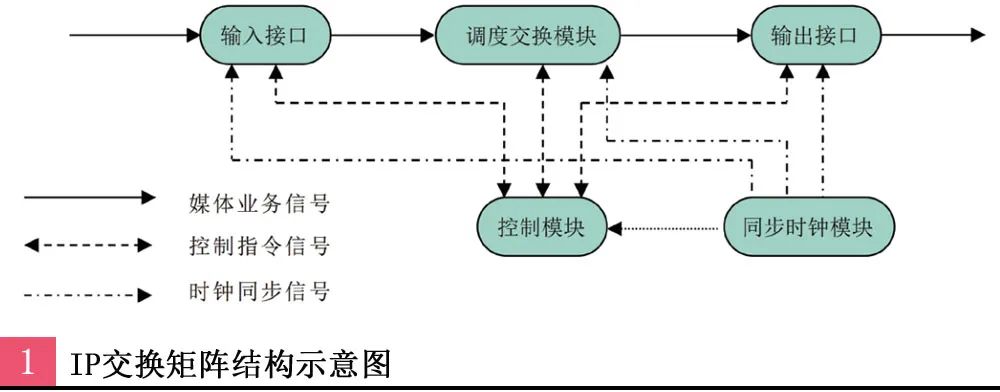

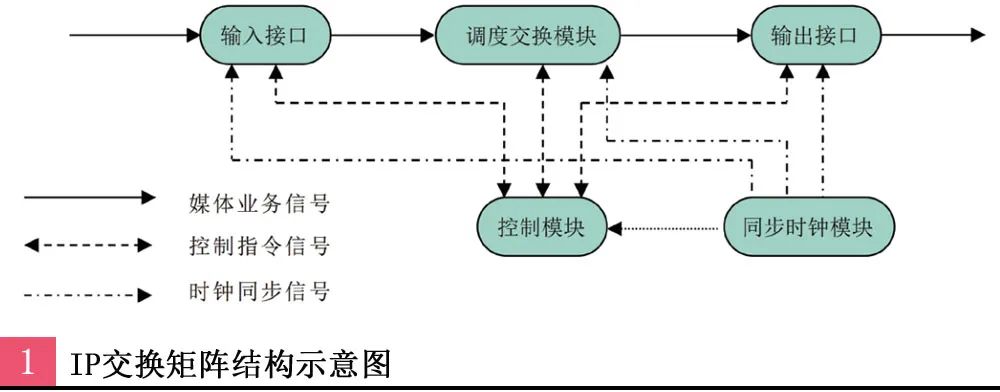

IP交换矩阵是由一级或多级交换设备及其控制器组成的单体矩阵,包含媒体业务信号、控制指令信号、同步时钟信号三个平面。

2023-12-04 14:13:45 816

816

4×4 矩阵式键盘电路的改进

2012-08-20 16:06:14

IP核加法器

2019-08-14 14:24:38

IP核生成文件:XilinxAlteraIP 核生成文件:(Xilinx/Altera同) IP 核生成器生成ip 后有两个文件对我们比较有用,假设生成了一个 asyn_fifo 的核,则

2012-08-12 12:21:36

本帖最后由 eehome 于 2013-1-5 09:59 编辑

IP核简介IP核是指:将一些在数字电路中常用但比较复杂的功能块,如FIR滤波器、SDRAM控制器、PCI接口等等设计成可修改

2011-07-06 14:15:52

IP核简介IP核是指:将一些在数字电路中常用但比较复杂的功能块,如FIR滤波器、SDRAM控制器、PCI接口等等设计成可修改参数的模块,让其它用户可以直接调用这些模块,以避免重复劳动。随着CPLD

2011-07-15 14:46:14

我想问一下,在quartus上直接调用IP核和在qsys中用IP核有什么区别?自个有点迷糊了

2017-08-07 10:09:03

我调用了一个ip核 在下载到芯片中 有一个time-limited的问题 在完成ip核破解之后 还是无法解决 但是我在Google上的找到一个解决方法就是把ip核生成的v文件加到主项目文件中就是上面

2016-05-17 10:28:47

fpga),现在需要完成一个cpu/fpga协同工作的任务,使用pcie总线通信。具体任务很简单:cpu通过pcie传两个32位浮点数给fpga,fpga相乘然后把结果返回。乘法模块使用quartus提供

2014-12-21 21:32:14

公司现需12bit sar adc的IP核,国内有哪些公司提供相关方面的服务了?

2015-11-06 08:37:44

用Quartus II 调用IP核时,在哪可以查看IP核的例程

2014-07-27 20:28:04

语言编写的浮点矩阵相乘处理单元[1],其关键技术是乘累加单元的设计,这样设计的硬件,其性能依赖于设计者的编程水平。此外,FPGA厂商也推出了一定规模的浮点矩阵运算IP核[2],虽然此IP核应用了本厂家的器件,并经过专业调试和硬件实测,性能稳定且优于手写代码,但仍可对其进行改进,以进一步提高运算速度。

2019-08-22 06:41:38

Altera_IP核,仅供参考

2016-08-24 16:57:15

Anlogic Float IP 基于 IEEE754 浮点数标准,实现了浮点数下的四则运算,IP 特色如下:IP 支持 Anlogic 所有器件

浮点数类型:半精度、单精度、双精度

浮点数计算

2023-08-09 07:53:03

在quartus2中创建了一个DDR2 控制器的ip核 ,但是在选择 DDR型号的时候,找不到我要用的DDR芯片信号 怎么办?选择了一个DDR芯片将它的行列bits数改了之后 发现 内存大小又不对 。求解答

2017-09-19 14:50:23

初始化时存入数据。那在IP核rom中存放大量数据对FPGA有什么影响,比如我想存65536个16位的数,然后在64M或者128M的时钟下读出来。会不会导致FPGA速度过慢?

2013-01-10 17:19:11

最近出现的 FPGA设计工具和 IP有效减少了计算占用的资源,大大简化了浮点数据通路的实现。而且,与数字信号处理器不同, FPGA能够支持浮点和定点混合工作的 DSP数据通路,实现的性能超过

2019-08-13 06:42:48

FPGA嵌入8051单片机 IP核编程,编写的c语言矩阵键盘程序可以在stc89c54单片机上正常工作,但是下载到FPGA中8051单片机ip核的rom中,不能正常工作,求指教

2013-07-25 21:27:44

本帖最后由 gk320830 于 2015-3-8 09:29 编辑

LCD的通用驱动电路IP核设计 摘 要:本文介绍了一种新型的LCD驱动电路IP核的总体设计,采用自顶向下的设计方法将其

2012-08-12 12:28:42

通用的IP核,使得用户可轻松集成属于自己的专用功能;但对于一些特定的外设,没有现成可用的IP核,如液晶模块CBGl28064等。用户可通过自定义逻辑的方法在SOPC设计中添加自定义IP核。在实际应用中

2019-08-06 08:29:14

最近在做FFT IP核,,走了好多弯路,LISENCE激活过了0034的IP核,通过修改LISENCE.DAT的方法。后来生成FFT的时候卡住,又尝试了关闭quartus_map进程和重装jre

2019-04-03 16:16:21

);v.BaseRpm为Q0格式v.Speed为Q15格式,他两个相乘为什么得到Q0格式的v.SpeedRpm。Q格式相乘不应该Q后面系数相加吗。

2020-05-19 10:34:07

本人使用RS IP核进行编码时出现IP核后面带有美元符号,不能正常使用。求大神给予破解帮助。

2019-08-20 11:34:00

。具体做法开始一个交互式会话,以便得到计算结果:一些其他有用的矩阵操作,如按元素相乘、乘以一个标量、按元素相除、按元素余数相除等,可以执行如下语句:tf.div 返回的张量的类型与第一个参数类型一致

2020-07-22 21:25:24

大家好,有没有谁比较熟悉ALTERA公司的VIP系列ip核,我们用该系列IP核中的某些模块(主要是scaler和interlacer)来实现高清图像转标清图像(具体就是1080p50转576i30

2015-04-13 14:12:18

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸载过Modelsim,用vivado打开过ISE工程,因为工程中很多IP核不能用所以在重新生成过程中发现了这个问题,还请大神告知是怎么回事?

2023-04-24 23:42:21

altera公司IP核使用手册,分享给想学习altera公司FPGA的IP核使用的亲们~~

2013-02-16 22:40:19

求用sopc builder定制IP核的步骤,是9.0的软件,假设硬件代码已有

2013-09-14 18:35:40

请问哪位高手有ise软件中的各个ip核的功能介绍

2013-10-08 16:41:25

labview怎样实现矩阵相乘A是nxm矩阵,B是mxp矩阵,如何实现C=AB;

2012-12-12 21:02:32

±B 其中Cij=Aij±Bij。2.2.2.2 乘 数量k与矩阵A相乘, 将A的每个元素都乘以k。MATLAB表达式形式:k*A 两矩阵A,B相乘,要求两个矩阵的相邻阶数相等,一般情况下

2009-09-22 15:34:40

有哪位大神用过pci ip核,为什么输入lm_req32请求,pci侧没有reqn请求输出呢?

2016-06-27 17:56:59

quartus 11.0 IP核的simulation如果勾选 就生成不出IP核出错,但是不选的话就没办法RTL仿真 求大神问题原因或者解决方法

2016-11-25 20:39:45

本帖最后由 ys_1*****8201 于 2016-5-19 14:16 编辑

Quartus IP核破解在完成quartus软件安装之后,一般都要进行一个软件破解。对于一般的需求来说

2016-05-19 14:13:09

2.5MHz 振幅0-5V 的正弦信号,请问 data 端口应该输入怎样的信号?如果有Altera IP核相关的详解资料推荐下更好。多谢了。

2014-10-28 12:34:41

ip 核应用

2012-05-26 15:26:27

在quartusII中,应用fft ip核时,variable streaming 模式下的bit-reverse(位翻转)是什么意思?烦劳详细帮助新手解释一下,不甚感激

2017-01-09 10:55:59

数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言中的printf()函数),可以直接调用,非常方便,大大加快了开发速度。使用Verilog调用IP

2018-05-15 12:05:13

vivado三种常用IP核的调用当前使用版本为vivado 2018.3vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点

2021-07-29 06:07:16

有没有大神可以提供xilinx FPGA的FFT IP核的调用的verilog 的参考程序,最近在学习FFT的IP核的使用,但是仿真结果有问题,所以想找些参考设计,谢谢

2016-12-25 17:05:38

两单精度浮点数相乘是先转换成二进制再相乘还是直接相乘,求教思路或程序

2016-10-23 23:36:36

大家好, 我在乘法模式下使用浮点7.0核心,即使对于小输入值,大多数时候核心输出也会非常高,核心配置: 1.在非阻塞模式下,单精度浮点 2.输入“a”是常量(32位) 3.输入“b”是以108Mhz

2020-03-25 09:07:58

刚刚接触IP核做FFT,现在用的是FFTV9.0,已经建立了一个IP核,但是如何仿真呢?是用quartus自带软件,还是要用MATLAB?抑或其他?我用的自带软件,但是什么也没有出来。正确的办法应该怎样呢,谢谢指点。

2011-04-21 10:22:31

最近在做一个FIR低通滤波器,利用Matlab 产生滤波系数,导入到Quartus中,再利用其中的FIR IP核进行滤波器设计,在采用分布式全并行结构时,Modelsim 仿真有输出;如果改为分布式

2018-07-05 08:33:02

quartus ii9.0创建的ip核,生成的一些文件,(.qip、 add_sub_bb.v、add_sub.v)这些文件都有用吗,想在其他工程里调用这些IP核,这几个文件全部要添加吗?

2013-07-02 17:20:01

在quartus II13.0版本上调用FFT IP核并进行modelsim-altera仿真,在生成IP核时,step2中勾选generate simulation model、generate

2016-10-07 22:23:33

核的分类和特点是什么?基于IP核的FPGA设计方法是什么?

2021-05-08 07:07:01

引言随着半导体技术的发展,深亚微米工艺加工技术允许开发上百万门级的单芯片,已能够将系统级设计集成到单个芯片中即实现片上系统SoC。IP核的复用是SoC设计的关键,但困难在于缺乏IP核与系统的接口标准

2019-06-11 05:00:07

我毕业设计要做一个基于FPGA的IP核的DDS信号发生器,但是我不会用DDS的IP核,有没有好人能发我一份资料如何用IP核的呀。我的浏览器下载不了网站上的资料,所以只能发帖求帮忙了。

2015-03-10 11:46:40

基于FPGA的FFT和IFFT IP核应用实例AT7_Xilinx开发板(USB3.0+LVDS)资料共享腾讯链接:https://share.weiyun.com/5GQyKKc百度网盘链接

2019-08-10 14:30:03

我们在嵌入式上跑矩阵运算时候,会遇到这样一个问题。假设将矩阵设置成N*N维的二维数组后,我们想求两个矩阵相乘,那就需要按照矩阵计算规则编写矩阵相乘函数,而且4*4矩阵得编一个,5*5矩阵又得编一个

2021-07-16 06:56:52

通用的IP核,使得用户可轻松集成属于自己的专用功能;但对于一些特定的外设,没有现成可用的IP核,如液晶模块CBGl28064等。用户可通过自定义逻辑的方法在SOPC设计中添加自定义IP核。在实际应用中

2019-08-05 07:56:59

是拥有完整的IP核产品线。如果你选择软核,应该确认该公司提供的是考虑了未来产品改进的完整软核产品线。如果你选择硬核,应确认它可提供所有你将使用的工艺技术,他们是否计划扩展其提供的软核产品?他们如何计划将

2021-07-03 08:30:00

将四字节16进制数转化为浮点数近期机缘凑巧帮了朋友一个忙,在Modbus协议下,将采集到的十六进数转化为浮点数,有几种解决方法,分享给需要的朋友,令其少走一些弯路。众所周知,Modbus通信协议

2018-12-01 06:13:07

核测试前的准备工作。

HLS 工程生成的 IP 核为 HLS_accel_0。图 64

4.4.1 PL 端 IP 核测试 Vivado 工程说明浮点矩阵乘法运算加速器 IP 核通过 AXI DMA

2023-08-24 14:52:17

的 IP 核为 HLS_accel_0。图 644.4.1 PL 端 IP 核测试 Vivado 工程说明浮点矩阵乘法运算加速器 IP 核通过 AXI DMA IP 核连接到 PS 端 ACP 接口,从而

2023-01-01 23:50:04

求助,有没有大神用verilog写过浮点矩阵乘法器的,我写出浮点乘法器和加法器之后就进行不下去了,急求助!!!只有一个积分~~~

2017-09-18 09:22:03

求助:用的Quartus13.0,选的modelsim仿真,Run Functional Simulation加法器IP核是Arithmetic下的ALTFP_ADD_SUB,设置是double

2015-06-25 16:05:50

本文介绍了一种基于FPGA的复数浮点协方差矩阵实现方案。

2021-04-29 06:01:31

@特权老师:特权老师,您好!最近买了您写的“PGA数字图像采集与处理”一书,书中第5章色彩滤波矩阵IP核 Demosaic 中的一段程序代码不明白!请问o_rgb_image_rst这个输出图像复位信号为1时的两个条件:dly>=12'd3200 &&dly

2021-04-01 08:41:05

数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言中的printf()函数),可以直接调用,非常方便,大大加快了开发速度。使用Verilog调用IP

2018-05-16 11:42:55

`错误提示截图放在二楼,用vivado14.4写了个1×8和8×8矩阵相乘的程序,调用了64个ip核乘法器,IO口用的有些多。综合和实现网表都能成功,就是仿真总是提示这两个错误,仔细检查了几遍程序

2020-04-26 19:21:25

本人FPGA小白一枚,最近使用到FPGA的IP核遇到一个问题。比如说:某个IP,用于计算sin函数,使用了流水线机制,所有从输入到输出需要20个时钟周期的延时。另外,还有一个IP,从输入到输出需要1

2021-06-19 11:06:07

请问Altera RAM IP核怎么使用?

2022-01-18 06:59:33

是Q21格式的,后面是Q15格式,看IQMath文档_IQmpy是两个Q格式相同的数相乘的,请问不同Q格式的用这个相乘怎么理解??

2018-11-22 09:59:34

在dspLib里只有矩阵转至和相乘的算法,还有没其他库有更多矩阵算法呢?

2018-07-27 10:01:18

指出现有差别矩阵属性约简算法的不足,对原有差别矩阵和属性重要性度量方法进行改进,运用差别矩阵元素项的重要性质,提出一种新的启发式约简完备算法,有效地降低差别矩

2009-03-28 09:34:22 15

15 本文对经典矩阵相乘A*B 算法提出多种优化方法:根据局部性原理,提出对矩阵B进行转置;根据计算机缓存的大小与矩阵A 与矩阵B 的规模进行嵌套循环分块,通过对分块大小的调

2010-01-27 13:37:55 25

25 在阵列信号处理中需要大量的矩阵运算,而其中最基本的就是矩阵相乘运算。本文就矩阵相乘的行划分并行实现进行了改进,将A矩阵的一行和整个B矩阵传输到每个工作进程,其中第一个

2010-07-27 16:30:27 9

9 矩阵相乘的速度在阵列信号处理中具有重要意义,并行处理是提高系统运算能力最有效的方法。本文根据矩阵相乘的特点,提凡了矩阵相乘的并行算法。同时经分析携姆出了矩阵相乘的

2011-10-12 16:27:41 74

74 嵌入式计算作为新一代计算系统的高效运行方式,应用于多个高性能领域,如阵列信号处理、核武器模拟、计算流体动力学等。在这些科学计算中,需要大量的浮点矩阵运算。而目前已

2012-10-15 16:57:40 3824

3824

浮点具有更大的数据动态范围,从而在很多算法中只需要一种数据类型的优势。本文介绍如何使用Vivado HLS实现浮点复数矩阵分解。使用HLS可以快速,高效地实现各种矩阵分解算法,极大地提高生产效率, 降低开发者的算法FPGA实现难度。

2017-11-18 12:00:11 852

852

一致,均为3x3方阵。激活区域与滤波器对应系数相乘并相加即获得对应的输出(这里是矩阵元素对应相乘相加,不是矩阵乘法)。紧接着,滑窗右移一格,得到新的激活区域,再次与滤波器对应元素相乘相加获得第2个输出。这里滑窗的步进为1。当滑窗右侧边缘与

2021-03-03 14:49:47 5049

5049 矩阵乘法是所有数学中最基本和最普遍的运算之一。要将一对 n×n 矩阵相乘,每个矩阵都有 n^2 个元素,你可以将这些元素以特定组合相乘并相加以生成乘积,即第三个 n×n 矩阵。将两个 n×n 矩阵相乘的标准方法需要 n^3 次乘法运算,因此,例如,一个 2×2 矩阵需要八次乘法。

2022-12-02 16:35:11 368

368

正在加载...

电子发烧友App

电子发烧友App

评论