I/O约束(I/O Constraints)包括I/O标准(I/OStandard)约束和I/O位置(I/O location)约束。

2023-11-18 16:42:28 506

506

下载附件,解压,运行k-mac.exe,选择某个网卡将它的mac地址设置为28-D2-44-1B-72-1D,重启机器,然后在QuartusII的tools->license setup将license文件设置为28D2441B721D_20161120.dat

2015-10-29 09:31:32

QuartusII基本使用方法

2012-08-06 13:53:18

QuartusII教程官方中文版. 目录: 第1章: 设计流程 ......................................... 1 第2章: 设计输入

2019-05-07 13:05:17

QuartusII新建一个工程进行编译并烧写的方法

2012-04-03 08:10:37

近期做了一个数据采集传输模块,用QuartusII编程设计的,采用FT245RL芯片进行USB通信。最近遇到一个问题,程序下载进PCB板以后多次出现无法识别USB口的问题。而且对同一个程序,哪怕修改

2019-06-29 14:46:38

设定就行了。主要是指你的某些管脚在电路当中起到了时钟管脚的 作用,比如flip-flop的clk管脚,而此管脚没有时钟约束,因此QuartusII把“clk”作为未定义的时钟。 措施:如果clk不是时钟

2018-07-03 01:34:46

希望从一个输入引脚到多个寄存器的输入端(D)的延时尽可能保持一致,可以设置这样的约束吗?器件是Cyclone4.

2012-04-11 15:32:53

求助:大哥们有没有Quartusii的详细资料啊,就说明怎样建立project,然后定义管脚仿真之类的东东。感激不尽。

2012-11-05 09:24:10

TCO2-532+

2023-04-06 23:32:40

这里主要是指对生态环境的保护,TCO认证在这方面限制了这些有害因素在显示器产品中的含有量,以达到保护生态环境的效果。

2020-03-20 09:00:35

EVAL MODULE FOR TSU3721

2023-03-29 22:52:02

TSU8111 SINGLE CELL USB CHARGER

2023-03-23 08:11:32

在quartusII中,应用fft ip核时,variable streaming 模式下的bit-reverse(位翻转)是什么意思?烦劳详细帮助新手解释一下,不甚感激

2017-01-09 10:55:59

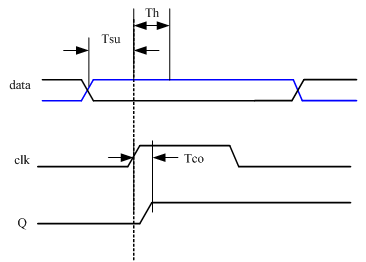

FPGA中几个基本的重要的时序分析参数介绍(fmax\tsu\th\tco\tpd)今天无聊,翻开书偶看到介绍时序部分的东西,觉得其中几个参数缩写所代表的含义应该记住,故写如下文章……FPGA中

2012-04-09 09:41:41

的计算模型 由图(1)可以看出,在影响Fmax 的四个参数中,由于针对某一个器件Tsu 和Tco 是固定的,因此我们在设计中需要考虑的参数只有两个Tlogic 和Troute.通过良好的设计以及一些如

2018-08-21 09:46:15

时钟路径。在本实例中,以上的约束将会覆盖如图8.27所示的时钟。(特权同学,版权所有)图8.27 时钟约束可覆盖路径接着,对lcd_clk这个时钟进行约束,它需要约束为虚拟(virtul)时钟,将会被用于

2015-07-30 22:07:42

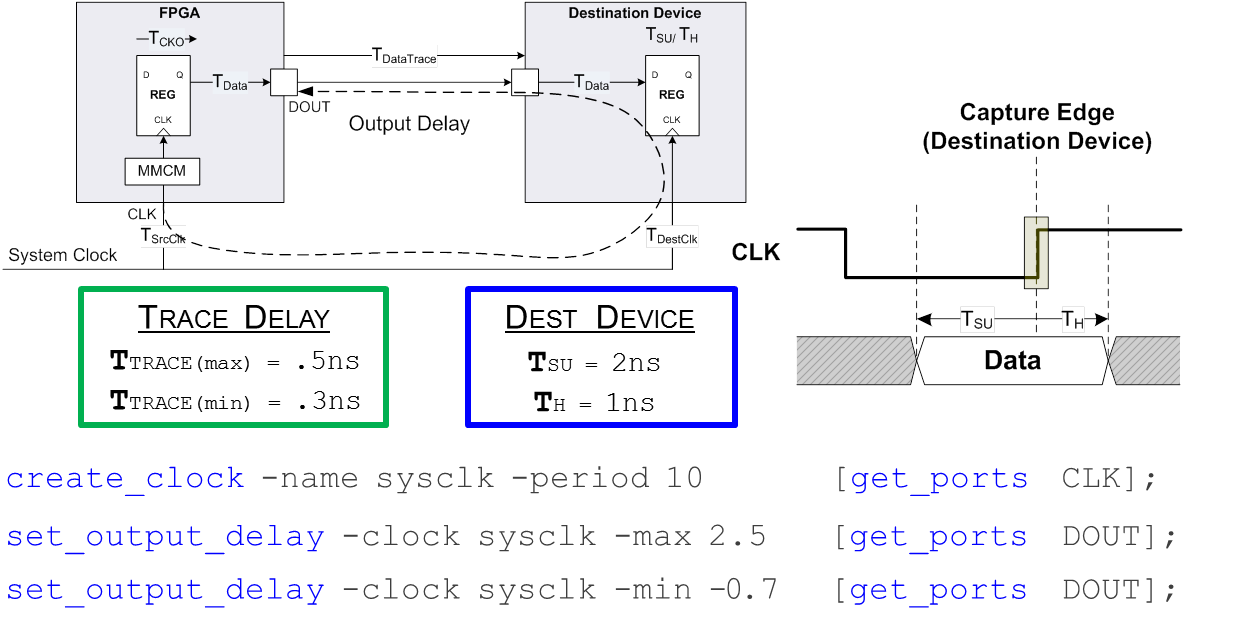

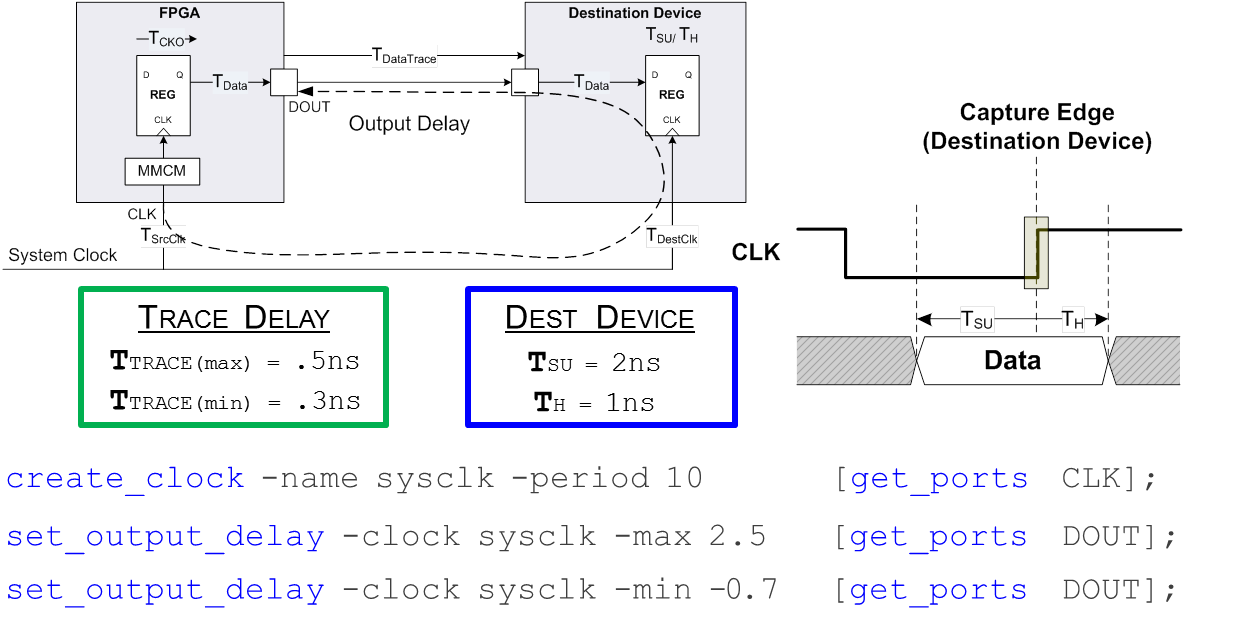

关系需要满足,其公式如下:Launch edge + Tc2t + Tco + Tr2p+Tdpcb < latch edge + Tc2r - Tsu对于保持时间,有基本的时序关系需要满足,其

2015-08-02 19:26:19

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间

2023-11-15 17:41:10

控。从最近一段时间工作和学习的成果中,我总结了如下几种进行时序约束的方法。按照从易到难的顺序排列如下:0. 核心频率约束 这是最基本的,所以标号为0。1. 核心频率约束+时序例外约束 时序例外约束包括

2016-06-02 15:54:04

过于繁多,在qsf文件中保存不下,得到保留的网表可以以Partial Netlist的形式输出到一个单独的文件qxp中,配和qsf文件中的粗略配置信息一起完成增量编译。 4. 核心频率约束+时序例外约束

2017-12-27 09:15:17

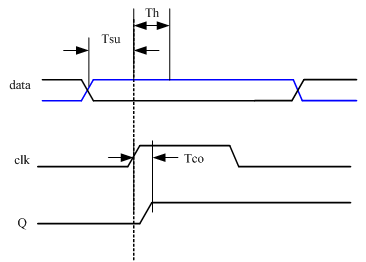

源端口出发到达源寄存器时钟端口的延迟Tclk2:时钟从时钟端口出发到达目的寄存器时钟端口的延迟Tco:时钟上升沿到达寄存器到数据从D端输出到Q端的延迟Tdata:数据从源寄存器Q端到目的寄存器D端的延迟Tclk:时钟周期Tsu:建立时间,时钟上升沿到达寄存器前,数据必须提前n纳秒稳定下来,这个...

2021-07-26 08:00:03

+ 组合逻辑延时Tlogic + FPGA内部的网络延时Tnet + 寄存器时钟建立时间Tsu –时钟偏斜TclkskewFmax = 1 / Tclk在QuartusII时序分析后很容易看到Fmax

2018-07-03 02:11:23

+ 组合逻辑延时Tlogic + FPGA内部的网络延时Tnet + 寄存器时钟建立时间Tsu –时钟偏斜TclkskewFmax = 1 / Tclk在QuartusII时序分析后很容易看到Fmax

2018-07-09 09:16:13

FPGA静态时序分析——IO口时序(Input Delay /output Delay)1.1概述 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能

2012-04-25 15:42:03

: Tmin = Tco + Tdata + Tsu - Tskew (公式3-8)4. 应用分析4.1设置时钟主频约束 所有的静态时序分析

2012-01-11 11:43:06

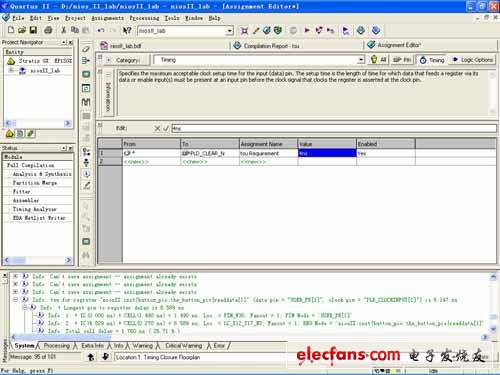

affect the logic placement but only can apply to I/O pin–Tsu?? NO! NO! Tsucan affect the logic

2008-09-11 09:20:30

Quartus II中Tsu/Tco的约束方法是什么

2021-04-29 06:36:32

关系需要满足,其公式如下:Launch edge + Tc2t + Tco + Tr2p+Tdpcb < latch edge + Tc2r - Tsu对于保持时间,有基本的时序关系需要满足,其

2019-04-10 06:33:34

的设定。这两个约束比较简单,容易设定,但是非常关键。如果设定的不好,系统性能会大打折扣。false path 是指在时序分析中不考虑其延迟计算的路径。例如有些跨越时钟域的电路等。设定的方法

2012-03-05 15:02:22

一个好的习惯就是,写代码一定要记得写注释。怎么碰到了这么个怪问题:Quartusii 9.0中

2009-11-08 17:06:49

edge、Tsu、Th、Tco:发射沿、锁存沿、建立、保持、数据输出延时(Tco):这个时间指的是当时钟有效沿变化后,数据从输入端到输出端的最小时间间隔。 四、时序约束(1)周期约束TIMESPEC

2017-03-09 14:43:24

时间,使(Tclk + clk skew)-(Tco+Tdelay) > Tsu,set min delay 约束Tco和clk skew满足外设的保持时间,(Tco

2023-05-06 16:24:12

时序工具 关于时序工具的一些FAE解答: 问:你们的工具是否只提供所有输入输出管脚完全一致的时序约束?如tsu,th,tco,tpd的约束?如果不同管脚可以有不 同约束值,如何设置

2021-10-12 09:22:08

此版只讨论时序约束约束理论约束方法约束结果时钟约束(Clock Specification): 约束所有时钟(包括你的设计中特有的时钟)对准确的时序分析结果而言是必不可少的。Quartus II

2013-05-16 18:51:50

好的时序是设计出来的,不是约束出来的时序就是一种关系,这种关系的基本概念有哪些?这种关系需要约束吗?各自的详细情况有哪些?约束的方法有哪些?这些约束可分为几大类?这种关系仅仅通过约束来维持吗?1

2018-08-01 16:45:40

求16.5安装方法和约束设置

2012-05-24 22:32:46

本文在开环时序仿真的基础上提出一种基于QuartusII、DSP Builder和Modelsim的闭环时序仿真测试方法,并借助于某一特定智能控制器的设计对该闭环测试方法进行了较为深入的研究。

2021-05-06 09:36:44

# ** Error: E:/QuartusII13/test2/fir2_ast.vhd(32): Library auk_dspip_lib not found.# ** Error: E

2018-04-23 12:33:00

1.quartusii 9.1 生成的testbench 后用VHDL 编写后续程序的格式, 方法2如何用modelsim 关联quartusii仿真3是不是testbench 没有问题了在quartusii 执行 RTL simulation 就可以从modelsim得到 波形

2013-05-17 21:36:56

喜我对我的设计中的关键路径以及如何约束它们有疑问。我正在使用ISE 14.1进行实施。我有一个设计,其中关键路径(从源FD到目的地FD)给出-3.3ns的松弛(周期约束为10ns)。现在有没有其他方法

2019-04-08 08:58:57

我正在设计一个双向ddr i / o电路,但遇到时序约束失败。器件为A7-100-FGG484-2,开发环境为vivado 2016.2。当电路作为输入(t_rn = 1)运行时,ddr输入引脚

2020-08-28 06:14:43

我是一个FPGA初学者,关于时序约束一直不是很明白,时序约束有什么用呢?我只会全局时钟的时序约束,如何进行其他时序约束呢?时序约束分为哪几类呢?不同时序约束的目的?

2012-07-04 09:45:37

,所以,Tco即我们的约束部分,Tsu即SDRAM的建立时间,又因为,altera官方提供的资料,不用时钟偏斜这一概念,用的是时钟网络延时, 即时钟网络延时=- 时钟偏斜,即Tc2s -Tc2d 所以

2015-03-31 10:20:00

现有的半监督聚类方法较少利用数据集空间结构信息,限制了聚类算法的性能。该文提出一种基于密度的约束扩展方法(DCE),将数据集以图的形式表达,定义一种基于密度的图形相似

2009-04-22 09:32:45 25

25 传统序列模式挖掘算法往往忽略了序列模式本身的时间特性,所考查的序列项都是单一事件,无属性约束。提出了一种挖掘多属性约束事件序列关联规则的方法。此方法基于传统

2009-06-17 11:08:30 10

10 时序约束与时序分析 ppt教程

本章概要:时序约束与时序分析基础常用时序概念QuartusII中的时序分析报告

设置时序约束全局时序约束个别时

2010-05-17 16:08:02 0

0 The TSU5511 is designed to interface the cell phone UART, USB, and audio chips with external

2010-09-10 00:09:59 24

24 时序约束用户指南包含以下章节: ?第一章“时序约束用户指南引言” ?第2章“时序约束的方法” ?第3章“时间约束原则” ?第4章“XST中指定的时序约束” ?第5章“Synplify中指定的时

2010-11-02 10:20:56 0

0 TCO在CRT方面的对比

随着时间的发展,原有的TCO99标准已经难以适应新的LCD、PDP等采用新式显示技术的显示器。于是TCO联盟开始制定最新的TCO03标准,

2009-12-26 17:06:32 768

768 TCO在LCD方面的对比

随着时间的发展,原有的TCO99标准已经难以适应新的LCD、PDP等采用新式显示技术的显示器。于是TCO联盟开始制定最新的TCO03标准,

2009-12-26 17:10:05 804

804 TCO的历史

2009-12-26 17:11:29 703

703 服务器操作系统TCO概览(1)

1. 服务器操作系统TCO构成 计世资讯(CCW Research)将全部企业不同操作系统、不同服务器应用的

2010-01-29 13:56:13 1267

1267 QuartusII免费下载入口

2012-07-01 17:12:25 547

547 QuartusII软件安装入口

2012-10-19 08:19:35 45

45 QuartusII_12.0下载入口

2014-02-24 11:36:44 31

31 QuartusII软件免费安装

2017-04-17 17:28:00 13

13 quartusII是一款非常棒的软件,FPGA现在市面上应用越来越广,有兴趣的可以看看此教程

2015-11-16 11:35:42 9

9 FPGA时序约束方法很好地资料,两大主流的时序约束都讲了!

2015-12-14 14:21:25 19

19 QuartusII简介(中文版),好东西,喜欢的朋友可以下载来学习。

2016-01-18 15:31:05 0

0 FPGA学习资料,有兴趣的同学可以下载看看。

2016-04-07 16:52:22 0

0 QuartusII_使用手册,又需要的朋友下来看看

2016-05-19 15:16:15 0

0 基于TCO的计数器设计,快来下载学习啊

2016-07-04 14:01:58 5

5 基于TCO的时钟设计,快来下载学习啊

2016-07-04 14:01:58 9

9 本章主要介绍 QuartusII自带的信号分析工具 自带的信号分析工具 —SignalTap II 的使用方法,感兴趣的小伙伴们可以看一看。

2016-09-18 14:55:04 10

10 QuartusII使用教程

2017-08-26 17:58:57 5

5 The TSU101, TSU102, and TSU104 operational amplifiers offer an ultra low-power consumption of 580

2017-09-05 09:47:51 8

8 XDC中的I/O约束虽然形式简单,但整体思路和约束方法却与UCF大相径庭。加之FPGA的应用特性决定了其在接口上有多种构建和实现方式,所以从UCF到XDC的转换过程中,最具挑战的可以说便是本文将要

2017-11-17 19:01:00 6665

6665

的双端和K端网络可靠性研究基础上,提出了基于截断的路径约束方法;并根据该方法构造二元决策图BDD模型进行带约束的是端网络可靠性分析。该算法针对k端点对点信息流在一定时间延迟下完成传输问题,具有较强的实际意义。实例分析结果

2017-12-06 14:03:03 0

0 约束优化进化算法主要研究如何利用进化计算方法求解约束优化问题,是进化计算领城的一个重要研究课题.约束优化问题求解存在约束区域离散、等式约束、非线性约束等挑战,其问题的本质是,如何处理可行解与不可行

2017-12-28 11:45:49 0

0 电子发烧友网为你提供TI(ti)TSU5511相关产品参数、数据手册,更有TSU5511的引脚图、接线图、封装手册、中文资料、英文资料,TSU5511真值表,TSU5511管脚等资料,希望可以帮助到广大的电子工程师们。

2018-09-12 16:30:28

电子发烧友网为你提供TI(ti)TSU6721相关产品参数、数据手册,更有TSU6721的引脚图、接线图、封装手册、中文资料、英文资料,TSU6721真值表,TSU6721管脚等资料,希望可以帮助到广大的电子工程师们。

2018-09-12 17:18:07

电子发烧友网为你提供TI(ti)TSU6111A相关产品参数、数据手册,更有TSU6111A的引脚图、接线图、封装手册、中文资料、英文资料,TSU6111A真值表,TSU6111A管脚等资料,希望可以帮助到广大的电子工程师们。

2018-09-13 14:26:11

电子发烧友网为你提供TI(ti)TSU8111相关产品参数、数据手册,更有TSU8111的引脚图、接线图、封装手册、中文资料、英文资料,TSU8111真值表,TSU8111管脚等资料,希望可以帮助到广大的电子工程师们。

2018-10-16 11:19:15

本文档的主要内容详细介绍的是QuartusII原理图输入法基本应用 实验目的是1. 掌握输入编辑原理图文件的方法2. 掌握编译原理图文件的方法3. 掌握仿真原理图文件的方法理解QuartusII器件编辑的方法

2018-10-17 08:00:00 0

0 本文档的主要内容详细介绍的是QuartusII原理图输入法层次化设计实验

一、 实验目的1. 掌握原理图文件的设计方法2. 掌握调用模块设计原理图文件的方法3. 掌握原理图文件层次化设计的方法

2018-10-17 08:00:00 0

0 了解时序约束向导如何用于“完全”约束您的设计。

该向导遵循UltraFast设计方法,定义您的时钟,时钟交互,最后是您的输入和输出约束。

2018-11-29 06:47:00 2698

2698

本文档的主要内容详细介绍的是QuartusII软件操作示例资料免费下载。

2019-02-26 14:09:31 8

8 本文档的主要内容详细介绍的是QuartusII安装教程之QuartusII安装说明和硬件安装资料免费下载。

2019-03-27 17:12:50 11

11 DDR接口的约束稍许复杂,需要将上升沿和下降沿分别考虑和约束,以下以源同步接口为例,分别就Setup/Hold Based 方法和Skew Based方法举例。

2019-07-25 11:01:38 2457

2457

本文档的主要内容详细介绍的是Verilog HDL语言组合逻辑设计方法以及QuartusII软件的一些高级技巧。

2019-07-03 17:36:12 19

19 组合逻辑延迟和走线延迟。Tsu表示捕获寄存器建立时间要求。Th表示捕获寄存器保持时间要求。其中Tco、Tsu和Th是由FPGA的芯片工艺决定的。所以,我们所谓的时序约束,实际上就是对时钟延迟和Tdata做一定的要求或者干预,其中Tdata由组合逻辑(代码)及布局布线决定,这也决

2021-01-12 17:31:36 9

9 1. 片内的Tsu/Tco 是指前级触发器的Tco 和后级触发器的Tsu, 一般来说都是几百ps 级别的。 可以通过“List Paths”命令查看。这里的Tsu/Tco 主要由器件工艺决定, 工作时在受到温度,电压的影响略有变化。

2021-01-19 15:23:00 7

7 1. 片内的Tsu/Tco 是指前级触发器的Tco 和后级触发器的Tsu, 一般来说都是几百ps 级别的。 可以通过“List Paths”命令查看。这里的Tsu/Tco 主要由器件工艺决定, 工作时在受到温度,电压的影响略有变化。

2021-01-29 16:27:07 11

11 基于成对约束的聚类分析是半监督学习的一个重要研究方向。成对约束的数量已成为影响该类算法有效性的重要因素。然而,在现实应用中,成对约束的获取需要耗费大量的成本。因此,文中提出了一种基于安全性的成对约束

2021-05-10 16:05:42 2

2 上一篇文章介绍了SystemVerilog的各种随机化方法,本文将在其基础上引入SystemVerilog的随机约束方法(constraints)。通过使用随机约束,我们可以将随机限制在一定的空间内,有针对性地提高功能覆盖率。

2023-01-21 17:03:00 1519

1519 TCO Certified是当前针对信息技术产品的一项全方位的安全、环保和可持续性的认证方案。随着IT 产品日益频繁地更新换代,TCO 认证的规范也每三年进行一次更新。当前应用中的TCO认证规范

2023-03-03 16:34:30 3020

3020 示例中采用的是“硬约束”,因为定义在类中的约束与随机时指定的内嵌约束“矛盾”,所以导致约束解析器解析随机失败,即“硬约束”要求所有相关的约束条件不能互相矛盾,否则将会随机失败。

2023-03-15 16:56:58 2539

2539 今天介绍一下,如何在Vivado中添加时序约束,Vivado添加约束的方法有3种:xdc文件、时序约束向导(Constraints Wizard)、时序约束编辑器(Edit Timing Constraints )

2023-06-26 15:21:11 1847

1847

指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被稳定的打入触发器,Tsu就是指这个最小的稳定时间。对应图1的Tsu(Tsu:set up time)

2023-06-28 15:40:07 1534

1534

本文将详细介绍输出延时的概念、场景分类、约束参数获取方法以及约束方法

2023-07-11 17:12:50 1288

1288

上一篇文章《暗藏玄机的SV随机化》介绍了SystemVerilog的各种随机化方法,本文将在其基础上引入SystemVerilog的随机约束方法(constraints)。通过使用随机约束,我们可以将随机限制在一定的空间内,有针对性地提高功能覆盖率。

2023-09-24 12:15:30 396

396

正在加载...

电子发烧友App

电子发烧友App

评论