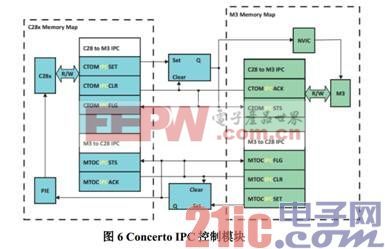

消息队列:开设两个消息队列,一个用于M4发送消息给M0,另一个则是M0发送消息给M4.两个队列的地址需事先约定好。队列是循环队列,可以使用简单的数组配以读、写下标来实现,也可以使用链表结构来实现。前者实现简单、开销小,但消息只能是定长,不便于携带其它信息,还有,就是必须把数组放置在共享内存区连续的位置,灵活性低。基于链表的实现用指针链接每则消息,每则消息除了公共的链表控制部分外,还可以根据消息类别携带各种各样的附加参数,并且可以由系统软件的内存管理机制灵活分配消息内存,不过,缺点是相对复杂,额外开销大。若涉及动态内存管理,实时性将远不如基于数组的方案。

消息队列有一个缺点,就是消息的串行化处理,它没有优先级的概念。但实际上,我们有实时操作系统(RTOS)及嵌套中断机制的支持,本应实现消息的并发处理。

消息池:消息池在存储结构上其实是简化的基于数组的消息队列--去掉了队列的读、写下标记录器。池中每个元素是一个消息,并且有一个字节指示每个元素的状态--空闲/已处理、新、半处理。当发送方写入消息时,扫描数组以查找空闲位置;当接收方读取消息时,也是扫描数组以查找状态。可见,消息池是基于优先级来处理消息的--小下标的元素优先得到处理。

消息池的可扫描性实现了消息的并发处理,并且可以通过中断上下文和任务上下文分两次"反刍式"处理。在处理消息池的中断服务例程中,先扫描各消息完成第一次处理,执行消息中(如果有的话)对实时性要求较高的部分。如果系统中没有使用RTOS,可以在后台的主循环中,再接下来二次扫描消息池,以完成第二次处理。对于使用了RTOS的系统,可以根据消息的优先级,创建或激活不同优先级的任务,使消息"附身"在这些任务的上下文中得到第二次处理。

消息池的一大缺点就是不宜支持较大数目的待处理消息。如有需要,可以给每则消息添加链表控制字段,我们可以把同一优先级的消息链成一串,从而彻底消除这一局限。

若干重要的细节

内核互斥:伪并行的多任务之间需要互斥访问共享资源,真并行的内核之间更是如此。尤其关键的是,一个内核无法关闭另一个内核的中断,因此还无法通过关中断临界区来保护。唯一能保证的,就是不会出现两个内核同时存取相同的地址。另外,由于架构上的局限,无法使用"自旋锁"来互斥。为此,我们可以通过施加一些编程准则来实现互斥。最简易有效的方法,就是在相同地址上给每个内核分别设置"只读"或"只写"的权限,或者是有条件的读写权限。比如,对于消息队列的读位置,只有接收方可以写,而发送方只能读取来判断队列是否空/满。又如,对于消息池,尽管发送方和接收方对池中的元素状态均可读可写,但有如下的条件:发送方只能把空闲状态改为非空闲;接收方只能把各种非空闲的状态改为空闲。再如,对于链表结构,可以只允许发送方更新各种指针;接收方通过更改链表中元素的状态和触发中断,以指示发送方更新各指针的时机。

内核鉴别:M4向下兼容M0,这使我们可以重用很多的源代码。但是,有时需要鉴别当前正在哪个内核上运行。这有两种方法,分别用于不同场合:如果在编译期间鉴别即可,则可以在编译器设置中,预定义诸如"CORE_M4"和"CORE_M0"的宏,使用C/C++的条件编译来处理;若需要在运行期间区分,可以读取一个名为"CPUID"的寄存器,根据CPUID的值来判定是M4还是M0.

初始化与可执行映像:LPC4350在完成上电复位后,M4开始执行代码,而M0却一直保持在复位状态。这样,我们也可以无视M0的存在,而只按单核MCU来使用。为使用M0,需要让M4为M0准备好开始执行的全部环境,包括寄存器上下文与地址空间等,然后释放M0.当M0处在复位状态时,我们可以通过JTAG发现M0,但是却无法操作它。因此,如果要调试M0的程序,需要先给M4下载适当的映像,使其释放M0才可,不可能在拿到一个空白的芯片后,直接先从M0动手。

尽管M4与M0各有自己的映像,但是我们可以把M0的映像内含于M4的映像中,这样在生产时只需要烧写一次闪存。为了并入M0的映像,工具链通常会提供把映像转换成C数组定义格式的功能。通过这个功能,我们把M0的映像转换成一个C数组的表格,并且把它和M4的源文件一同编译连接,这样一来,M0的映像就嵌入到M4的映像中了。M4在初始化期间,要把M0的映像拷贝到准备让M0执行的位置。由于M0固定从零地址开始取向量,M4还需要设置M0的地址映射,把映像的首地址设置成为M0的零地址。

值得一提的是,这种"主控带动协控"的设计哲学,也是被AMP普遍采用的。

调试时的细节:当我们使用调试仿真器连接MCU时,通常都会产生复位信号,但范围可仅限于内核,也可复位全片。在调试M0时,需设置复位范围仅包括M0,避免殃及正在运行的M4.另外,也需要编写适当的调试初始化脚本,以准备好内核的执行环境。这些工作繁琐,但具有高度的通用性,我们可以借鉴现有的脚本。

我们可以同时调试M4和M0:只需运行两个独立的IDE进程,分别打开相应的工程即可。经实践,至少在MDK+ULINK下可行。

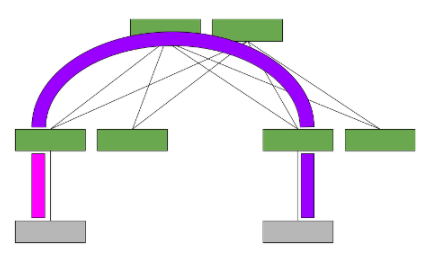

核间任务分工

M0没有M4强大的处理能力,但是作为一个CPU,亦有完整的中断系统和基本的算术与数据传送能力,并且在LPC4350上,可以在高达204MHz的主频下运行。合理地分担一些任务给M0,才能利用双核设计的优势。接下来,我们讨论两种主要的任务分工模型。

处理高频中断--智能"DMA":中断的响应是有额外开销的:既包括CPU的中断模型本身产生的硬件开销,也包括操作系统的中断管理产生的软件开销,当然,也还有中断服务程序本身执行的开销。当中断的频率很高时(比如:高达几十甚至几百kHz),中断的响应将对CPU时间产生不可忽略的额外开销。更重要的是,中断的响应是由硬件处理,并凌驾于任务管理之上的,这可以影响任何任务的执行而不论其优先级如何。DMA明显改善了这一状况。但是当DMA通道或总线分配不足,或者是设备不受DMA支持时,我们就可以让M0来响应这些高频的中断,合理组织数据缓冲区,而如同一个智能的DMA一样。

例如:在调光设备中,需要进行多达几十甚至上百路的AD采样来获取每路灯光的预期亮度,以及同样多的LED来指示实际输出的亮度。后者需要非常多的PWM,极可能已超出硬件PWM通道的数目。因此,在实现AD采样与软件PWM时,均需要快速的通道数据流处理与高频LED刷新,以保证PWM精度。这两者很容易导致高达几十kHz的中断请求,仅中断响应的额外开销就可占用一半以上的CPU时间。传统的做法是使用若干颗MCU来分摊并由主控轮询。在LPC4350下,则可由M0来处理这些任务。同样的例子也适用于PLC应用,它需要快速地刷新多路控制。

为弱计算操作提供额外的处理能力:M0的整体性能约是M4的72%,但对于弱计算操作(如:加减乘与逻辑运算,移位,以及简单的数据传送),并没有太多劣势。弱计算操作在程序中往往占一半以上的比例,尤其体现在驱动程序及一些通信协议栈上。合理地分配一部分弱计算操作任务给M0,可以有效提升整体的处理能力。这样,完成相同的任务只需更低的主频,而降低功耗,或者反过来,能够在有限的主频下完成需求更大的任务。

例如:在高精密工业运动控制中,对于电机的控制往往需要运算量很大的算法,同时又要处理如CAN、工业以太网,以及各种现场总线的通信。我们可以让M4来运行电机控制算法,而通信协议栈与驱动程序则由M0来完成。同样的例子也适用于嵌入式音频--由M4执行音频编解码与音效处理算法,而M0则负责音频总线、USB等事务。

本文小结

通过以上的介绍可以看出,相比传统的使用多颗MCU的方案,非对称双核MCU在性能、成本、功耗、生产等诸多环节都有明显的优势。核间通信稍显复杂,但作为基础设施可由底层系统软件来实现。在具体开发时,应根据实际问题合理分配任务,并且在初始化流程、内核鉴别以及调试上,需注意一些操作细节。

电子发烧友App

电子发烧友App

评论