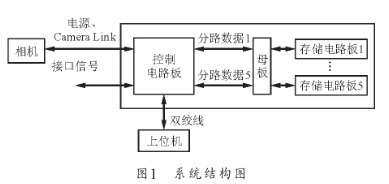

为了在嵌入式系统设计中实现对SDRAM存储器的访问,本文提出了一种基于AMBA-AHB总线规范的SDRAM控制器设计方案。方案首先简要介绍了AMBA总线规范,然后在完成整个存储控制器的整体框架

2014-01-02 13:59:42 4099

4099

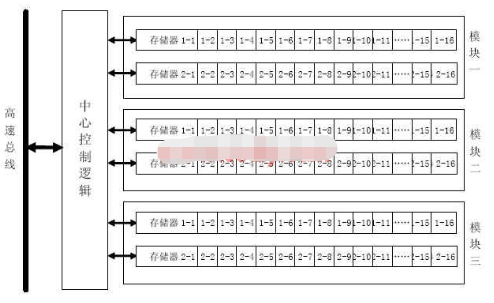

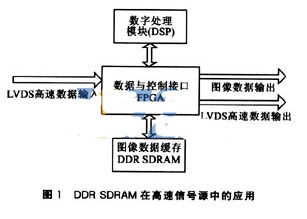

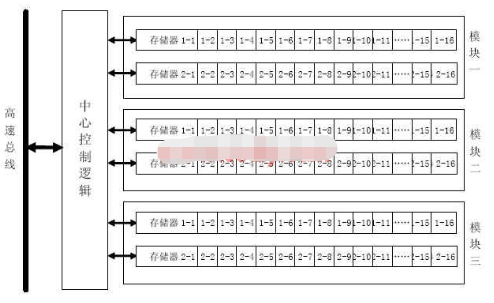

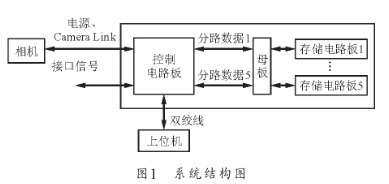

本文介绍了一种以FPGA作为控制器,FLASH MEMORY作为主存储器的大容量高速存储系统方案,并对关键技术及实现途径进行了论述,在存储容量及存储速度上实现了突破。

2020-07-30 17:53:54 1917

1917

的速度是480Mbits/s,完全可以满足图像采集、传输以及后续处理的要求。系统中采用 DSP+CPLD的硬件设计方案,采用现场可编程芯片 CPLD及两片 SRAM构成的图像采集和存储系统,可以根据

2019-06-20 07:31:29

是480Mbits/s,完全可以满足图像采集、传输以及后续处理的要求。系统中采用 DSP+CPLD的硬件设计方案,采用现场可编程芯片 CPLD及两片 SRAM构成的图像采集和存储系统,可以根据

2019-07-26 07:16:41

描述此参考设计演示了如何实现 SDRAM 存储器并通过接口连接到高性能微控制器 TM4C129XNCZAD。为了实现此设计,其中采用了该微控制器的 EPI 接口来连接 256Mbit SDRAM

2018-08-30 09:31:51

文章目录存储系统的层次结构技术指标层次结构局部性原理主存储器读写存储器只读存储器存储器地址译码主存空间分配高速缓冲存储器工作原理地址映射替换算法写入策略80486的L1 CachePentium

2021-07-29 09:47:21

存储系统的层次结构是怎样的?怎么解决容量/速度和价格矛盾的问题?

2021-11-02 09:22:03

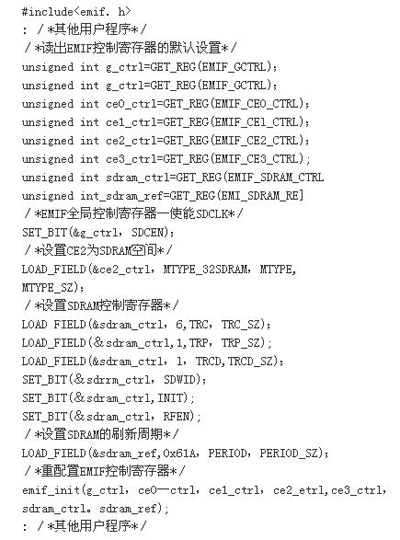

DSP有限的片内存储器容量往往使得设计人员感到捉襟见肘,特别是在数字图像处理、语音处理等应用场合,需要有高速大容量存储空间的强力支持。因此,需要外接存储器来扩展DSP的存储空间。

2019-11-06 06:00:41

高速SDRAM存储器接口电路设计SDRAM可作为软嵌入式系统的(NIOSII)的程序运行空间,或者作为大量数据的缓冲区。SDRAM是通用的存储设备,只要容量和数据位宽相同,不同公司生产的芯片都是兼容

2019-06-03 05:00:07

子系统的性能要求和设计方案的基础上,提出了高速缓存和海量缓存方案,并将该方案成功地应用于DSP多通道超声信号采集与处理系统中。 对高速多通道采样数据存储的性能要求:一是高速性,现在高速数据采集

2020-12-04 15:59:14

MMU。而一些复杂的系统可能包含一种或多种下面提到的技术,从而提供功能更为强大的存储系统。(1)系统中可能包含多种类型的存储器件,一般都有Flash、SRAM、SDRAM等接口。(2)使用指令/数据

2022-04-20 09:23:59

ESP32存储系统分为几部分呢?SPI flash的操作方法是怎样的?

2022-01-14 07:11:32

在DSP应用系统中,需要大量外扩存储器的情况经常遇到。例如,在数码相机和摄像机中,为了将现场拍摄的诸多图片或图像暂存下来,需要将 DSP 处理后的数据转移到外存中以备后用。从目前的存储器市场看

2020-04-23 08:00:00

该行业非常重视单个ECC代码的强度:但经常被忽视的是错误预防的强度,这在纠正甚至发挥作用之前是重要的我们如何在基于NAND闪存的系统中实现最低的故障率?您可能已在工程团队或存储系统供应商之间进行过

2019-08-01 07:09:53

“芯海杯”参考设计方案——计价秤计价秤,又可以称作电子计价秤是采用高精度称重传感器和八位单片微处理机,具备迅速称重计价的功能,操作方便,性能稳定,采用防水键盘,密封性好,手感舒适,尤其适用于水产品

2014-01-09 15:22:07

数据进行读入DSP的缓冲区以及将读取的数据进行数字滤波处理,然后将数据传递给上位机系统进行分析。另外考虑到DSP内存的不足,防止数据的丢失,特别为DSP外扩了SDRAM存储器和FLASH存储

2015-11-06 10:01:48

对数据采集与处理系统提出了新的更高的要求,即高速度、高精度和高实时性。对数据采集与处理系统的设计,有以下3种方案可供选择:(1)A/D+DSP方案在传统的高速信号处理中,大多采用这种方案。将A/D、D

2019-07-05 06:41:27

到底什么是云存储?云存储系统的结构是如何构成的?云存储有哪些技术前提?

2021-06-02 06:27:45

求大佬分享一款不错的基于FPGA超高速雷达住处实时采集存储系统

2021-04-15 06:56:25

DM642本身内存用于视频处理时远远不够,需要外扩存储器。一个SDRAM是32位的,我查看资料都是选用两片SDRAM扩展成64位的,与DSP的EMIF连接。我想问只用一片SDRAM不扩展成64位

2020-08-14 10:04:52

外部设备接口设计本系统通过公用总线连接的存储器资源有:4个扩展应用的SDRAM,2个FLASH,2对扩展应用的FIFO,以及DSP片内存储器资源。所有存储器资源都通过统一的地址空间映射来进行区分

2019-05-21 05:00:19

设计高温环境下(最高120°)基于FPGA的数据采集存储系统,就是通过传感器采集数据,通过FPGA来控制,把数据存储到存储芯片上,回头可以通过接口读取数据显示在计算机上,求大师给我指导,我急需整个系统的protel原理图,请各位帮忙,我将感激不尽。最好有附件画出整个原理图,谢谢!

2012-10-29 21:37:12

基于KeyStone架构的DSP电源设计方案电源硬件电路设计与计算

2021-02-04 06:48:30

针对航天测试系统的应用需求,利用FPGA的设计微型数字存储系统势在必行,那我们具体该怎么做呢?

2019-08-01 08:14:33

的高速SATA驱动器,1TB空间用来存储原始数据。设备买齐了,下面该动手安装了。首先,分别设定一个系统驱动器和一个数据驱动器。为了保证大影音文件运行时磁盘性能,剩余的两个驱动器设置为RAID 0.然后

2012-12-12 15:56:32

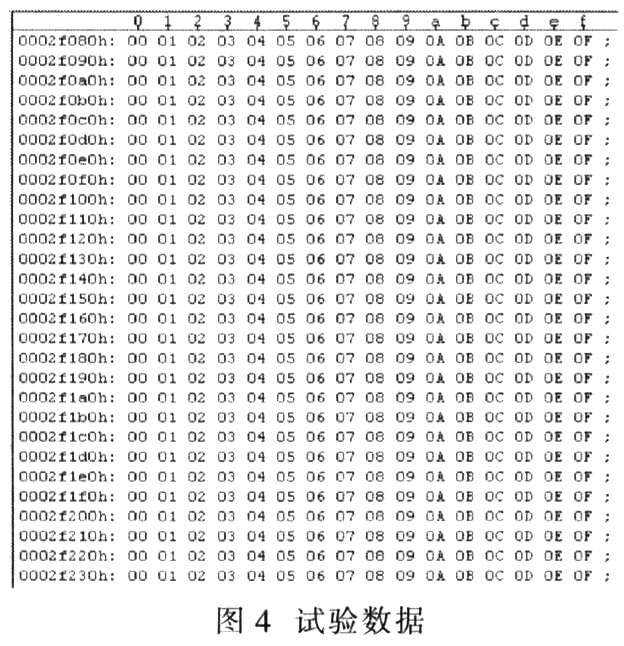

如何去设计微型数字存储系统的硬件部分?如何去设计微型数字存储系统的软件部分?

2021-05-13 07:22:46

如何设计一个基于PC主机北桥的长时间不间断高速采集和存储的系统。本文最后介绍了利用PC主机、PCI-E接口芯片PEX8311、Switch芯片PEX8616和RAID磁盘阵列卡,构建一个 的实时海量存储系统的案例。

2021-04-15 06:32:11

DSP有限的片内存储器容量往往使得设计人员感到捉襟见肘,特别是在数字图像处理、语音处理等应用场合,需要有高速大容量存储空间的强力支持。因此,需要外接存储器来扩展DSP的存储空间。

2019-10-29 07:13:51

DSP有限的片内存储器容量往往使得设计人员感到捉襟见肘,特别是在数字图像处理、语音处理等应用场合,需要有高速大容量存储空间的强力支持。因此,需要外接存储器来扩展DSP的存储空间。

2019-09-17 08:10:49

PXA27x系列的高端处理器,Intel并没有对SDRAM部分做本质上的改动,仍然是4根动态片选信号,故硬件方面的设计可以完全移植到PXA27x系列的处理器中。3 软件设计方案Windows CE操作系统下对内

2020-08-12 00:00:00

、卫星、无线电、光电、激光等高频物理信号),因试验、监测及装备的需要,对于原始信号的长时间捕捉与存储需求也日益增强。做为实现这些需求的手段,一般搭建一套高速数据采集存储系统是比较常规的方式。坤驰科技做为

2019-07-04 06:08:14

本文在FAST-40 SCSI协议基础上,对实时高速数字视频SCSI存储系统的软硬件进行了设计。

2021-06-07 06:32:21

本文提出了基于SOPC(System On Programmable Chip)的设计方案[2],利 用其配置灵活、扩展性强、接口丰富等优点,以Altera 公司的Cyclone II 系列FPGA 为基 础,设计传感器节点数据采集存储系统,降低了设计的风险,完善了传感器节点功能要求。

2021-05-06 08:28:58

怎么实现基于VW2010的视频存储系统的设计?

2021-06-03 07:14:51

是480Mbits/s,完全可以满足图像采集、传输以及后续处理的要求。系统中采用DSP+CPLD的硬件设计方案,采用现场可编程芯片 CPLD及两片SRAM构成的图像采集和存储系统,可以根据不同的需要进行现场编程

2019-09-18 08:31:58

够这些“冷数据”能够内储存到低成本、低能耗的媒介上,因而松下联开发了一种基于freeze ray技术的光盘存储系统。另据外媒报道称,该光盘存储系统是松下秘密与全球最大社交网平台Facebook历时

2016-01-06 18:23:32

本文提出的DSP控制多片DDC芯片的接口设计方案,对于4路A/D转换后的高速信号,分别通过DDC进行下变频和多级抽取滤波。

2021-04-20 06:20:27

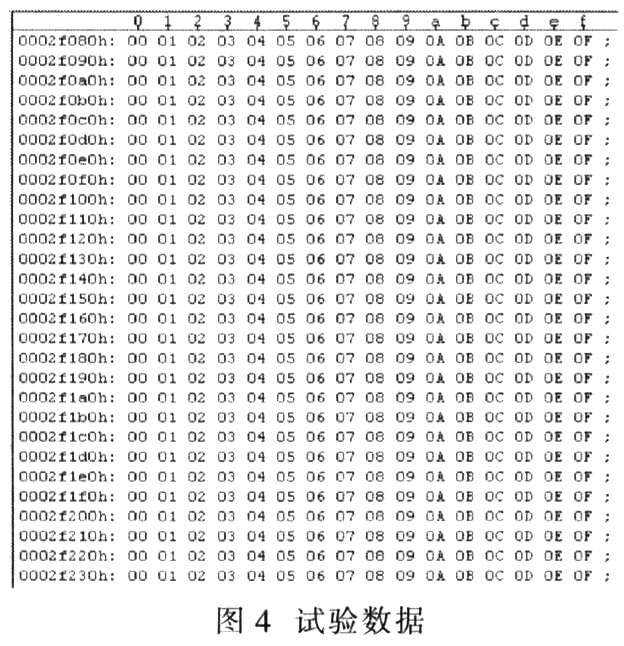

微型数字存储系统的硬件设计微型数字存储系统的软件设计怎样对微型数字存储系统进行验证?

2021-04-29 06:26:29

我在做一个FPGA的片外SDRAM读写功能的开发,参考了特权老师的verilog代码。背景:片外SDRAM采用的是HY57V561620FT-HI,模块当中利用100K时钟产生数据流,利用20M时钟

2018-04-24 10:38:29

【作者】:张益;霍珊珊;【来源】:《清华大学学报(自然科学版)》2009年S2期【摘要】:针对当前网络存储系统可生存性评估缺乏系统的评估指标和量化评估方法的现状,提出了量化评估指标体系和基于多指标

2010-04-24 09:43:16

内存,写这部分主要是为了和从片外 SDRAN 申请内存进行对比。选择以开发板创建工程后,选择 STM32F429-ATK-APOLLO 开发板,工程创建后默认是没有开启片外的 SDRAM 的,此时工程中

2022-05-11 14:45:46

语音压缩,存储与回放工程设计方案一、 设计要求与目标(1)使用DSP实现语音压缩和解压缩的基本算法,算法类型自定,例如可以采用G.711、G.729等语音压缩算法。(2)采用A/D

2009-12-09 15:37:01

想把程序从片内FLASH启动,将片外NOR FLASH中的应用加载到片外SDRAM中,然后跳转到片外SDRAM程序地址执行,可总是跳转不成功?有哪位做过类似的项目,敬请指教。

2019-03-22 07:19:07

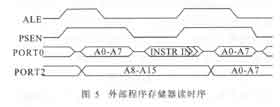

首先提出了一个通用DSP系统的设计方案,主要给出了FPGA在系统中的位置和作用。然后简要介绍了FPGA的各个功能模块,着重针对DSP和SDRAM接口进行了讨论,针对数据宽度和时钟速率不匹配的特点,提出双状态机

2019-05-17 07:00:13

论述了一种以Berkeley DB 为数据库内核的嵌入式流媒体存储系统的设计方案,该系统以改进的dosFs 文件系统为底层物理存储引擎,通过数据库为应用程序提供数据存取接口,确保了

2009-05-26 15:13:36 31

31 提出了一种基于DSP 的高速数据采集系统的设计方案,对其中高速A/D、高速缓存。DSP 控制以及数据通讯接口等内容进行了讨论,提出了更为有效的同步控制方式。该设计方案电路

2009-06-12 16:37:58 17

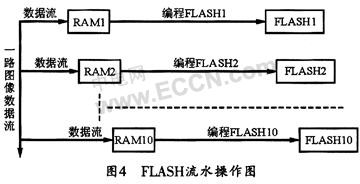

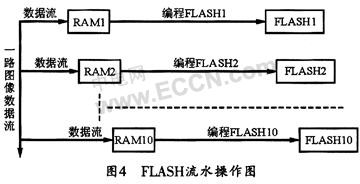

17 针对硬盘存储图像速度慢、可靠性差的弊端,分析了以Flash作为存储介质的可行性,提出了一种基于闪存Flash的存储系统设计方案.利用并行与流水线技术相结合,有效提高了存储容量和

2010-12-15 14:51:40 49

49 模数转换是数字信号处理的重要前提和关键环节,设计了基于TMS320C6416T型DSP和THS12082型A/D转换器的数据采集存储系统。实验表明,该高速数据采集存储系统具有高速的DSP特性,可广泛

2010-12-22 16:41:47 14

14 基于DSP的数字存储示波器显示控制系统的设计

一种基于DSP的数字存储示波器显示控制系统的设计方案。该系统主要由主机接口电路、数据处理电路及显示

2008-12-03 20:50:44 678

678

基于FPGA的微型数字存储系统设计

1 引言 针对航天测试系统的应用需求,提出一种基于FPGA的微型数字存储系统设计方案。该系统是在传统存储测试系统的基

2009-11-04 10:46:38 716

716

浅析嵌入式存储系统设计方法

嵌入式存储系统由嵌入式硬件和固化在硬件平台中的嵌入式存储系统软件组成。传统的小规模嵌入式存储系统,软件多采用前后台的方

2010-01-26 16:32:14 930

930

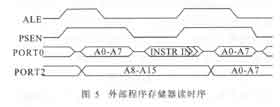

高速大容量存储系统设计

0 引言在测量技术中,高速数字摄像机所拍摄到的大量数字图像需要高速、大容量的图像存储设备来实时快速地存储。用传统的磁带

2010-03-08 16:23:02 979

979

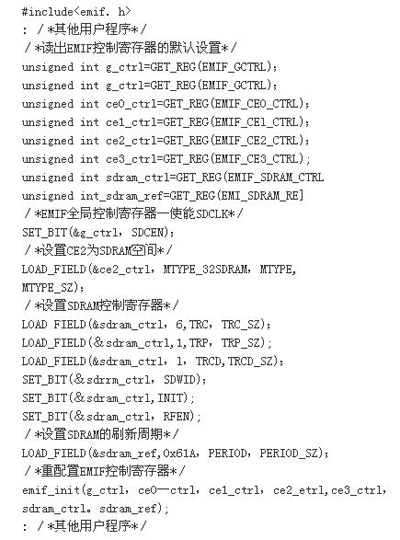

在数字图像处理、航空航天等高速信号处理应用场合,需要有高速大容量存储空间的强力支持,来满足系统对海量数据吞吐的要求。通过使用大容量同步动态RAM(SDRAM)来扩展嵌入式DSP

2010-07-14 10:02:31 857

857

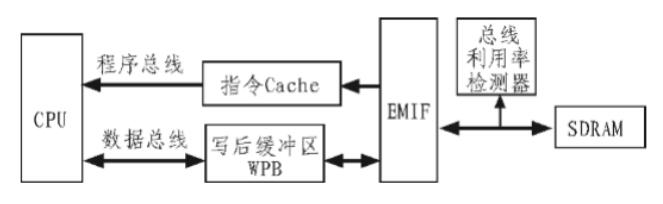

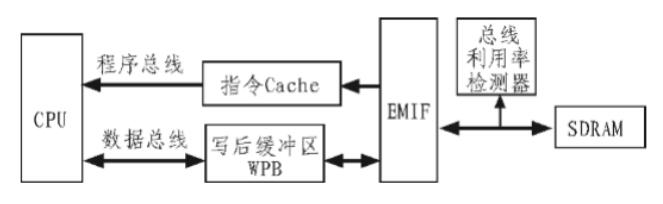

为了降低DSP外部SDRAM存储系统的功耗,针对DSP访问片外SDRAM的功耗来源特点,提出了基于总线利用率动态监测的读写归并方案。该方案动态监测外部存储器接口(EMIF)总线的利用率,根据总线利用率的不同选择开放的页策略、封闭的页策略或休眠模式;设计了简化

2011-01-14 17:40:12 50

50 分析当前网络存储系统存在的问题,给出一种基于企业卷管理系统技术的带外虚拟网络存储系统基本结构。分别阐述该存储系统的客户端、内部数据的读/写操作、存储系统在线存储容量

2011-05-18 18:50:31 38

38 SDRAM 以其高速和大容量的优点获得了极大的应用,但是其接口与目前广泛应用的微处理器系统不兼容,介绍了用 VHDL 语言实现的SDRAM与RAM之间的接口控制电路,从而将SDRAM应用到微处理器

2011-06-01 15:29:15 57

57 本内容详细介绍了高速数据采集与存储系统技术方案

2011-07-07 17:43:53 69

69 超高帧频实时图像的长序列采集存储一直是难于解决的问题。本文基于SCSI 总线的理论体系,提出一种新的图像数据采集存储系统的技术方案和体系结构,并设计出一种超高速、数字化

2011-07-18 16:02:43 31

31 本文利用“FPGA+单片机”作为存储控制器,采用基于LZW算法的数据压缩技术,以SDRAM作为周期存储和缓存,SD卡作为最终存储载体,实现车载CAN总线记录仪实现大容量存储系统。

2011-09-08 16:24:59 2170

2170

:针对当前网络存储技术存在的存储服务瓶颐问题,介绍了一种高可靠可扩展PC集群存储系统的设计方案,并提出了对各个存储结.点所挂磁盘的分组方案,对大小数据对象分别采用不同的

2011-09-21 16:50:00 0

0 为解决现有采集存储系统不能同时满足高速率采集,大容量脱机且长时间持续存储的问题,设计了一种基于SATA硬盘和FPGA的数据采集和存储方案。本设计由AD9627转换芯片,Altera Cyclone系列

2011-11-15 11:35:19 169

169 高速图像存储系统中SDRAM控制器的实现

2016-08-29 15:02:03 10

10 基于闪存的图像存储系统设计,又需要的下来看看

2016-09-22 14:08:55 13

13 NetApp_E5600_存储系统

2016-12-28 09:33:36 0

0 NetApp_E5500_存储系统

2016-12-28 09:33:36 0

0 NetApp_E2700_存储系统

2016-12-29 12:01:01 0

0 本文中介绍的故障恢复主要是只单机存储系统中的故障恢复,就是只有一台电脑,与之相对的是分布式存储系统,暂且不谈。

2018-06-10 01:41:00 777

777 在数字图像处理、航空航天等高速信号处理应用场合,需要有高速大容量存储空间的强力支持,来满足系统对海量数据吞吐的要求。通过使用大容量同步动态RAM(SDRAM)来扩展嵌入式DSP系统存储空间的方法

2017-10-23 10:48:11 1

1 Tera-Store高速数据采集存储系统

2017-10-24 09:28:41 4

4 数字图象处理技术在电子通信与信息处理领域得到了广泛的应用,设计一种功能灵活、使用方便、便于嵌入到系统中的视频信号采集电路具有重要的实用意义。 在研究基于DSP的视频监控系统时,考虑到高速实时处理

2017-10-29 10:46:44 0

0 针对某系统图像数据量大、传输速率快的特点,提出了采用PCI总线协议完成PC与高速数据存储系统之间的通信,利用LVDS总线协议传输数据并进行混合编帧的解决方案。为提高数据存储速率,使用Flash交叉

2017-11-18 05:26:03 3788

3788

DRAM (动态随机访问存储器)对设计人员特别具有吸引力,因为它提供了广泛的性能,用于各种计算机和嵌入式系统的存储系统设计中。本文概括阐述了DRAM 的概念,及介绍了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、LPDDR、GDDR。

2018-06-07 22:10:00 91644

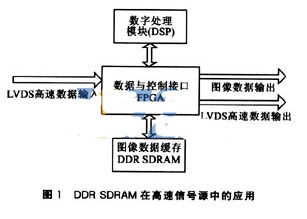

91644 很多嵌入式系统,特别是应用于图像处理与高速数据采集等场合的嵌入式系统,都需要高速缓存大量的数据。DDR(Double Data Rate,双数据速率)SDRAM由于其速度快、容量大,而且价格便宜

2019-07-02 08:03:00 4051

4051

说一说AI技术在存储中的应用,和对存储系统带来的创新性改进。

2018-10-24 15:41:58 4084

4084 设计了以FPGA器件XCSVIXS0为核心处理芯片的高速数据采集存储系统。在XCSVLXS0内部实现的高速状态机和相位延迟时钟作用下,采用4片高速A/D器件流水工作来提高数据采集速度。同时

2018-12-10 16:47:01 22

22 ,所以不利于数据的长时间保存。而近几年问世的闪存以其存储容量大、体积小、可靠性高等优点,逐步向存储系统进军。

2020-07-21 17:45:20 1003

1003

为了降低DSP外部SDRAM存储系统的功耗,针对DSP访问片外SDRAM的功耗来源特点,提出了基于总线利用率动态监测的读写归并方案。该方案动态监测外部存储器接口(EMIF)总线的利用率,根据总线

2020-12-02 15:50:52 715

715

SDRAM作为大容量存储器在高速图像处理中具有很大的应用价值。但由于SDRAM的结构和SRAM不同,其控制比较复杂。文章详细介绍了 SDRAM存储器的结构、接口信号和操作方法,以及 SDRAM控制器

2021-01-26 15:30:52 13

13 针对硬盘存储图像速度慢、可靠性差的弊端,分析了以Flash作为存储介质的可行性,提出了一种基于闪存Flash的存储系统设计方案。利用并行与流水线技术相结合,有效提高了存储容量和操作速度。整个存储系统

2021-03-23 15:44:59 10

10 PACS-存储系统方案的选择(肇庆理士电源技术有限公司规模人数)-该文档为PACS-存储系统方案的选择讲解文档,是一份不错的参考资料,感兴趣的可以下载看看,,,,,,,,,,,,,,,,,

2021-09-23 10:05:09 10

10

正在加载...

电子发烧友App

电子发烧友App

评论