在数字电路设计中(Verilog or VHDL),ModelSim是常用的仿真工具。当我们仿真大型的工程时,往往需要保留仿真波形,以便分析和以后查看。这就需要学习在ModelSim里面如何保存仿真波形及调用波形。

为了方便以后察看仿真结果,可以将仿真波形保存在.Wlf文件中:

一。保存过程:

1.完成仿真波形

2.切换到sim视窗

3.点击保存图标,可以直接保存为.wlf文件

二。打开过程

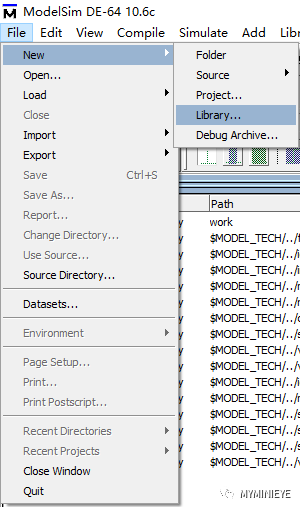

1.打开modelsim

2 file菜单打开.wlf文件(要在文件类型中选择.wlf类型)

3.确定之后出现sim视窗

4.选中窗口中的测试文件名右击————add wave即可在wave窗口打开该测试坡形。

三。也可以将波形保存为.do文件

do文件记录了仿真的过程和加载的各种库。

do文件的保存过程:

file——》save format——》D:/modeltech_6.5b/examples/wave.do 可以更改do文件名称和存放目录

2.do文件的加载:

file——》load(注意要在sim视窗下)。打开之后貌似只显示出仿真过程代码,没法显示波形。

modelsim保存仿真结果,以及打开保存的仿真结果的波形wlf文件(经过实验,真实可用)

1、在wave界面,将仿真波形保存为 .do文件(信号列表文件)。

2、切换左边任务栏至“sim”,,点击保存,给将要保存的 .wlf文件(波形文件)命名为自己想要的名字,默认为vsim.wlf。

(wlf文件为modelsim的wave log file文件格式)

3、保存,OK,关闭modelsim(注意,必须关闭modelsim,否则打开wlf文件的时候,会提示未正常关闭,无法打开)。

4、重启modelsim,open 之前保存的 .wlf文件,然后 load 对应的 .do文件。

也可以使用命令行的格式打开此波形文件,举例如下:vsim -view wave.wlf -do run.do。

do文件记录了仿真的过程和加载的各种库。

do文件的保存过程:

file——》save format——》D:/modeltech_6.5b/examples/run_wave.do 可以更改do文件名称和存放目录,一般保存在仿真目录中。

2.在仿真路径中找到文件vsim.wlf打开,再命令窗口输入:do run_wave.do

具体操作:

1.打开modelsim se :切换目录到仿真工程下。

2.命令行输入:OpenFile vsim.wlf

3.命令行输入:do run_wave.do(上次保存的wave.do文件)

参考:

保留仿真后的波形,步骤如下:

1.点击file菜单下的save format,保存为.do格式文件

2.下次打开Modelsim后,在控制台输入do wave.do命令后,即可看到上次仿真的波形图

此外,点击向上箭头的按键可以重复输入上次命令。

怎么样保存仿真的完整波形(不是printScreen),File》export》image好象和截屏的功能一样,只能保存一部分波形,怎么样保存成modelsim认识的波形,下次看的时候只需要打开这个波形图,不需要重新仿真,这个在vcs中可以的,用vcd文件,好像modelsim也支持dump vcd的,不知道具体怎么做,怎样保存,怎么样打开?

使用“dataset save sim filename.wlf ”保存仿真波形,

filename.wlf文件的名字可以自己任意取。打开时候直接,open filename.wlf文件就可以了。

直接通过OPEN找到.WLF文件,打开就可以了。

保存wlf,下一次只要直接打开它就可以了。但是有这样的情况出现,如果在保存wlf前,你改动了某些信号的位置,下一次打开是会回到原先的位置,此时你可以把do文件一起保存,在下一次打开wlf文件后,再打开do文件,你先前的顺序就会回来

波形信号的保存:有时,在波形窗口内拖放了较多的信号,可以保存起来以后调入。在wave窗口,File -》 Save format,保存成*.do文件。以后需要调入时,在modelsim主窗口命令行内执行:do *.do即可

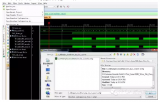

ModelSim中寄存器组值查看工具

在ModelSim中,当定义了寄存器数组(例如:reg [7:0] ram [0:127]),可以通过Memory List工具查看仿真时的值。步骤:

1.定义Reg类型,例如RAM

module ram_1024Byte

#(parameter DATA_WIDTH = 16, parameter ADDR_WIDTH = 8)

(

input [(DATA_WIDTH-1):0] data,

input [(ADDR_WIDTH-1):0] read_addr, write_addr,

input we, clk,

output reg [(DATA_WIDTH-1):0] q

);

// Declare the RAM variable

reg [DATA_WIDTH-1:0] ram[0:(2**ADDR_WIDTH-1)];

// Initiation

initial

begin

$readmemh(“。。/dev/ram_init.dat”, ram);

end

// Read and Write Operation

always @ (posedge clk)

begin

// Write

if (we)

ram[write_addr] 《= data;

// Read (if read_addr == write_addr, return OLD data)。 To return

// NEW data, use = (blocking write) rather than 《= (non-blocking write)

// in the write assignment. NOTE: NEW data may require extra bypass

// logic around the RAM.

q 《= ram[read_addr];

end

endmodule

2.仿真

新建工程-》编译-》仿真(without optimization)

View-》Memory List,便可以查看RAM中寄存器的值

电子发烧友App

电子发烧友App

评论