数据分配器

能够将1个输入数据,根据需要传送到m个输出端的任何一个输出端的电路,叫做数据分配器,又称为多路分配器,其逻辑功能正好与数据选择器相反。电路结构:由与门组成的阵列。分类:1路-4路数据分配器(如74LS139)、1路-8路数据分配器(74LS138)等。由于译码器和数据分配器的功能非常接近,所以译码器一个很重要的应用就是构成数据分配器。 也正因为如此,市场上没有集成数据分配器产品,只有集成译码器产品。

通过QuartusII软件进行编译后,仿真结果如图3-8所示;

译码器

译码器是一个多输入、多输出的组合逻辑电路。它的工作是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。译码器在数字系统中有广泛的用途,不仅用于代码的转换、终端的数字显示,还用于数字分配,存储器寻址和组合控制信号等。译码器可以分为通用译码器和显示译码器两大类。在电路中用的译码器是共阴极译码器74LS48,用74LS48把输入的8421BCD码ABCD译成七段输出a-g,再由七段数码管显示相应的数。

通过QuartusII软件进行编译后,仿真结果如图3-11所示;

分频器

分频器的作用是将由石英晶体产生的高频信号分频成基时钟脉冲信号和扩展部分所需的频率。在此电路中,分频器的功能主要有两个:一是产生标准脉冲信号;二是功能扩展电路所需的信号,如仿电台用的1KHz的高频信号和500Hz的低频信号等。可以组成二分频电路和四分频电路和十六分频器。

打包后成元器件如图3-12所示;

闹时器

数字钟在指定的时刻发出信号,或驱动音响电路“闹时”;或对某装置的电源进行接通或断开“控制”。不管是闹时还是控制,都要求时间准确,即信号的开始时刻与持续时间必须满足规定的要求。在这里将举例来说明它的工作原理。要求上午7时59分发出闹时信号,持续1分钟。设计如下:

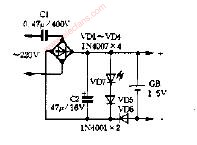

在电路图中用到了4输入二与非门74LS20,集电极开路的2输入四与非门74LS03,因OC门的输出端可以进行“线与”,使用时在它们的输出端与电源+5V端之间应接一电阻RL。RL的值由下式决定:

闹时器程序代码;

module nsdl(out,m1,m2,h1,h2,tenh,oneh,tenm,onem,clk1k,cin);

output out;

input[3:0] m1,m2,h1,h2,tenh,tenm,oneh,onem; input cin, clk1k;

reg out;

always @(m1 or m2 or h1 or h2 or tenh or tenm or oneh or onem or cin) begin

if(cin) out《=0; else if(cin==0) begin

if(tenh==h1&&oneh==h2&&tenm==m1&&onem==m2) out《=clk1k; else out《=0; end end

endmodule

打包后成元器件如图3-13所示;

报时器

(一)功能要求

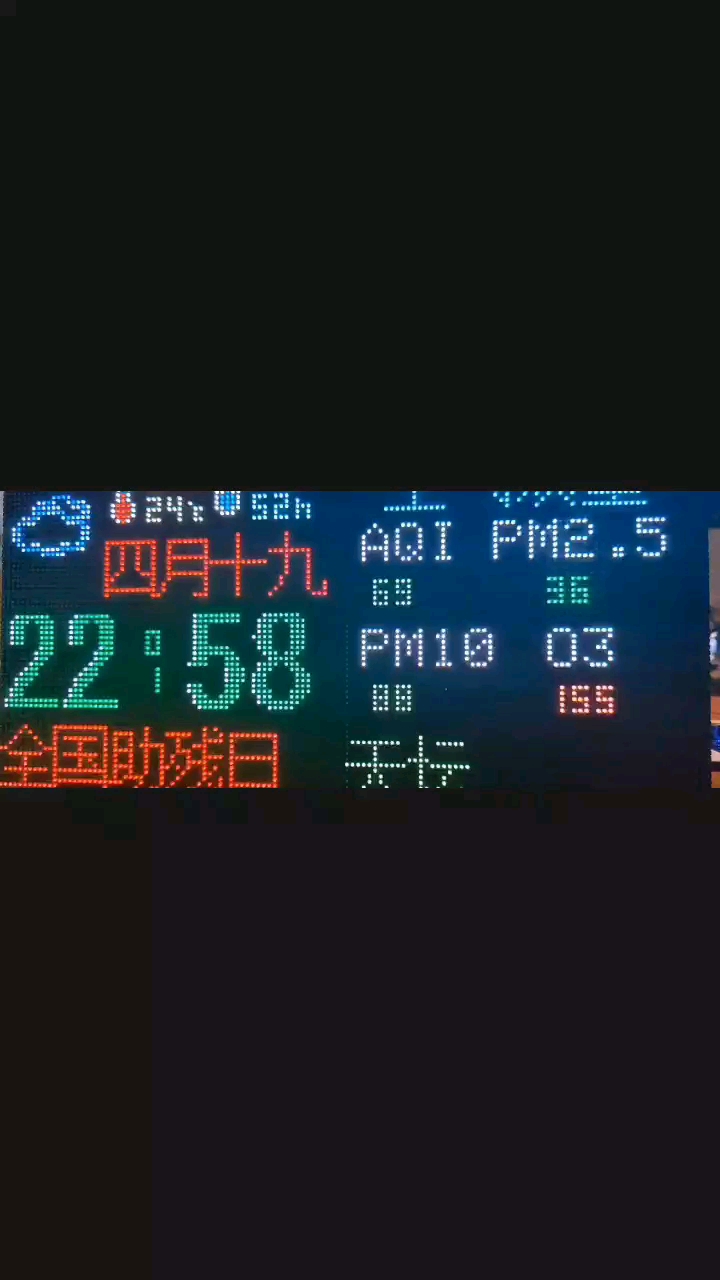

报时的功能要求是:每当数字钟计时快要到正点时,通常按照4低音1高音的顺序发出间断声响,以最后一声高音结束的时刻为正点时刻。

(二)该电路的工作原理

电路图的工作原理举例来说明;例如设4声低音(约500Hz)分别 在59分51秒、53秒、55秒及57秒,最后一声高音(约1000Hz)发生在59秒,它们的持续时间为1秒。只有当分十进位的Q2M2Q0M2=11,分个位的Q3M1Q0M1=11,秒十位的Q2S2Q0S2=11及秒个位的Q0S1=1时,音响电路才能工作。

(三)对该电路中使用的元件的介绍

因为在该电路中所用的元件主要是74LS00、74LS04及74LS20这些元件在前面的

电路中已经介绍。这里就不再介绍它了

报时器程序代码;

module baoshi(tenm,onem,tens,ones,q500,q1k,a,b); input a,b;

input [3:0]tenm,onem,tens,ones; output q500,q1k; reg q500,q1k;

always @(tenm or onem or tens or ones) begin

if ({tenm,onem}==8‘h59&&{tens,ones}==8’h50||{tenm,onem}==8‘h59&&{tens,ones}==8’h52|| {tenm,onem}==8‘h59&&{tens,ones}==8’h54||{tenm,onem}==8‘h59&&{tens,ones}==8’h56|| {tenm,onem}==8‘h59&&{tens,ones}==8’h58) q500《=a; else q500《=0; end

always @(tenm or onem or tens or ones) begin

if ((tenm[3:0]==0000&&onem[3:0]==0000)&&(tens[3:0]==0000&&ones[3:0]==0000)) q1k《=b; else q1k《=0; end

endmodule

打包后成元器件如图3-14所示;

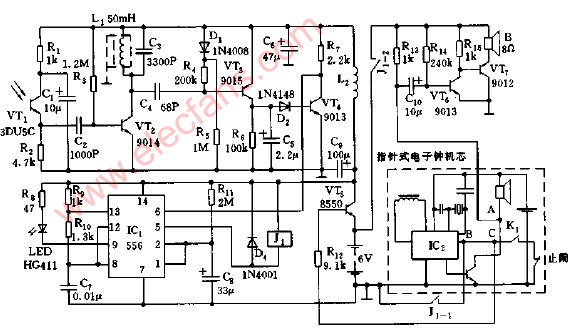

数字钟原理图

将各模块组合一起构成如图3-15所示:

软件调试的过程据功能的增加分为几步:

首先,根据原来的100进制显示程序的基础上编写成时分秒六位显示的主程序。该程序将时分秒分成个位和十位分别计算,所以将60进制和24进制变成10进制、6进制和2进制。又因为如果时十位为2的话,不能大于3,所以在分十位向时个位进位时得判断时十位是否为2,在组员的帮助下经过不断试验和修改终于完成。过程比较顺利。

该电子钟使用一个键来调时,利用长按来选择所要调的位,用短暂按下来对位进行加1,前提是时钟暂停,这个功能也是通过长按来实现的。选位是从秒个位到时十位依次选取,但到时十位以后就回不到秒个位了,就是不会循环。所以就得对选的位进行检查,如果到了时十位再按取位键就重新赋给秒个位地址。这样就可以循环选位了。但在后来的测试中又有了新的问题,如果该位到了9,对一个位进行加1调整就会显示乱码。时分秒的十位都会调到9!

对于这个问题费看一些周折。起先构思再加一个减一的键,但不但没有解决这个乱码问题而且减到了0一下很可能也会出现乱码。所以就转而寻求程序解决。调时的时候让它也像正常运行的时候进位?没见过这样的。继而决定在进行加1调时的时候检测该位是否到10或6或3。所以就产生了所谓的调时比较子程序,就是在调时的时候将该位跟10或6或3比较。最后,调试的时候却总是出现这样的情况:所调的位超过了9或5或2就变成乱码。比原来进步的地方就是时分秒的十位不用超过9就变成乱码。这说明虽然还没成功,但还是有前展的。就继续调试。

电子发烧友App

电子发烧友App

评论