摘要 介绍以Philips LPC3180微控制器为核心的嵌入式软硬件平台设计;对系统设计的硬件部分和软件部分进行详细的分析,并针对LPC3180芯片特性着重讨论了其软件系统构建以及系统启动流程。实验结果表明,LPC3180嵌入式系统平台结合片内硬件浮点运算单元,具有高性能的浮点运算处理能力,可满足复杂的嵌入式应用场合的要求。

关键词 LPC3180 ARM9 软硬件平台

嵌入式应用系统设计包括硬件平台和软件平台两部分。前者是以嵌入式微控制器/微处理器为核心的硬件系统;后者则是围绕嵌入式操作系统构建的软件系统。两者在设计上是密不可分的,并且需要在设计之间进行权衡优化,根据实际应用进行外扩和裁剪。

基于ARM926EJS内核的LPC3180内部集成了丰富的外设资源,为嵌入式系统构建提供了很大的设计空间。本文结合笔者开发LPC3180嵌入式平台的实际经验,将具体介绍该系统的实现、结构组成和实验结果。

1 LPC3180芯片特性介绍

LPC3180是Philips公司新推出的一款ARM9微控制器。它采用90 nm工艺技术,片内集成ARM9EJS处理器内核,具有高计算性能、低功耗的特性,这使得在很多对功耗敏感的嵌入式应用场合中仍能使用高性能的ARM9微控制器。LPC3180内核正常工作电压为1.2 V,在低功耗模式下可降至0.9 V;同时,LPC3180作为一款新型的32位微控制器,其新特性还包括:

◆ 片内集成向量浮点(VFP)协处理器。LPC3180的浮点运算单元有3条独立的流水线,支持并行单精度或双精度浮点加/减、乘/除以及乘累积运算,完全兼容IEEE754标准,适用于高速浮点运算场合。

◆ 片内集成USB OTG控制模块,同时支持与便携USB主设备或USB外设相连,可用于与PDA、读卡器和打印机等设备直接相连,而无需PC机介入。

◆ LPC3180采用多层的AHB总线系统,为各个主模块提供独立的总线,包括CPU的指令总线和数据总线、2套DMA控制器数据总线以及1套USB控制器数据总线。

LPC3180的内部架构如图1所示。

LPC3180的其他特性包括: 内部集成MLC/SLCNAND控制器、SDR/DDR SDRAM控制器、SD卡接口,UART、SPI、I2C外围通信模块,以及高速/毫秒定时器、RTC、看门狗定时器、10位ADC等其他功能模块。

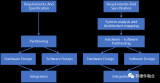

2 硬件平台设计

以LPC3180为核心的硬件平台设计框架如图2所示。

(1) 存储器系统

NAND Flash存储器。通过LPC3180内部集成的MLC/SLC NAND控制器直接外接多级或单级NAND Flash器件。本系统选用ST NAND256R3A,其32 MB存储空间可满足存放系统引导程序、嵌入式操作系统内核和文件系统的大小要求。

SDRAM存储器。系统选用2片16位MICRON SDRAM,并联构建32位SDRAM存储器系统。32 MB SDRAM空间,可满足嵌入式操作系统以及上层应用程序的运行要求。

SD卡插槽。系统通过LPC3180内部集成的SD卡接口,提供SD卡插槽,可用于SD存储卡外扩,作为外部存储空间。

(2) 外围通信接口

UART接口。LPC3180内部集成了标准UART模块和高速UART模块,符合550工业标准。系统外扩了UART1/7、UART2和UART5,用于实现基本的串行通信功能;同时,UART5可用于系统启动时的外部程序下载。

USB接口。LPC3180内部集成了USB host、USB device以及USB OTG控制器,通过外部USB收发模块Philips ISP1301外扩USB host接口A、USB device接口B以及USB OTG接口AB。

(3) 其他外围模块

系统通过I2C接口外扩了一个简易的字符型LCD显示模块,用于应用程序运行结果显示;同时,为了简化硬件系统设计,系统的以太网模块通过USB host接口A以软件方式实现外扩。

3 系统关键模块设计

3.1 NAND Flash存储器模块

LPC3180内部集成了MLC/SLC NAND控制器,通过外部引脚可直接外接多级或单级NAND Flash器件,如图3所示。需要注意的是MLC和SLC NAND控制器通过引脚复用,使用相同的接口与NAND Flash相连,且同一时刻只允许开启其中一个控制器,因此在系统上电后必须通过配置FLASH_CTRL寄存器选择要使用的NAND控制器。在闲置状态时,也可通过写寄存器关闭NAND控制器,以降低功耗。NAND Flash存储器模块是整个系统主要的静态数据存储空间,用于存储系统启动过程中的加载程序,因此在LPC3180系统设计中是必不可少的。

3.2 USB接口模块

LPC3180内部集成USB控制模块,但不包括USB物理层,系统通过外接USB收发模块ISP1301实现USB的物理层接口。图4是USB接口连接图。LPC3180内部通过AHB从设备总线配置USB控制器,可工作在全速(12 Mb/s)和低速(1.5 Mb/s)两种模式下。

4 软件系统设计

软件系统组成包括系统引导程序Bootloader,嵌入式操作系统以及上层应用程序。其中Bootloader是运行于操作系统之前的引导程序,主要任务是完成系统启动之前必要的硬件初始化和操作系统加载;操作系统是整个嵌入式平台的核心程序,主要功能是高效地管理和分配底层硬件资源,并为上层应用程序提供与硬件细节无关的系统调用接口。

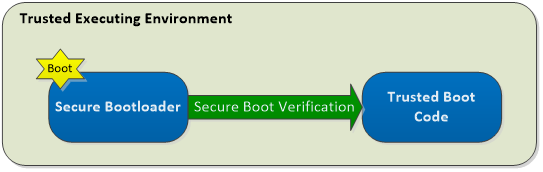

软件系统设计必须与硬件平台紧密结合。LPC3180采用NAND Flash作为整个系统的程序存储区域,在系统启动时通过片上ROM的bootstrap程序,从NAND Flash加载并执行外部引导程序来实现整个系统的启动步骤。因此,整个软件系统采取了图5所示的设计结构。

(1) 系统引导程序Bootloader

由于启动过程首先从片内的bootstrap程序开始,因此系统采取二级Bootloader设计,包括第一级Sibl和第二级U?boot。

其中Sibl是bootstrap加载并执行的第一个引导程序,在程序大小上受到bootstrap加载的限制,因此设计上尽量做到了小型化和功能专一。它除了完成最基本的硬件初始化以外,主要功能是实现其他程序(包括U?boot)从NAND Flash的加载,完成下一级Bootloader运行之前的内存地址空间分布。

第二级Bootloader采用功能强大的sourceforge开源软件U?boot。U?boot的主要功能是完成嵌入式操作系统启动前的底层硬件初始化,并为Linux内核提供启动参数,最终引导操作系统Linux内核启动。另外,为了实现程序镜像文件编程写入NAND Flash,U?boot嵌入了一个NAND子系统,通过U?boot的用户命令行实现对NAND Flash的读/写操作,可将程序镜像写入NAND Flash指定的地址空间。

(2) 嵌入式操作系统

LPC3180内部集成了ARM926EJS处理器内核,带存储器管理单元MMU,支持多数主流嵌入式操作系统。系统通过编写板级支持代码,移植了Linux2.6.10作为平台操作系统,利用稳定的Linux2.6内核实现任务调度、进程管理、内存管理等功能,同时,针对Linux的可配置性,对内核进行裁剪和硬件驱动代码添加,系统实现了一个小型但功能强大的内核程序,适应了嵌入式系统存储资源相对紧缺的状况。

5 系统启动流程分析

由上面的软件结构组成分析可知,整个系统启动流程分为3个步骤:

① 系统上电后,首先从片上ROM固化的bootstrap程序执行。bootstrap用于完成外部引导程序下载并跳入执行。bootstrap运行过程首先读输入引脚GPIO_01。如果GPIO_01置为高,则从NAND Flash下载程序引导系统启动;如果置为低,则依次检测USB接口和UART5接口,通过外部连接下载引导程序。系统通过设置GPIO_IO跳线来控制bootstrap启动过程,本例将GPIO_01置为高,从NAND Flash下载程序。

② 系统启动的第二阶段是运行bootstrap下载的引导程序Sibl。Sibl完成系统必要的初始化后,从NAND Flash加载镜像程序到指定的SDRAM空间。镜像程序在起始位置添加了64字节的头信息,用于Sibl识别和加载,头信息数据结构如下:

struct image_header {

uint32_tih_magic;/*镜像头信息同步字,Sibl通过该字识别程序*/

uint32_tih_hcrc;/*镜像头信息CRC校验码*/

uint32_tih_time;/*存储镜像创建时间*/

uint32_tih_size;/*镜像数据大小*/

uint32_tih_load;/*镜像加载地址*/

uint32_tih_ep;/*镜像入口地址*/

uint32_tih_dcrc;/*镜像数据CRC校验码*/

uint8_tih_os;/*操作系统信息*/

uint8_tih_arch;/*CPU体系结构类型*/

uint8_tih_type;/*镜像类型*/

uint8_tih_comp;/*压缩类型*/

uint8_tih_name[32];/*镜像名称*/

}

Sibl从NAND Flash起始地址开始搜索。如果读到镜像同步字ih_magic,则识别镜像程序,并根据偏移地址读取程序大小ih_size和加载地址ih_load,将程序加载到指定的SDRAM空间;加载完成后根据CRC校验码ih_dcrc对SDRAM数据进行CRC检测;最后根据镜像类型ih_type判断镜像是否可执行,若可执行,则跳入镜像入口地址ih_ep,否则Sibl继续搜索NAND Flash镜像程序。

镜像程序使用U-boot提供的工具mkimage添加头信息,命令格式如下:

mkimage-A arch-O os-T type-C comp-a addr-e ep-n name-d data_file image

③ 完成Sibl加载后,内存空间分布如图6所示,系统进入启动流程的第三阶段U-boot。U-boot完成Linux内核镜像的解压缩和操作系统启动前的初始化,最终跳入内核入口地址,完成对Linux的引导。

6 系统性能分析

系统构建提供了一个完整的LPC3180嵌入式软硬件平台,下面对LPC3180浮点运算能力进行测试和分析。测试方法是使用一个浮点运算密集的算法,用ADS编译器分别编译使能硬件VFP和软浮点运算两个版本的测试程序,并在不同的CPU时钟频率下比较运行时间,结果如表1所列。

分析实验数据,可以得出结论: VFP协处理器在相同时钟频率下,提高了5倍左右的浮点运算性能。因此,LPC3180平台结合VFP协处理器,能够实现复杂的浮点运算密集算法。在微控制器中集成硬件浮点运算单元,这使得微控制器的数据处理能力大大提高,能够胜任多数的数字信号处理应用。

结语

本文介绍了以LPC3180微控制器为核心的嵌入式软硬件平台的设计与实现,并测试、验证了LPC3180的浮点运算性能。该平台对于LPC3180的应用开发具有借鉴意义。目前LPC3180在医疗器械、工业控制、POS机、数字信号处理等领域有着广泛的应用。

电子发烧友App

电子发烧友App

评论