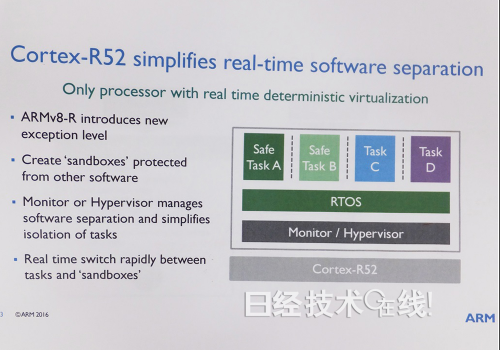

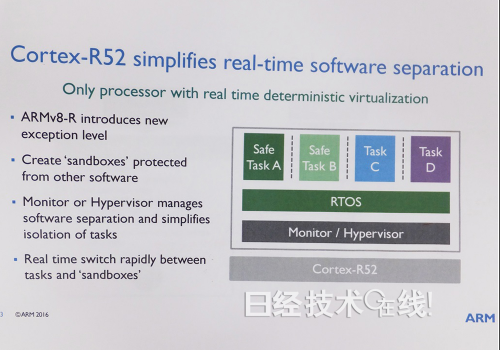

英国ARM公司2016年9月20日(当地时间)发布了瞄准自动驾驶汽车、医疗及工业机器人等领域、可用于实时处理的CPU内核“Cortex-R52”。ARM日本公司于9月21日面向日本的新闻媒体举行

2016-09-29 10:12:51 2310

2310

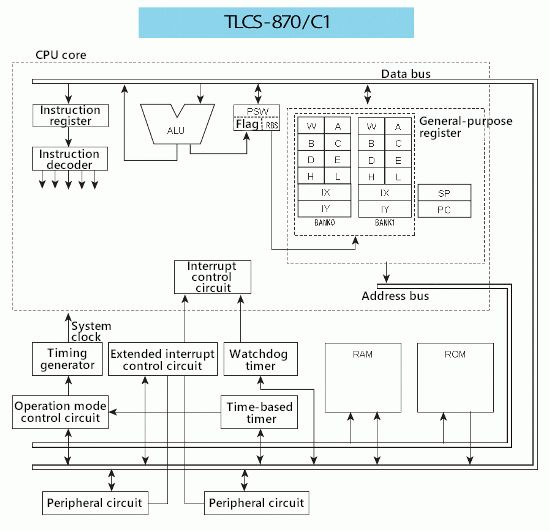

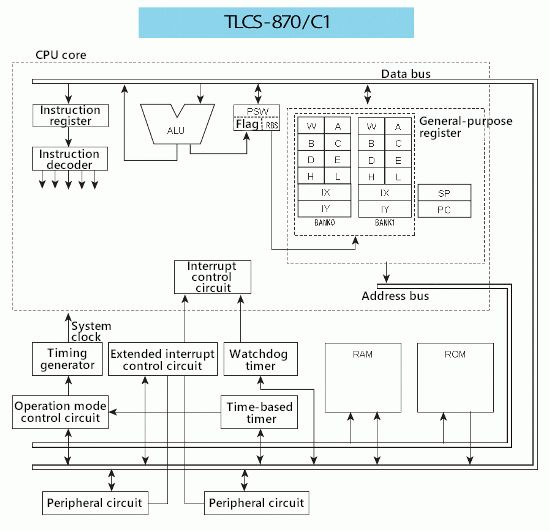

上一节的芝识课堂中我们介绍了微控制器的CPU部分功能单元和基本指令执行的知识,今天我们继续以东芝的TLCS-870/C1内核作为示例,跟大家一起认识CPU配置的另一个关键环节——“中断处理”。Continue

2022-07-18 10:41:11 814

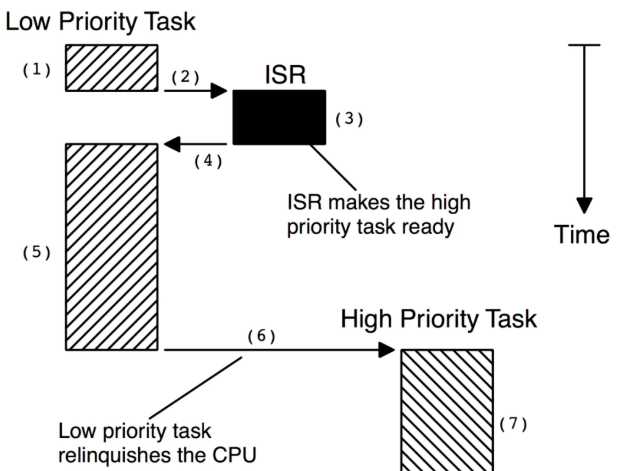

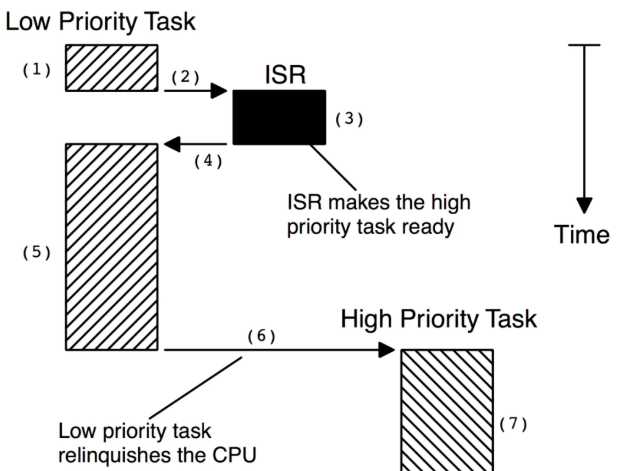

814 非抢占式内核 非抢占式内核要求每个任务(线程)都做一些事情来明确放弃对 CPU 的控制,为了保持多任务并发的错觉,必须要有这一步操作。 非抢占式调度也称为协作多任务,任务相互协作以共享 CPU,异步

2022-09-29 18:38:43 890

890

瑞萨电子今日宣布,推出基于64位RISC-V CPU内核的RZ/Five通用微处理器(MPU)——RZ/Five采用Andes AX45MP,基于RISC-V CPU指令集架构(ISA),增强了瑞萨现有基于Arm® CPU内核的MPU阵容,扩充了客户的选择,并在产品开发过程中提供更大灵活性。

2022-03-01 13:54:21 1202

1202

大家对下面这段话:“单片机也称微控制器,并不是所说的CPU,但它是CPU控制的。所说的片内外设就是指cpu控制的模块,如定时器、串口等,这个cpu就是微控制器的内核,根据不同内核也有不同型号”中

2014-07-12 00:36:27

THERMAL PAD CPU 1.75" X 1.75"

2024-03-14 20:50:16

CPU001-BB - CPU001-BB - List of Unclassifed Manufacturers

2022-11-04 17:22:44

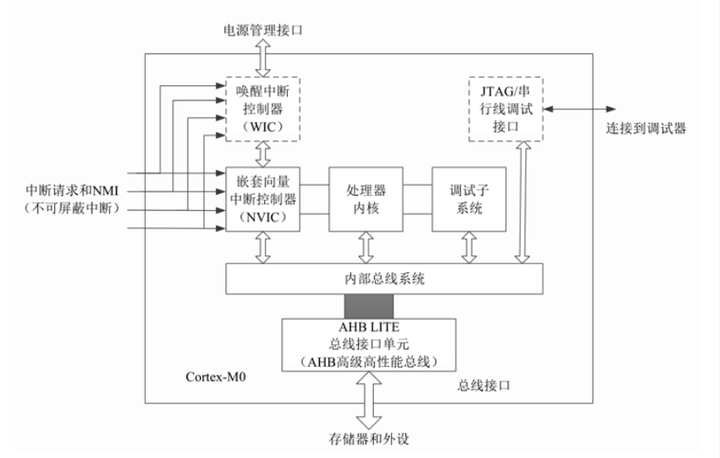

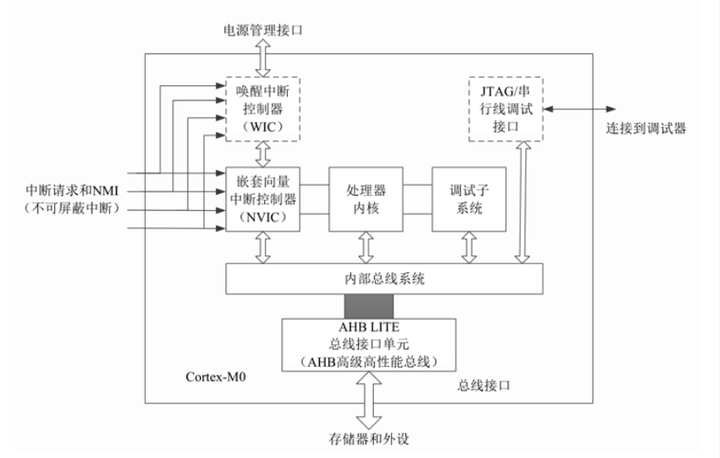

嵌入式之Cortex-M架构CPU内核寄存器及处理模式学习笔记

2021-12-15 06:13:09

CPU是什么?CPU主要由哪几部分构成?CPU的内部处理过程是怎样的?

2021-10-19 09:21:03

■ 内核CPU― 32位ARM Cortex-M4 内核+ FPU,单周期硬件乘除法指令,支持DSP指令和MPU― 内置8KB 指令Cache缓存,支持Flash加速单元执行程序 0 等待― 最高

2021-08-20 06:32:56

理想电压源的特点有哪些?理想电压源与理想电流源有何区别?

2021-10-14 07:10:37

主系统由 32 位多层 AHB 总线矩阵构成,可实现以下部分的互连:● 八条主控总线:— Cortex™-M4F 内核 I 总线、D 总线和 S 总线— DMA1 存储器总线— DMA2 存储器总线

2021-08-05 07:51:29

CONTROL LOGIC CPU44 W PROCESS

2023-03-29 20:04:47

CJ2M-CPU11 - SYSMAC CJ-series CJ2M CPU Units - Omron Electronics LLC

2022-11-04 17:22:44

CJ2M-CPU12 - SYSMAC CJ-series CJ2M CPU Units - Omron Electronics LLC

2022-11-04 17:22:44

CONTROL LOGIC CPU 448K PROG

2023-03-22 19:22:27

CONTROL LOGIC CPU 448K PROG

2023-03-29 20:04:48

CONTROL LOGIC CPU 448K PROG

2023-03-29 20:04:47

CONTROL LOGIC CPU 64K PROG

2023-03-29 20:04:46

CONTROL LOGIC CPU 128K PROG

2023-03-29 20:04:46

CONTROL LOGIC CPU 256K PROG

2023-03-29 20:04:47

关于内核学习我建议不要上来就读内核而是先了解内核的构成和特性,然后通过思考发现疑问这时再去读内核源码。即先了解概貌在读局部细节。而且内核分成好多部分,不要只是按照顺序去读,应该针对某一部分比如内存管理或进程管理横向读几本书,这样可以理解很全面。

2019-07-24 07:09:16

CPU轻量级隔离特性基本概念CPU轻量级隔离特性提供了根据系统负载和用户配置来选择合适的CPU进行动态隔离的能力。内核会将被隔离CPU上的任务和中断迁移到其他合适的CPU上执行被隔离的CPU会进入

2023-02-04 16:40:29

INTEL CPU 志强E5 V4,Linux内核版本3.10.0-514.26.2.el7.x86_64及以上平台下,PCI寄存器操作,仅可写,读操作引起内核崩溃,各位大牛有谁知道什么原因,谢谢!(PS: 降低内核版本或更换E5 V3 ,均可解决问题)

2017-09-07 13:22:47

掌握STM32的估计库的构成和每个库文件的作用,对我们使用库非常有帮助,我们这里以3.5版本的库来分析。按照内核和外设的关系,我把库分成两个部分:内核相关,处理器相关

2021-08-17 08:43:55

s5pv210是三星公司推出的32位RISC微处理器,其CPU采用的是ARM Cortex-A8内核,基于ARMv7架构,这里的内核和架构是什么意思???

2015-03-25 12:09:45

arm处理器复位cpu后先进入管理模式,然后内核是怎样切换模式的,在程序中好像无法体现出来。

2022-11-01 15:16:49

z80内核是什么cpu

2023-09-20 07:26:32

你好,正如我们所知,每个CPU可以在睡眠中独立于其他CPU的状态。如果两个内核处于不同的功率模式,那么这意味着相同的外设对不同的内核表现出不同的性能吗? 以上来自于百度翻译 以下为原文Hi

2018-12-14 16:04:32

中,CPU、RAM、ROM、I/O这些都是单独的芯片,然后这些芯片被安装在一个主板上,这样就构成了我们的PC主板,进而组装成电脑,而单片机只是将这所有的集中在了一个芯片上而已。2、什么是ARM芯片?凡是采用ARM内核的芯片(或者凡是采用ARM内核的CPU)都是ARM芯片3、什么是ARM内核?所谓内核,就是CP

2022-01-13 06:55:55

内核:基于平头哥半导体 (T-HEAD Semiconductor) CPU E801 内核开发(原生:中天微CK801)RISC 精简指令结构64K Flash ,独立2Kbytes Data

2021-12-09 06:20:46

请问下:对市面上的ARM SOC芯片,如何可靠识别ARM SOC内所使用的ARM CPU内核IP型号?1、对市面上的ARM SOC芯片,如何可靠识别ARM SOC内所使用的ARM CPU内核IP

2022-08-01 14:14:45

如何对RK3399 CPU arm64的内核进行配置?

2022-02-16 06:20:18

问题:我有个 Linux 进程运行在多核处理器系统上。怎样才能找出哪个 CPU 内核正在运行该进程?当你在 [url=]多核 NUMA 处理器上[/url]运行需要较高性能的 HPC(高性能计算

2016-10-24 15:30:42

我需要保留一个 CPU 核心用于关键中断和 WIFI 处理。当我使用 PSRAM 时,访问 PSRAM 的 CPU 核心将停止,直到 PSRAM 数据传输结束。如何配置 ESP-IDF 只为一个 CPU 内核分配 PSRAM,这样另一个 CPU 内核就不会因为访问 PSRAM 而停滞?

2023-03-02 06:54:04

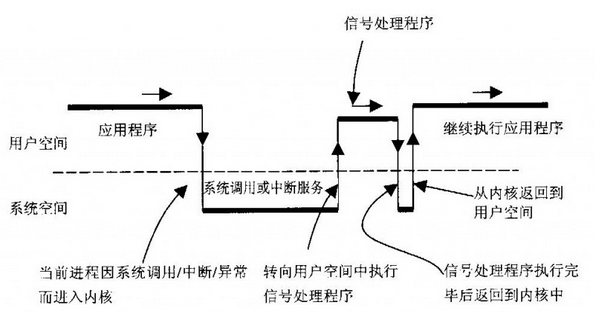

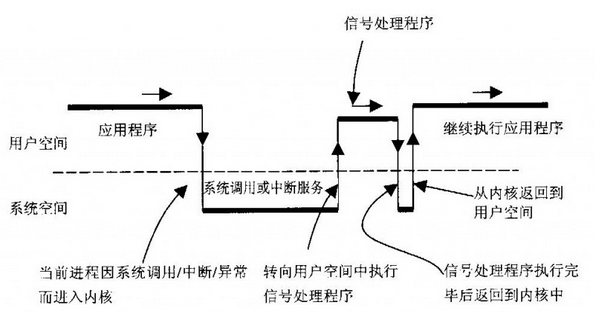

一. Linux内核简介1. 系统架构1.1 Linux系统架构Linux系统由用户空间和内核空间两部分构成,用户空间包括用户应用程序和C库,而内核空间包含了系统调用接口、狭义上的内核以及体系结构

2021-12-20 07:23:39

你好 是否可以通过SPAEr320 CPU中的USB启动机制启动Linux内核? 如果是,可以使用哪些工具为可启动USB记忆棒生成图像?我希望至少能够获得一份认可的应用说明链接。 谢谢 亨氏 #USB启动

2019-08-07 14:23:28

计算机硬件系统由哪几部分构成?编程语言的作用及与操作系统和硬件的关系是什么?请问CPU与寄存器,内核态与用户态及如何切换?

2021-10-25 06:31:50

三菱PLC Q基本模式CPU功能解说程序基础篇:

1 概要1.1 特长1.2 程序存储和运算1.3 方便编程的软元件指令2 系统构成2.1 系统构成2.1.1 Q00JCPU的场合2.1.2 Q00CPU/Q01CPU的

2008-11-21 13:27:20 113

113 三菱PLC Q基本模式CPU硬件设计保养:1 概要1.1 特点2 系统构成2.1 系统构成2.1.1 Q00JCPU2.1.2 Q00/Q01CPU2.1.3 GX Developer的构成2.2 使用时的注意事项2.3 功能版本的确认方

2008-11-21 13:33:43 73

73 三菱PLC Q CPU用户手册(硬件设计维护点检篇):

第1 章概述1.1 特点第2 章系统构成2.1 系统构成2.1.1 单CPU 系统的系统构成2.1.2 GOT 总线连接的系统构成.2.1.3 外围设备

2008-11-21 14:03:59 314

314 本文主要讲述的是便携式CPU内核的供电问题。

2009-04-30 10:10:31 25

25 提出一种基于51 内核网络单片机的嵌入式远程监控系统方案,介绍以DS80C400单片机为核心的系统硬件构成和基于TINI运行环境的应用程序设计方法。该方案可以实现串口、CAN总线等轻

2009-05-18 14:25:30 19

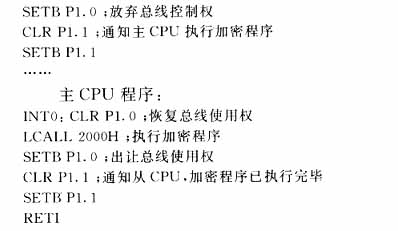

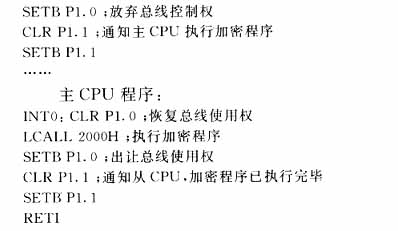

19 介绍了单片机双CPU构成复杂系统的电路以及该系统的几种应用实例。 关键词:单片机,双CPU,总线,数据存储器

2009-05-06 20:44:22 548

548

TMS320C31和80C196双CPU构成的高速实时控制系统

介绍了采用TMS320C31和80C196双CPU构成的高速实时控制系统的基本构成,给出了TMS320C31、80C196与双口RAM IDT7140

2009-12-08 14:21:54 1444

1444

什么是CPU核心

核心(Die)又称为内核,是CPU最重要的组成部分

2009-12-17 10:57:07 1067

1067 双核cpu

双核就是2个核心,核心(Die)又称为内核,是CPU最重要

2009-12-17 11:01:49 923

923 CPU核心技术 核心(Die)又称为内核,是CPU最重要的组

2009-12-18 09:54:16 1229

1229 CPU核心类型 核心(Die)又称为内核,是CPU

2009-12-24 09:58:03 507

507 CPU内核结构解析 CPU内核主要分为两部分:运算器和控制器。

(一) 运算器

1、 算

2010-04-15 16:13:27 1495

1495 由KIA7033构成的单片机复位电路,可手动复位,效果理想。

2012-01-04 10:50:04 2232

2232

多任务系统中,内核负责管理各个任务,或者说为每个任务分配CPU时间,并且负责任务之间的通讯。内核提供的基本服务是任务切换。

2012-05-11 10:41:03 1635

1635 ‘Warrior P-class’ CPU,这是迈向高性能 MIPS CPU IP 内核的重大进展。新款MIPS P5600 内核可提供领先业界的 32 位性能,内核芯片面积比竞争对手小 30% ,提供较同类领先的低功耗特性,MIPS P5600 内核成为各种移动、消费和嵌入式应用的理想选择。

2013-10-22 16:29:28 805

805 今年三星的半导体部门已经开始尝试一些大的飞跃,其运用于Galaxy S7旗舰的Exynos 8890处理器,首次采用了自主定制的CPU内核M1。

2016-11-25 14:50:10 705

705 今年三星的半导体部门已经开始尝试一些大的飞跃,其运用于Galaxy S7旗舰的Exynos 8890处理器,首次采用了自主定制的CPU内核M1。

2016-11-28 13:57:07 542

542 发布了多款新产品,表现出了大力发展IoT市场的勃勃雄心。除了CPU内核、安全技术、互联IP内核、无线通信IP内核、IoT子系统、POP等SoC设计用新产品之外,ARM还宣布提供SaaS。

2016-12-13 15:29:53 1629

1629 1 引言 本文分析了Windows 系统的进程调度机制,并设计了一种基于Windows 操作系统内核驱动的多核CPU 线程管理方法,实现了一个基于Windows 内核驱动的线程管理服务系统,它能

2017-10-31 11:02:46 0

0 如果让内核定期对设备进行轮询,以便处理设备,那会做很多无用功,因为外设的处理速度一般慢于CPU,而CPU不能一直等待外部事件。所以能让设备在需要内核时主动通知内核,会是一个聪明的方式,这便是中断。

2017-11-14 15:48:05 2906

2906 Architecture, ISA)。本节概述基于 M4K 处理器内核的 PIC32 系列单片机的 CPU 特性和系统架构。

2018-06-06 12:29:00 19

19 PIC32 系列参考手册—第50章 采用MIPS32® microAptiv™和M-Class内核的器件的CPU

2018-05-25 17:29:32 6

6 CPU的主频,即CPU内核工作的时钟频率(CPU Clock Speed)。通常所说的某某CPU是多少兆赫的,而这个多少兆赫就是“CPU的主频”。

2018-09-10 11:17:45 231941

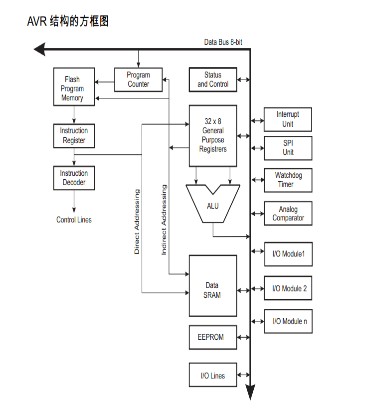

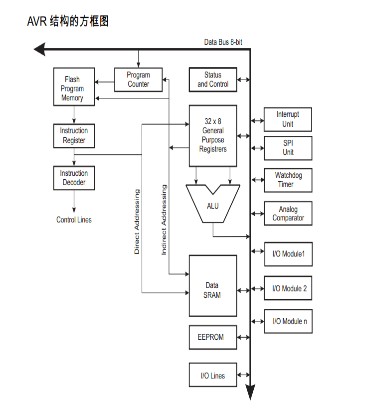

231941 AVR采用了Harvard结构,具有独立的数据和程序总线,CPU在执行一条指令的同时,就将PC中指定的下一条指令取出,构成了一级流水线运行方式,实现了一个时钟周期执行一条指令,数据吞吐量高达1MIPS/MHz。

2018-10-17 16:39:35 4612

4612

让我们考虑一些似乎是兼容处理器技术平滑发展的例子,这些技术将MCU产品线推向微处理器领域。飞思卡尔提供基于ARM Cortex-M4内核的Kinetis MCU系列,包括K10,K20,K30

2019-01-25 08:56:00 3870

3870

2019年就要正式量产了,6月份就会发布10nm Ice Lake处理器,今天Intel也正式宣布了第二代10nm工艺的处理器Tiger Lake,将会使用全新的CPU内核及GPU内核。

2019-05-09 15:19:03 1801

1801 让我们快速描述一下CPU。CPU在设备上运行OS和各种应用程序,处理数据并提供输出。现在的CPU通常包含多个处理器(内核)。比如双核,四核,八核等。

2020-02-24 20:44:13 2899

2899 ARM宣布,从2022年开始,其所有“大型” CPU内核将仅采用64位。但这为ARM将继续为使用其“ LITTLE” CPU内核的新型节能芯片提供32位支持提供了可能性。

2020-10-12 10:50:40 2603

2603 本篇有相当的难度,涉及用户栈和内核栈的两轮切换,CPU四次换栈,寄存器改值,将围绕下图来说明. 解读 为本篇理解方便,把图做简化标签说明: user:用户空间 kernel:内核空间 source

2021-04-28 16:56:17 1366

1366

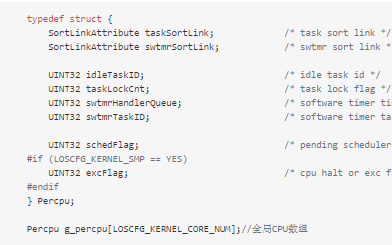

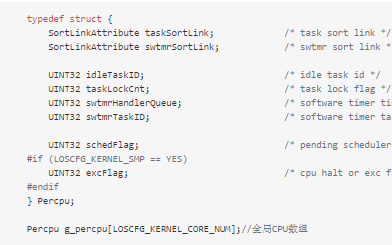

这是内核对CPU的描述,主要是两个排序链表,一个是任务的排序,一个是定时器的排序.什么意思? 在

2021-04-25 09:24:00 1381

1381

本篇说清楚CPU cpu是负责执行指令的,谁能给它指令?是线程(也叫任务), 任务是内核的调度单元,调度到哪个任务CPU就去执行哪个任务的指令. 要执行指令就要有个取指令的开始地址. 开始地址就是

2021-03-15 14:37:06 1890

1890 适用于工业和嵌入式 PC 的 Intel Core i7 (Arrandale) 48A CPU 内核参考设计;此两相 48A 设计面向采用 Intel Core i7 处理器的嵌入式和工业 PC,在小面积内提供紧凑 CPU 内核电压调节和出众热性能

2020-11-24 08:00:00 2

2 为了同步对内核共享资源的访问,内核提供了down函数和up函数用于获取和释放资源。down和叩所保护的访问资源的内核代码区域,就构成一个临界区。在等待获取资源进入临界区的过程中,代表进程运行的内核

2021-01-14 16:55:43 5

5 混合内核实质上也是微内核,而外内核是一种比较极端的设计方法,目前还处于研究阶段,所以我们就着重讨论宏内核与微内核两种内核。

2021-03-17 16:05:48 11

11 从全面升级到Armv9架构,到公布Neoverse V1和N2平台技术细节,再到推出三款基于Armv9架构的全新CPU内核,短短两个月时间里,Arm全面计算(Arm Total Compute)战略正在以令人难以置信的速度加速推进,密集,但有条不紊。

2021-06-12 09:11:00 3985

3985 目录一、51内核二 、ARM内核一、51内核51单片机由一个IP核和片上外设组成,IP核就是上图中的CPU,片上外设就是上图中的:时钟电路、SFR和RAM、ROM、定时/计数器、并行I/O口、串行

2021-11-15 10:06:02 11

11 设计,俗称CPU内核,例如Zilog的Z80内核、Intel的8051内核、Microchip的PIC16、18、dsPIC、PIC32内核、Motorola的68000内核、Atmel的AVR...

2021-11-15 13:06:03 37

37 先进半导体解决方案的主要供应商瑞萨电子公司(TSE:6723)今天宣布推出围绕 64 位 RISC-V CPU 内核构建的 RZ/5 个通用微处理器单元 (MPU)。RZ/Five 采用

2022-03-01 16:52:22 3975

3975 非抢占式内核的优点之一是中断延迟更低,在任务级别,非抢占内核也可以使用不可重入函数。每个任务都可以使用不可重入函数,而不必担心被另一个任务破坏。这是因为每个任务都可以在放弃 CPU 之前运行到完成。但是,不应允许不可重入函数放弃对 CPU 的控制。

2022-06-02 14:35:30 1071

1071 ,比如:cache 等,这些部分会在后面进行补充。CPU 拓扑除了描述 CPU 的组成关系外,还为内核的调度器提供服务,从而提供更好的性能。

2022-08-29 11:02:22 3343

3343 Linux内核由七个部分构成,每个不同的部分又有多个内核模块组成。

2022-10-13 15:44:45 625

625 CPU由运算器、控制器和寄存器及实现它们之间联系的数据、控制及状态的总线 构成。CPU的能力高低直接影响了整个电脑的运行速度。

2023-02-14 15:03:07 5604

5604 PLC的构成:由微处理器(CPU)、存储器(ROM,RAM)、输入/输出单元(I/O)、编程器和电源构成。

2023-03-03 15:49:18 5517

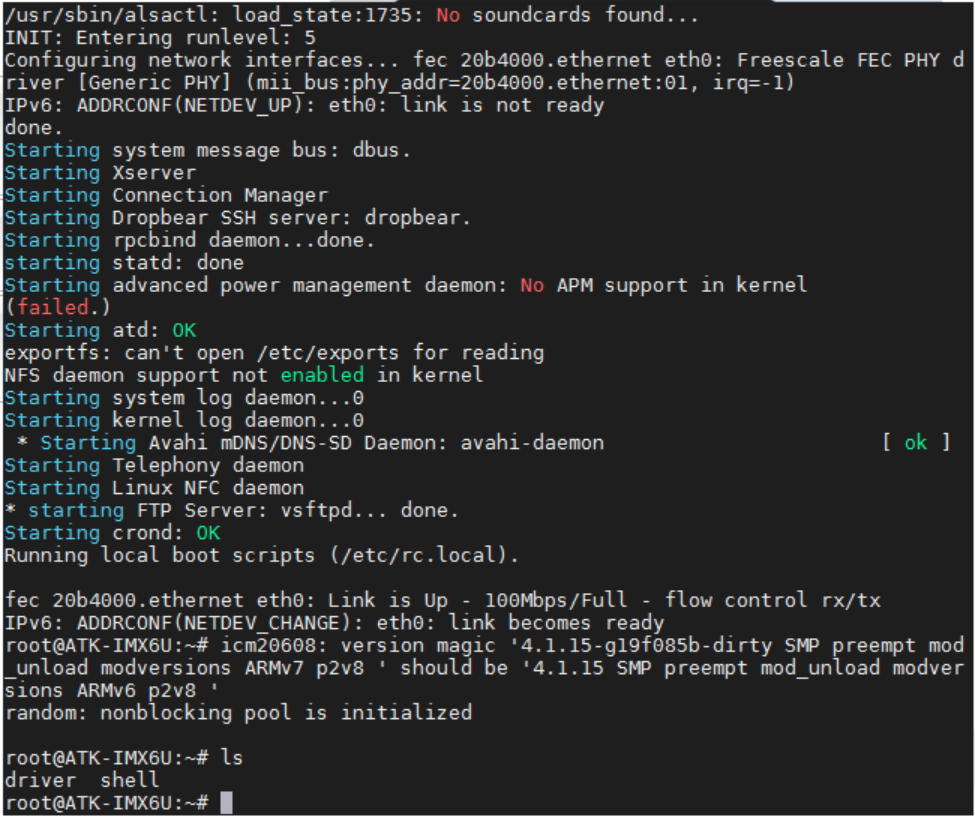

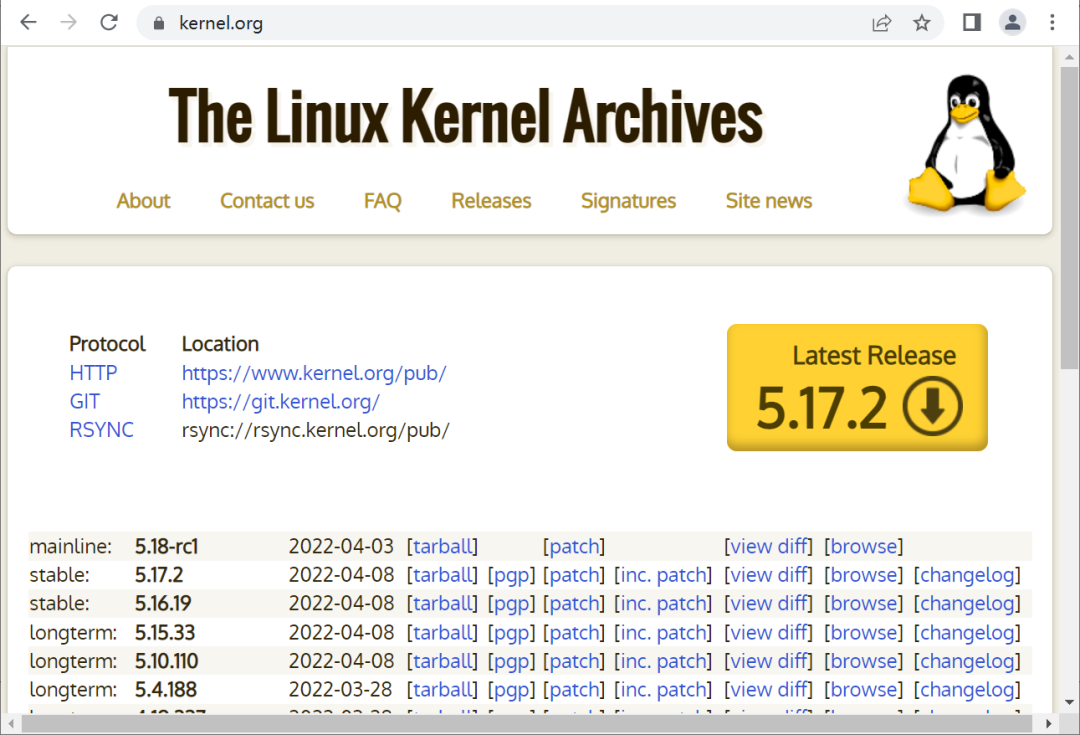

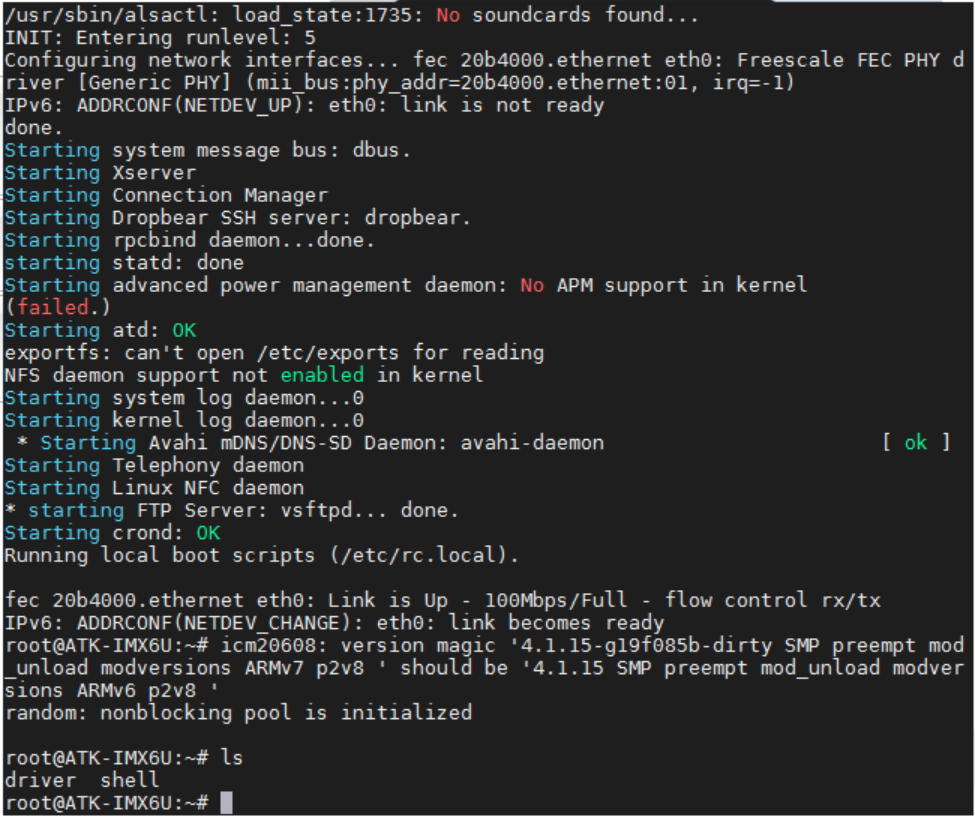

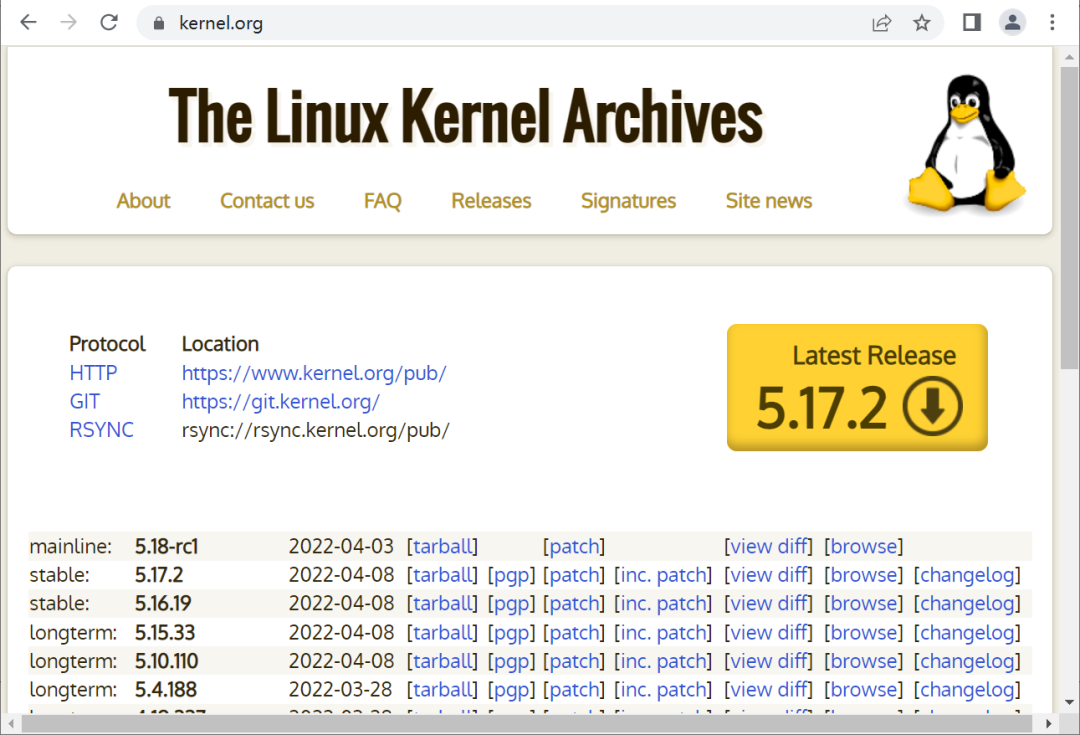

5517 半导体厂商会从 Linux内核官网下载某个版本,将其移植到自己的 CPU上,测试成功后就会将其开放给该半导体厂商的 CPU开发者。开发者下载其提供的 Linux内核,然后将其移植到自己的产品上。

2023-04-19 11:20:32 701

701

一般半导体厂商会从 Linux内核官网下载某个版本,将其移植到自己的 CPU上,测试成功后就会将其开放给该半导体厂商的 CPU开发者。开发者下载其提供的 Linux内核,然后将其移植到自己的产品上。

2023-04-19 11:20:56 791

791

初步用户手册 带 32 位 RISC CPU 内核的 ERTEC 400 增强型实时以太网控制器用户手册

2023-04-28 20:12:09 0

0 物理机器是由CPU,内存和I/O设备等一组资源构成的实体。虚拟机也一样,由虚拟CPU,虚拟内存和虚拟I/O设备等组成。

2023-06-06 15:47:00 1599

1599 芯片内核又称CPU内核,它是CPU中间的核心芯片,是CPU最重要的组成部分。由单晶硅制成,CPU所有的计算、接受/存储命令、处理数据都由核心执行。各种CPU核心都具有固定的逻辑结构,一级缓存

2023-08-02 15:21:12 1047

1047

【微控制器基础】——CPU内核与整体配置(上)

2023-10-17 17:19:38 377

377

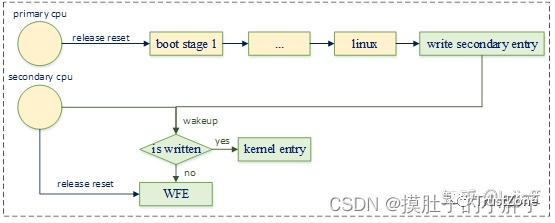

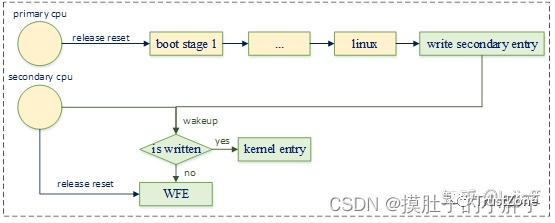

spin-table spin-table启动流程的示意图如下: 芯片上电后primary cpu开始执行启动流程,而secondary cpu则将自身设置为WFE睡眠状态,并且为内核准备了一块内存

2023-12-05 15:27:21 275

275

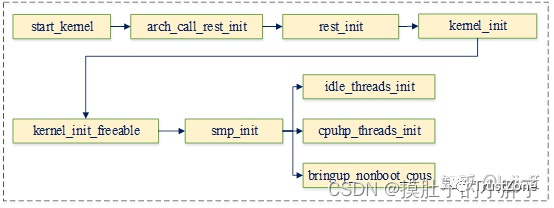

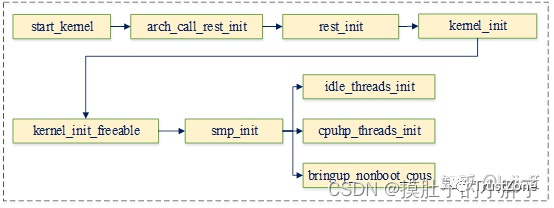

启动secondary cpu 内核在启动secondary cpu之前当然需要为其准备好执行环境,因为内核中cpu最终都将由调度器管理,故此时调度子系统应该要初始化完成。 同时cpu启动完成转交

2023-12-05 15:46:51 231

231

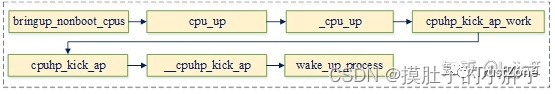

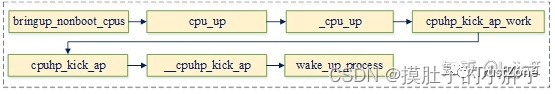

hotplug回调线程唤醒 内核使用以下流程唤醒特定cpu的hotplug线程,用于执行实际的cpu启动流程: 由于cpu启动时需要与一系列模块交互以执行相应的准备工作,为此内核为其定义了一组

2023-12-05 15:55:03 156

156

cpu_ops接口 驱动初始化完成后,cpu的cpu_ops就可以调用这些回调实现psci功能的调用。如下所示,当devicetree中cpu的enable-method设置为psci时,该cpu

2023-12-05 17:25:11 257

257 新闻快讯 全球半导体解决方案供应商瑞萨电子(TSE:6723)宣布成功设计、测试并推出基于开放标准RISC-V指令集架构(ISA)的32位CPU内核。瑞萨作为业内首个为32位通用RISC-V市场独立研发CPU内核的厂商,面向物联网、消费电子、医疗保健和工业系统打造了一个开放、灵活的平台。

2023-12-08 11:40:02 210

210 在计算市场持续迎来变革的背景下,Arm公司发布了其最新一代Neoverse CPU内核设计,分别为Neoverse V3(代号Poseidon)和N3(代号Hermes),两款内核将为服务器、云计算和基础设施领域带来更大规模和更快速度的计算能力。

2024-02-27 09:27:24 258

258

本土RISC-V CPU IP领军企业——芯来科技正式发布针对信息安全的超低功耗嵌入式RISC-V处理器CPU IP——NS100系列内核,主要针超低功耗下的信息安全应用。

2024-03-04 11:19:30 489

489

电子发烧友网站提供《用于高频 CPU 内核功率的同步降压 FET 驱动器TPS51604数据表.pdf》资料免费下载

2024-03-13 11:10:03 0

0

电子发烧友App

电子发烧友App

评论