ARM处理器是一种流行的处理器架构,用于许多现代移动设备和嵌入式系统中。中断和异常是ARM处理器中的两个重要概念,它们是处理器中断程序执行的关键机制。

2023-09-05 15:45:30 695

695

32位ARM嵌入式处理器的调试技术摘要:针对32位ARM处理器开发过程中调试技术的研究,分析了目前比较流行的基于JTAG的实时调试技术,介绍了正在发展的嵌入式调试标准,并展望期趋势。关键词:嵌入式

2021-12-14 09:08:18

ARM720T是一款通用的32位微处理器,具有8KB的高速缓存、扩大的写入缓冲区和内存管理单元(MMU),组合在一个芯片中。ARM720T中的CPU是ARM7TDMI。ARM720T是与ARM处理器

2023-08-02 11:36:56

一、简介(1)ARM Cortex系列处理器有40个32位的寄存器,其中包括33个通用寄存器和7个状态寄存器,40个中有18个可编程访问的寄存器(2)寄存器被安排成部分重叠的组,在不同的工作模式

2022-06-01 18:07:47

ARM Cortex系列处理器――Cortex-AARM Cortex系列处理器——Cortex-MARM Cortex系列处理器——Cortex-R

2021-01-12 07:54:17

指令变为中断和系统异常处理函数的起始地址。—寄存器组和某些编程模式也做了改变。这些变化意味着许多为经典ARM处理器编写的汇编代码需要修改,老的项目需要修改和重新编译才能迁移到Cortex-M的产品上

2021-05-12 06:30:00

ARM cortex 处理器本身仿真要注意什么,uvm仿真时处理器本身arm提供验证list吗?

2022-08-05 14:14:40

指令和数据地址提供翻译和访问权限检查。

ARM920T处理器支持ARM调试架构,并包括辅助硬件和软件调试的逻辑。ARM920T处理器还支持协处理器,导出指令和数据总线以及简单的握手信号

2023-08-02 13:05:00

ARM9系列处理器是英国ARM公司设计的主流嵌入式处理器,主要包括ARM9TDMI和ARM9E-S等系列。本文主要介绍它们与ARM7TDMI的结构以及性能比较。

2019-10-09 07:30:25

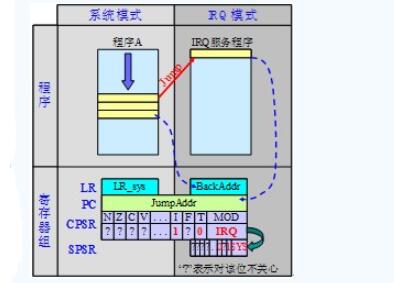

寄存器的赋值来切换的。 Tips:当处理器运行在用户模式下,某些被保护的系统资源是不能被访问的。 除用户模式外,其余6种工作模式都属于特权模式; 特权模式中除了系统模式以外的其余5种模式称为异常

2023-12-15 10:15:25

` ARM微处理器支持7种运行模式,分别如下: 用户模式(usr):ARM处理器正常的程序执行状态。快速中断模式(fiq):用于高速数据传输或通道处理。外部中断模式(irq):用于通用的中断处理

2014-03-20 11:15:00

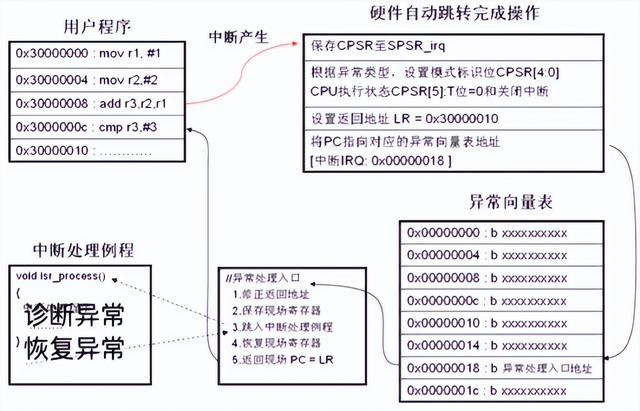

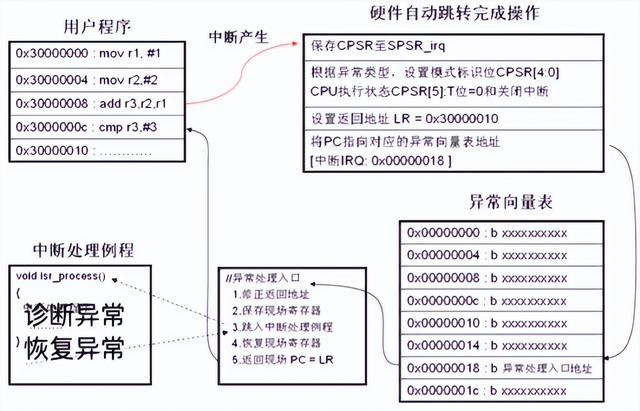

ARM处理器异常相应过程:1、保存处理器当前状态、中断屏蔽位以及各个条件标志位。将当前程序状态寄存器CPSR保存到对应的SPSR寄存器中实现。每个异常中断都有对应的物理SPSR寄存器。2、设置

2021-12-14 08:57:34

在ARM处理器中一条指令的执行分为取指、译码、执行三个阶段,由于指令流水线的存在造成当前执行的指令的地址是PC-8(ARM指令集),那么当前执行指令的下一条指令的地址应该是PC-4,所以在异常产生

2017-03-02 15:08:27

在ARM处理器中一条指令的执行分为取指、译码、执行三个阶段,由于指令流水线的存在造成当前执行的指令的地址是PC-8(ARM指令集),那么当前执行指令的下一条指令的地址应该是PC-4,所以在异常产生

2017-03-07 16:40:45

ARM处理器中引起异常的原因是什么?

2022-11-03 15:20:37

ARM处理器中断处理的编程是怎么实现的?

2021-04-27 06:46:53

)。FIQ 还必须禁用中断。如果一个 FIQ 例程必须重新启用中断,则它太慢了,并应该是 IRQ 而不是 FIQ。 6.ARM处理器对异常中断的响应过程 ARM处理器对异常中断的响应过程如下所述

2020-11-17 16:13:49

,ARM微处理器会执行以下几步操作从异常返回:将连接寄存器LR的值减去相应的偏移量后送到PC中。将SPSR复制回CPSR中。若在进入异常处理时设置了中断禁止位,要在此清除。欲知更多请访问中华矽智网SIPMall

2011-01-27 11:13:20

,ARM微处理器会执行以下几步操作从异常返回:将连接寄存器LR的值减去相应的偏移量后送到PC中。将SPSR复制回CPSR中。若在进入异常处理时设置了中断禁止位,要在此清除。欲知更多请访问中华矽智网SIPMall

2011-01-27 14:19:05

本帖最后由 eehome 于 2013-1-5 10:10 编辑

ARM处理器启动代码的分析与编程

2012-08-03 22:01:48

(或者可选为只允许)特权模式下访问。此外,特权模式可以自由的切换处理器模式,而用户模式不能直接切换到别的模式。异常模式特权模式中除系统(system)模式之外的其他5种模式又统称为异常模式。它们除了

2017-10-12 11:30:08

模式外,其它模式均为特权模式(Privileged Modes)。ARM内部寄存器和一些片内外设在硬件设计上只允许(或者可选为只允许)特权模式下访问。此外,特权模式可以自由的切换处理器模式,而用户模式

2017-11-06 10:43:47

Modes)。ARM内部寄存器和一些片内外设在硬件设计上只允许(或者可选为只允许)特权模式下访问。此外,特权模式可以自由的切换处理器模式,而用户模式不能直接切换到别的模式。 异常模式特权模式中除系统

2017-10-25 16:55:35

ARM处理器都是RISC结构,单周期操作,指令流水线,使用加载或存储指令访问内存。ARM7采用冯-诺依曼结构,3级流水线;ARM9采用哈佛结构,5级流水线;Cortex-A15采用13级流水线

2021-12-21 07:16:24

ARM处理器有哪些系列?

2021-11-04 07:35:30

ARM处理器模式和ARM处理器状态有何区别?

2022-11-01 15:15:13

,ARM公司的高性能、低耗能的RISC微处理器目前占据了手机处理器90%的市场份额。然而一些预测机构分析,智能手机市场开始趋于稳定。相较于去年,只实现了个位数的增长。ARM也不会单纯的在消费电子领域

2016-12-16 19:24:17

PC 寄存器R15用做程序计数器(PC)。 ARM程序状态寄存器 在所有处理器模式下都可以访问当前的程序状态寄存器CPSR。CPSR包含条件码标志,中断禁止位,当前处理器模式以及其它状态和控制信息

2018-07-06 07:59:05

一、ARM处理器共有7种运行模式usr是普通模式,其他六种是特权模式(Privileged Modes),在这些模式下,程序可以访问所有的系统资源,也可以任意地进行处理器模式的切换。除了usr

2022-04-14 10:57:58

飞凌嵌入式-ARM处理器让全自动生化分析仪越来越小

2020-12-30 06:44:46

本帖最后由 i2c 于 2014-10-13 14:07 编辑

ARM 是 32 位嵌入式微处理器的行业领先提供商,已推出各种各样基于通用架构的处理器,这些处理器具有高性能和行业领先的功效

2014-10-13 14:04:17

异常就是正在执行的指令,由于各种软件或硬件故障被打断,比如,在读数据或指令时,访问存储器失败、产生了一个外部硬件中断等。当这些情况发生时,在ARM系统里,由异常和中断处理程序做出相应的处理,当处理

2013-04-08 10:53:07

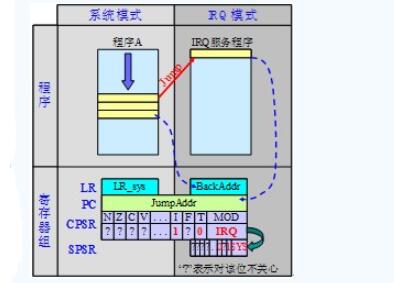

工作是任何异常发生时都必须要做的,所以ARM处理器就会自动带我们完成。其它重要的工作,必须由程序员来完成。ARM处理器处理的事包括从用户模式切换到IRQ模式、状态寄存器值的变化及跳转。比如说,处理器自动

2013-05-24 10:30:42

工作是任何异常发生时都必须要做的,所以ARM处理器就会自动带我们完成。其它重要的工作,必须由程序员来完成。ARM处理器处理的事包括从用户模式切换到IRQ模式、状态寄存器值的变化及跳转。比如说,处理器自动

2013-08-09 16:15:24

在学习与开发ARM处理器的过程中,一个不能绕开的话题就是异常处理流程。它在ARM的体系架构中,占据着不可动摇的重要地位。此处就以Coterx-A系列的ARM处理器简单分析一下异常中断处理流程。说异常

2016-11-11 09:55:57

在学习与开发ARM处理器的过程中,一个不能绕开的话题就是异常处理流程。它在ARM的体系架构中,占据着不可动摇的重要地位。此处就以Coterx-A系列的ARM处理器简单分析一下异常中断处理流程。说异常

2016-10-14 16:15:42

现场,在从异常中断处理程序退出时,要恢复被中断的程序的执行现场。本文讨论ARM体系中的异常中断机制。ARM体系中异常中断种类:ARM体系中异常中断如下面的介绍。复位(Reset):当处理器的复位引脚有效

2020-08-28 08:09:17

=A+12,处理器将 A+8(PC-4)保存到 LR.A+8PC;lr! 返回时,要返回到 A 处继续执行,所以指令为 SUBS PC,LR,#8.(PC=A=LR-8)白话解释:对于数据访问中止异常

2016-07-22 11:32:45

异常(exception)和特权(privilege)是在ARMv8-A中定义的两个概念。现代软件期望被分成不同的模块,每个模块对系统和处理器资源具有不同的访问级别。这方面的一个例子是操作系统内核

2022-04-11 16:06:28

ARM体系结构所支持的异常和具体含义如下:1、复位(优先级1)当处理器的复位电平有效时,产生复位异常,程式跳转到复位异常处执行(异常向量:0x0000,0000);2、未定义指令(优先级6)当ARM

2014-10-13 10:06:50

cpu的架构有哪几种?ARM和Intel处理器有哪些区别?

2021-10-22 07:43:53

的处理器中,Q未定义。3.J位:* 仅ARM 5TE/J 架构支持* J=1时,处理器处于Jazelle状态跳转过程异常向量表所有的CPU都有异常向量表,这是CPU设计时就设定好的,是硬件决定的。 当异常

2019-09-10 07:00:00

ARM微处理器分析与串口通信

2020-05-30 11:58:40

经典ARM微处理器包括7种异常:1、 复位异常2、 未定义指令异常3、 软件中断异常4、 预取指令异常5、 数据异常6、 IRQ(中断)7、 FIQ(快速中断)异常,单片机为中断,笼统来讲可以把异常

2021-07-16 07:04:57

ARM微处理器应用开发技术详解与实例分析

2012-08-16 20:19:41

1、ARM微处理器指令系统ARM指令集可以分为跳转指令、数据处理指令、程序状态寄存器传输指令、Load/Store指令、协处理器指令和异常中断产生指令。根据使用的指令类型不同,指令的寻址方式分为

2022-04-26 10:30:57

2.ARM微处理器的指令系统ARM微处理器的指令集是加载/存储型的,即指令集仅能处理寄存器中的数据,而且处理结果都要放回寄存器中,而对系统存储器的访问则需要通过专门的加载/存储指令来完成。ARM

2021-12-20 06:54:28

划分,只有特权模式才能访问所有的地址空间。而用户模式如果需要访问硬件,必须切换到特权模式下,才允许访问硬件。5. ARM处理器寄存器组织ARM共有37个32位寄存器,其中31个为通用寄存器,6个为状态

2022-04-13 12:08:30

ARM异常处理:只要正常的程序流被暂时中止,处理器就进入异常模式。例如响应一个来自外设的中断。在处理异常之前,ARM内核保存当前的处理器状态,这样当处理程序结束是可以恢复执行原来的程序。注意:如果

2020-04-20 10:52:02

arm为什么是32位微处理器呢?所以ARM体系结构所支持的最大寻址空间为4GB喽?

2023-03-15 10:27:53

,特权软件会让内核在恢复异常处理之前的现场。通常,中断用于表示中断信号。在ARM-A系列处理器上,中断信号可以是IRQ或FIQ中断信号。ARM体系结构将异常分为两组,同步和异步。同步异常类型可能有许多原因

2022-05-23 15:51:36

本文通过基于S3C44B0X处理器VxWorks嵌入式操作系统的BSP移植,详细分析了VxWorks操作系统基于ARM处理器的中断处理方法。

2021-04-27 06:28:03

异常就是正在执行的指令,由于各种软件或硬件故障被打断,比如,在读数据或指令时,访问存储器失败、产生了一个外部硬件中断等。当这些情况发生时,在ARM系统里,由异常和中断处理程序做出相应的处理,当处理

2015-07-27 15:31:14

异常就是正在执行的指令,由于各种软件或硬件故障被打断,比如,在读数据或指令时,访问存储器失败、产生了一个外部硬件中断等。当这些情况发生时,在ARM系统里,由异常和中断处理程序做出相应的处理,当处理

2013-03-22 16:20:47

异常就是正在执行的指令,由于各种软件或硬件故障被打断,比如,在读数据或指令时,访问存储器失败、产生了一个外部硬件中断等。当这些情况发生时,在ARM系统里,由异常和中断处理程序做出相应的处理,当处理

2013-03-22 16:34:17

一、ARM处理器之中断与异常CPU被中断的方式有指令不对、数据访问有问题、Reset信号等这称为异常,还有中断源:按键、定时器、网路数据等称为中断,中断处于一种异常体系,对于异常,首先需要我们保存

2022-05-30 09:46:26

记忆“1/0”能记忆 1 位“1/0”数据的电子单元,称之为存储元,计算机中的存储器通常将每8 个这样的存储元组成一个单元,称之为字节,字节是处理器访问存储器的最小单位。ARM 处理器对存储器空间

2022-04-29 16:41:53

RISC和CISC指令集有何区别呢?ARM处理器异常的处理过程是怎样的?

2021-11-30 07:04:33

ARM 处理器是一种低功耗高性能的 32 位 RISC(精简指令系统)处理器。从结构 入手对其进行分析,并针对目前流行的 ARM920T 核详细描述其硬件结构和编程。ARM 处理器共有 31 个

2019-09-24 17:47:38

厂商的x86架构处理器,有IBM的power架构处理器,高通苹果海思有ARM架构处理器。说PC端的处理器大家比较熟悉,移动端现在几乎ARM架构处理器一统天下。那么什么是ARM处理器呢?这就要介绍一下ARM公司的产品线,ARM属于英国一家公司,专门设计内核,目前的内核有M0,M3,M4,M7..

2021-11-24 07:05:38

复制到发生的异常模式下SPSR中; b.模式切换:将CPSR模式位强制设置为与异常类型相对应的值,同时处理器进入到ARM执行模式,禁止所有IRQ中断,当进入FIQ快速中断模式时禁止FIQ中断; c.

2018-05-10 10:58:33

在ARM处理器中,如果一个程序产生了错误并且被处理器检测到,这是就会产生错误异常。错误是怎么发生的呢?许多可能的原因都会引起错误发生,比如对于存储器相关错误,总线系统的异常响应可以有以下原因:访问

2021-10-29 13:36:12

你好我有Zynq 7z020板,我想访问它的GPIO,但我找不到Zynq处理器文档,所以我知道如何访问Zynq GPIO?问候

2019-09-11 10:48:04

运用ARM处理器系列软件工具可加速遵循安全至上的规范ARM处理器逐渐拓展应用

2021-02-24 06:35:28

。高效的处理能够极大的提升系统的性能。ARM处理器一共有7种可以暂停指令的执行序列的异常。主要分为三个部分:点击这里

2021-12-14 09:23:07

嗨,我想通过pcie链接访问外部处理器的内存。 CDMA如何知道外部处理器的内存?如何在cdma中寻址外部处理器内存?我试过访问内存并得到CDMA解码错误?谢谢

2020-04-22 10:28:03

ARM通过增加硬件协处理器来支持对其指令集的通用扩展,通过未定义指令陷阱支持这些协处理器的软件仿真。简单的ARM核提供板级协处理器接口,因此协处理器可作为一个独立的元件接入。高速时钟使得板级接口非常

2022-04-24 09:36:47

的。—向量表从跳转指令变为中断和系统异常处理函数的起始地址。—寄存器组和某些编程模式也做了改变。这些变化意味着许多为经典ARM处理器编写的汇编代码需要修改,老的项目需要修改和重新编译才能迁移

2018-09-13 10:01:22

ARM处理器,有一个寄存器,叫CPSR,保存了当前的处理器状态。但在ARMv8中,AArch64(以下简称A64)和AArch32(以下简称A32)对于这寄存器,有不同的规定。一、 A64在A64中

2022-04-01 15:17:22

应用程式码变大,需要较大的程式记忆体空间,且存在指的模式与异常令种类较多等等的缺点。4、大量使用寄存器二、ARM处理器的模式与异常ARM体系结构主要支持7种处理器模式,分别为 : 用户模式、快中断模式

2022-04-20 10:33:40

时间内响应中断次数。二、异常源在ARM体系结构中,存在7种异常处理。当异常发生时,处理器会把PC设置为一个特定的存储器地址。这一地址放在被称为向量表(vector table)的特定地址范围内,向量

2022-08-18 15:26:04

偶然机会,看到arm一个文档,发现ARM有一个型号叫merlin,属于ARM CORTEX M系列的处理器,但是平时好像没听说过这款处理器。和M0 M3 M4比起来,这个Merlin性能如何?有了解的兄弟么?

2022-10-26 16:07:49

文中分析了ARM体系结构下异常处理特点,提出一种基于ARM处理器的高效异常处理解决方案,以LPC3250硬件平台为基础,对该方案进行了设计与实现。测试结果表明,该方案的异常处理更为高效。

2021-02-23 06:15:33

= 0xffff0000ElsePC = 0x00000000未定义指令异常概念当 ARM 处理器执行协处理器指令时,它必须等待一个外部协处理器答应后,才能真正执行这条指令。若协处理器没有响应,则发生未定义

2022-04-13 11:44:12

中,而SPSR_《MODE》就是异常产生后进入的模式中的 SPSR; ARM中只有一个CPSR,也只有一个SP,被所有的模式共用) 2、设置适当的CPSR位: (1)改变处理器状态进入ARM状态

2022-04-26 09:29:21

一、经典ARM处理器七种异常:复位RESET(优先级最高)未定义指令UND软件中断SWI指令预取终止PABT数据访问终止DABT外部中断请求IRQ快速中断

2022-01-11 07:41:15

Modes);其中除去用户模式和系统模式以外的5种又称为异常模式(Exception Modes),常用于处理中断或异常,以及需要访问受保护的系统资源等情况。ARM处理器在每一种处理器模式下均有一组相应

2018-11-27 19:32:01

请问RISC处理器和ARM7处理器的区别在哪?求大神解答

2022-06-30 17:51:06

SVC32 工作模式,ARM 系统有 7 种工作模式: 除了用户模式之外的其他 6 种处理器模式称为特权模式,特权模式下,程序可以访问所有的系统资源,也可以任意地进行处理器模式的切换。特权模式中,除

2019-07-29 15:36:26

简介ARM微处理器编程模型的一些基本概念,包括工作状态切换、数据的存储格式、处理器异常等,通过对本章的阅读,希望读者能了解ARM微处理器的基本工作原理和一些与程序设计

2008-09-09 14:54:17 382

382 ARM,ARM处理器是什么意思

ARM处理器简介 ARM(Advanced RISC Machines)微处理器是采用ARM技术知识产权(IP)核的微处理器,这种ARM核技术是由英

2010-03-26 10:53:21 5130

5130 一.ARM处理器异常及其对应的模式当一个异常发生时,ARM处理器总是切换到ARM状态(即非Thumb状态)。Thumb指令集没有包含进行异常处理时需要的一些指令

2011-04-18 08:34:05 2379

2379

ARM处理器的启动代码的分析与设计

2017-09-25 08:27:29 12

12 )。 注意在ARM文档中,使用术语Exception来描述异常。Exception主要是从处理器被动接受异常的角度出发,而Interrup

2017-10-18 13:29:56 1

1 所谓异常就是正常的用户程序被暂时中止,处理器就进入异常模式,例如响应一个来自外设的中断,或者当前程序非法访问内存地址都会进入相应异常模式。

2017-11-02 12:57:26 17727

17727

嵌入式系统要求对异常及中断处理器能快速响应。文中分析了ARM体系结构下 异常处理 特点,提出一种基于 ARM处理器 的高效异常处理解决方案,以LPC3250硬件平台为基础,对该方案进行了设计与实现

2018-02-03 03:38:01 1139

1139

ARM中异常中断的类型问题分析总结 一、ARM中异常中断的类型: 异常中断名称 含义 复位(Reset) 当处理器复位引脚有效时,系统产生复位异常中断,程序跳转到复位异常中断处理程序处执行。复位

2018-04-05 10:51:00 1148

1148 ARM处理器存在七种工作模式:用户模式、快速中断模式、外部中断模式、管理模式、数据访问中止模式、未定义指令中止模式、系统模式。除了用户模式外,其它六种均为特权模式。处理器模式可以通过控制进行切换

2018-10-26 11:12:50 15554

15554 关于“进入异常”:在异常发生后,ARM7TDMI内核会作以下工作:

2020-07-21 09:10:32 2485

2485

arm处理器的异常模式包括哪些 ARM处理器的异常模式是其操作系统和应用程序中最重要的方面之一。异常就是处理器在执行指令时遇到的问题,这种问题可能由软件错误、硬件错误或者是其他因素引起。如果异常不被

2023-09-05 16:22:25 2036

2036 arm处理器有哪些中断源?arm处理器对异常中断的响应过程 ARM处理器是一种广泛使用的嵌入式处理器,运行着各种不同类型的应用程序。为了保证应用程序的稳定性和正确性,ARM处理器需要在遇到异常

2023-10-19 16:35:59 675

675 ARM9处理器从哪些方面保证了FIQ异常响应的快速性? ARM9处理器是一款高性能、低功耗的处理器,它采用了一系列技术来优化FIQ异常响应的速度和精度。本文将从以下几个方面详细介绍ARM9处理器

2023-10-19 16:36:02 413

413 机制。ARM处于操作系统和硬件之间,因此异常处理机制在有效性、安全性、可靠性方面必须经过充分测试和验证。 ARM异常指令是程序中不受控制的分支或其他例外情况,如硬件故障、访问非法地址、非法指令、软件中断等。虽然大多处理器都有异常响应和处理

2023-10-19 16:36:05 454

454 ARM中的异常中断是如何实现进入中断程序的?如何进入呢? 在计算机系统中,异常和中断是两个常见的概念。 在ARM中,异常和中断的主要目的是帮助处理器响应与系统操作相关的事件。 由于处理器必须同时执行

2023-10-19 16:36:11 481

481 如何解决C语言中的“访问权限冲突”异常?C语言引发异常原因分析 在C语言中,访问权限冲突异常通常是由于尝试访问未授权的变量、函数或其他数据结构而引起的。这种异常是编程中常见的错误之一,但是可以通过

2024-01-12 16:03:31 528

528

正在加载...

电子发烧友App

电子发烧友App

评论