像ARM926EJ 和ARM946E这两个最常见的ARM9E处理器中,都带有一套存储器子系统,以提高系统性能和支持大型操作系统。如图2所示,一个存储器子系统包含一个 MMU(存储器管理单元)或MPU

2018-05-21 08:57:29 6924

6924 ARM-CP15协处理器 ARM处理器使用协处理器15(CP15)的寄存器来控制cache、TCM和存储器管理。CP15的寄存器只能被MRC和MCR(Move to Coprocessor from

2020-10-29 10:41:07 3506

3506

之前我们在学习MMU的时候, **知道这个内存的分配和CP15协处理器** 。这里先介绍一下CP15寄存器以及访问CP15寄存器的汇编指令。

2023-09-08 17:50:52 890

890

ARM架构通过支持协处理器来扩展处理器的功能。ARM架构的处理器支持最多16个协处理器,通常称为CP0~CP15。下述的协处理器被ARM用于特殊用途。

2023-10-31 16:07:40 562

562

ARM720T是一款通用的32位微处理器,具有8KB的高速缓存、扩大的写入缓冲区和内存管理单元(MMU),组合在一个芯片中。ARM720T中的CPU是ARM7TDMI。ARM720T是与ARM处理器

2023-08-02 11:36:56

ARM946E-S是一款可合成处理器,结合了ARM9E-S™ 具有可配置存储器系统的处理器核心。它是ARM9E的成员™ 高性能32位片上系统处理器解决方案系列。

ARM946E-S是哈佛体系结构

2023-08-02 10:17:36

(AXI),用于支持优先级的二级接口

多处理器实现

•九级管道

•带返回堆栈的分支预测

•低中断延迟

•外部协处理器接口和协处理器CP14和CP15

•可选的指令和数据存储器保护单元(MPU)

•可选的指令

2023-08-02 09:15:45

14和CP15

•矢量浮点(VFP)协处理器支持

•外部协处理器接口

•使用MicroTLB管理的指令和数据存储器管理单元(MMU)

由统一的主TLB支持的结构

•指令和数据缓存,包括具有

2023-08-02 10:30:50

9TDMI处理器核心是一种哈佛体系结构的设备,使用由Fetch、Decode、Execute、Memory和Write阶段组成的五级流水线实现。它可以作为一个独立的核心提供,可以嵌入到更复杂的设备中。独立内核有一个

2023-08-02 13:05:00

对调试信道的访问。CP15:系统控制处理器,提供 16 个额外寄存器来配置与控制缓存、MMU、系统保 护、时钟模式及其他系列选项。 ARM920T 处理器的主要特征如下。ARM9TDMI 内核,ARM

2019-09-26 09:43:55

300MHz。ARM9E 系列微处理器主要应用于下一代无线设备、数字消费品、成像设备、工业控制、 存储设备和网络设备等领域。ARM9E 系列微处理器包含 ARM926EJ-S、ARM946E-S 和 ARM966E-S 三种类型,以适 用于不同的应用场合。

2019-09-26 09:36:52

请问: S3C2440可以通过设置/清除CP15协处理器的寄存器1的bit13来设置高端/低端异常向量地址,我从网上看到说也可以通过硬件电路控制,但是我一直没有查到硬件如何配置???我想了解下,谢谢谁来解惑,

2019-04-25 07:45:05

寄存器中,并且把高24位清零LDRH:将一个16位的数据送到寄存器中,并且把高16位清零STR:从源寄存器32位存入到存储器中,和前几个指令相比是不清零协处理器指令CDP:用于ARM处理器通知ARM协

2022-04-12 10:36:38

(und):当未定义的指令执行时进入该模式,可用于支持硬件协处理器的软件仿真。 更多的ARM处理器开发板应用,请关注深圳电子 :http://shop57047166.taobao.com [/url

2014-03-20 11:15:00

ARM微处理器支持7种运行模式,分别如下。 用户模式(usr):ARM处理器正常的程序执行状态。 快速中断模式(fiq):用于高速数据传输或通道处理。 外部中断模式(irq):用于通用的中断处理

2014-10-13 10:08:55

0000。 4. ARM启动代码设计 ARM启动代码直接面对处理器内核和硬件控制器进行编程,一般使用汇编语言。启动代码一般包括: 中断向量表 初始化存储器系统 初始化堆栈初始化有特殊要求的端口

2020-11-17 16:13:49

ARM处理器状态ARM微处理器的工作状态一般有两种,并可在两种状态之间切换:第一种为ARM状态,此时处理器执行32位的字对齐的ARM指令;第二种为Thumb状态,此时处理器执行16位的、半字对齐

2011-01-27 11:13:20

ARM处理器状态ARM微处理器的工作状态一般有两种,并可在两种状态之间切换:第一种为ARM状态,此时处理器执行32位的字对齐的ARM指令;第二种为Thumb状态,此时处理器执行16位的、半字对齐

2011-01-27 14:19:05

(32位)数据,从第四个字节到第七个字节放置第二个存储的字数据,一次排列。作为32位的微处理器,arm体系结构所支持的最大寻址空间为4GB。存储器格式1、大端格式:高字节在低地址,低字节在高地址;2、小端

2017-11-06 10:43:47

32位的微处理器,arm体系结构所支持的最大寻址空间为4GB。存储器格式1、大端格式:高字节在低地址,低字节在高地址;2、小端格式:高字节在高地址,低字节在低地址。指令长度Arm微处理器的指令长度是32位

2017-10-12 11:30:08

32位的微处理器,arm体系结构所支持的最大寻址空间为4GB。 存储器格式1、大端格式:高字节在低地址,低字节在高地址;2、小端格式:高字节在高地址,低字节在低地址。 指令长度Arm微处理器的指令长度

2017-10-25 16:55:35

ARM处理器都是RISC结构,单周期操作,指令流水线,使用加载或存储指令访问内存。ARM7采用冯-诺依曼结构,3级流水线;ARM9采用哈佛结构,5级流水线;Cortex-A15采用13级流水线

2021-12-21 07:16:24

Memory ordering为了提高指令执行速度,最新的arm处理器不再one bye one的执行指令,采取了一系列的措施来提高指令执行速度,包括重排序指令、存储访问方式(cache

2022-04-22 09:36:08

ARM处理器模式和ARM处理器状态有何区别?

2022-11-01 15:15:13

CPU是计算机/微控制器的核心,进行算数/逻辑运算MCU?MicroController Unit 微控制器是一个完整的计算机系统,在单个芯片上包含了处理器、存储器和所有的外设IO模块。MCU包含

2021-11-03 07:12:01

人士的面前。ARM这家不生产芯片却也能数钱数到手抽筋的公司到底有着怎样的发展史。今天小编,就带大伙一探究竟,其中包括ARM处理器的详细介绍。 ARM发展史 1978年12月5日,物理学家赫尔曼·豪泽

2016-12-16 19:24:17

位决定处理器的工作模式,如表所示。3)其他位 程序状态寄存器的其他位保留,用作以后的扩展。 ARM核工作在用户模式,R0~R15可用。 存储器格式 ARM体系结构将存储器看作是从零地址开始的字节

2018-07-06 07:59:05

处理器内核二、经典ARM处理器编程模型三、Cortex-M4处理器四、STM32F407芯片简洁一、ARM处理器特点1.ARM处理器主要特点(1)ARM7系列采用冯诺依曼结构(输入输出、控制器、存储器、处理器),ARM9~11采用哈佛体系结构(存储器分为程序存储器和数据存储器)(2)属于RISC型处理器结

2021-12-13 07:18:29

时的实现工艺。容易实现高性能。RISC体系结构的简单性、有效性很容易设计出低成本、高性能的处理器。RISC技术的历史贡献在计算机设计技术的发展变化中,20世纪60年代初引入的虚拟存储器、Cache和流水线

2022-04-24 10:02:29

首先来了解 ARM 体系结构中的字长。字(Word),在 ARM 体系结构中,字的长度为 32 位,而在 8 位/16 位处理器体系结构中,字的长度一般为 16 位。半字(Half Word),在

2019-09-27 09:37:35

一、ARM七种处理器工作模式:用户模式 usr:正常程序执行模式快速中断模式FIQ:用于高速数据传输和通道处理外部中断模式IRQ:用于通常的中断处理管理模式svc:供操作系统使用的一种保护模式

2021-07-16 06:52:30

1、ARM微处理器指令系统ARM指令集可以分为跳转指令、数据处理指令、程序状态寄存器传输指令、Load/Store指令、协处理器指令和异常中断产生指令。根据使用的指令类型不同,指令的寻址方式分为

2022-04-26 10:30:57

2.ARM微处理器的指令系统ARM微处理器的指令集是加载/存储型的,即指令集仅能处理寄存器中的数据,而且处理结果都要放回寄存器中,而对系统存储器的访问则需要通过专门的加载/存储指令来完成。ARM

2021-12-20 06:54:28

体系结构中,字节的长度为8位。2. ARM处理器存储格式ARM体系结构将存储器看作是从0地址开始的字节的线性组合。作为32位的微处理器,ARM体系结构所支持的最大寻址空间为4GB。ARM体系结构可以用

2022-04-13 12:08:30

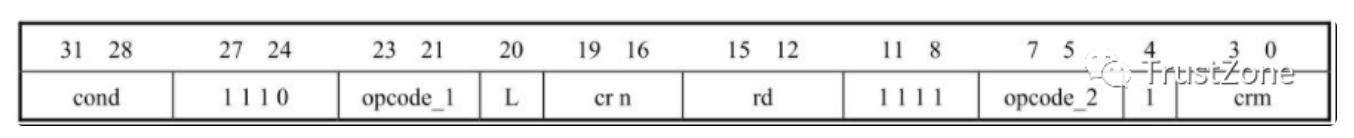

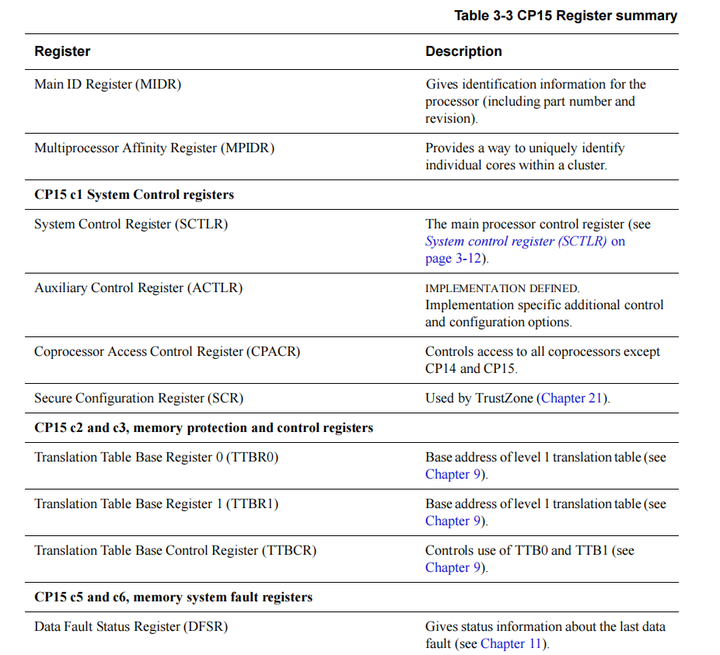

ARM核心通过两种机制进行识别。

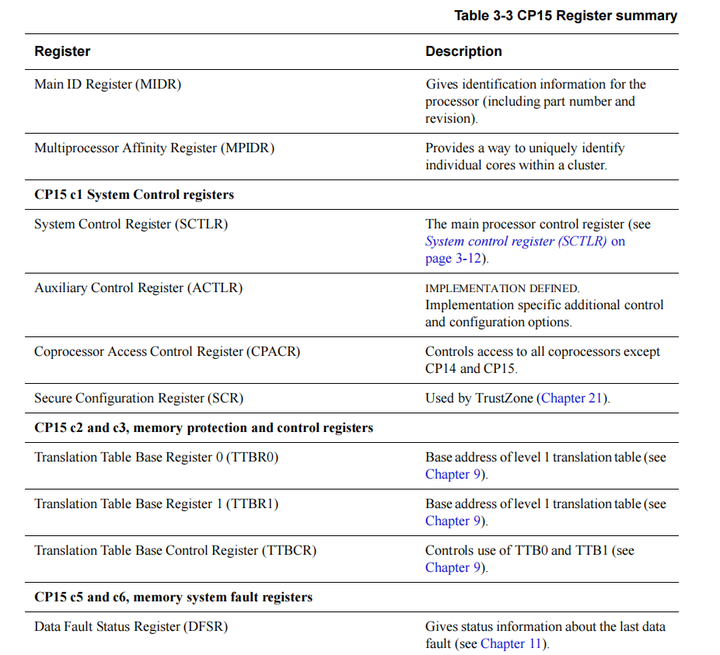

第一种是通过系统控制协处理器的寄存器0,也称为协处理器15或CP15。

CP15仅在包含MMU或MPU的处理器内核上可用,并包含多个配置寄存器(实际数量取决于内核

2023-08-23 06:55:04

[table][tr][td=670][table][tr][td]arm处理器本身所产生的地址为虚拟地址,每一个arm芯片内都有存储器,而这个芯片内的存储器的地址为物理地址。我们写程序的目的是为了

2014-03-24 11:57:18

,集成了一个被称为 CP15 的协处理器,该协处理器的 C2 寄存器中用于保存页表的基地址,下面以一级页表变换为例说明 MMU 实现地址变换的过程。4 、节访问的转换过程节和大页是支持允许只用一个

2020-10-23 15:29:49

CP15 - STANDARD CAPACITANCE TVS ARRAY - Protek Devices

2022-11-04 17:22:44

记忆“1/0”能记忆 1 位“1/0”数据的电子单元,称之为存储元,计算机中的存储器通常将每8 个这样的存储元组成一个单元,称之为字节,字节是处理器访问存储器的最小单位。ARM 处理器对存储器空间

2022-04-29 16:41:53

ARM的MMU主要实现什么功能?协处理器cp15主要主要实现何功能?简述MMU使能时存储访问过程

2021-03-16 07:57:10

第一套在8086的微计算机系统中,存储器是如何组织的?是如何与处理器总线连接的?#BHE信号起什么作用?答:8086 为 16 位处理器,可访问 1M 字节的存储器空间;1M 字节的存储器分为两个

2021-07-26 06:06:49

想了解常见的arm处理器里面,哪些系列用了具体的哪些技术。比如m0-m4猜测都是第一种方式。那m7呢?r系列呢?a系列呢?

2022-08-31 14:49:23

字处理器内核(The VLIW core)、一个可编程位流协处理器(The VLx)、视频滤波协处理器(VF)、片内存储器、显示刷新控制器(DRC)和大量可用的数字I/O接口组成。 BSP-15支持

2018-11-27 11:49:31

ARM Cortex-M33处理器的五大特色

2021-01-29 07:35:54

DSP的五大发展趋势双SHARC+内核加Cortex-A5,提升工业和实时音频处理性能单片处理器可应对多种应用需求开源操作系统是工业领域必然趋势

2021-02-19 06:11:21

传统的、基于通用DSP处理器并运行由C语言开发的算法的高性能DSP平台,正在朝着使用FPGA预处理器和/或协处理器的方向发展。这一最新发展能够为产品提供巨大的性能、功耗和成本优势。

2011-09-29 16:28:38

MCR指令将ARM处理器的寄存器中的值传到协处理器的寄存器中去这里用CP15协处理器来作为例子MCR{cond} p15,

2022-01-20 06:08:02

。 PSoC模拟协处理器通过提供可扩展和可重新配置的架构来简化基于传感器的系统的设计,该架构集成了可编程的模拟前端(AFE)和信号处理引擎(32位Arm®Cortex®-M0+),可以对其进行校准和调整

2020-09-01 16:50:45

呵呵,s3c2410...在vivi中的s3c2410.h文件中设置时钟时 有这么一段mrc p15,0,r1,c1,c0,0orr r1,r1,#0xc0000000;mcr p15,0,r1,c1,c0,0这段的每句 的意思是什么?为什么要用到些处理器指令?协处理器指令的作用是干什么?

2019-02-25 12:34:48

可以包含一个存储器存取(DMA)引擎。在增加额外的逻辑情况下,DMA引擎允许协处理器工作在位于连接到总线的存储器上的数据块,独立于CPU。2. I/O连接与I/O连接的加速器直接连接到一个专用的I/O

2015-02-02 14:18:19

Cache分开为I-Cache(指令缓存)和D-Cache(数据缓存)。系统刚上电时,I-Cacche中的内容是无效的,并且I-Cacche的功能也是关闭的,CP15协处理器的SCTLR寄存器

2016-10-13 18:02:50

代码加速和代码转换到硬件协处理器的方法如何采用FPGA协处理器实现算法加速?

2021-04-13 06:39:25

举例说明FPGA作为协处理器在实时系统中有哪些应用?FPGA用于协处理器有什么结构特点和设计原则?

2021-04-08 06:48:20

可以实现相同的ISA,但是需要在功率效率或执行速度等方面进行权衡。最基本的处理器将包括一个寄存器文件,一个ALU,系统存储器和一个控制单元,该控制单元使处理器可以根据其执行的指令来做出决定。ARM寄存器

2020-10-09 07:46:49

ARM处理器本身是32位设计,但也配备16位指令集。一般来讲存储器比等价32位代码节省达35%,然而保留了32位系统的所有优势。

2019-11-11 06:48:04

户模式进入系统模式。ARM 处理器是一个综合体,ARM 公司自身并不制造微处理器。它们是由 ARM 的合作 伙伴(Intel 或 LSI)制造。ARM 还允许将其处理器通过协处理器接口进行紧耦合。它还

2019-09-24 17:47:38

厂商的x86架构处理器,有IBM的power架构处理器,高通苹果海思有ARM架构处理器。说PC端的处理器大家比较熟悉,移动端现在几乎ARM架构处理器一统天下。那么什么是ARM处理器呢?这就要介绍一下ARM公司的产品线,ARM属于英国一家公司,专门设计内核,目前的内核有M0,M3,M4,M7..

2021-11-24 07:05:38

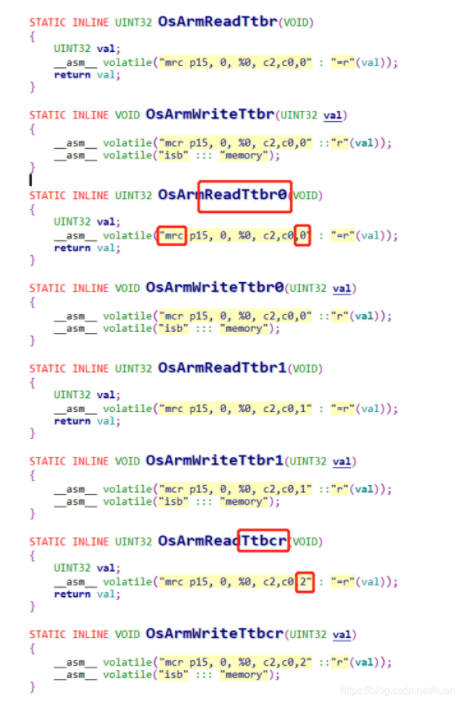

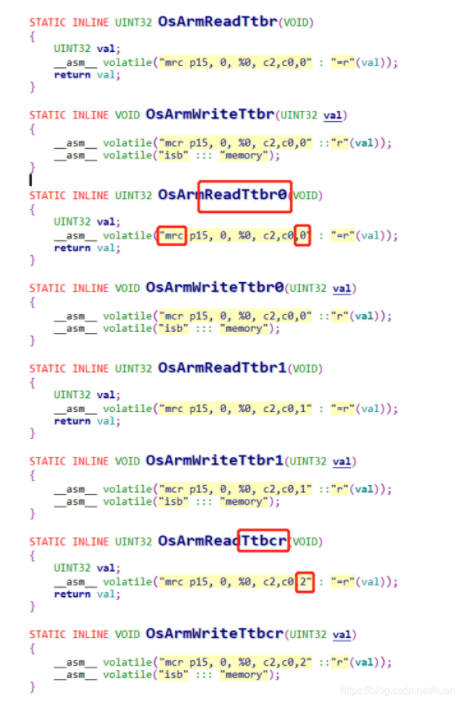

一、ARM中对于存储管理的协处理器CP15CP15可以包含16个32bit的寄存器,分别标记为0~15。但是对于同一个寄存器的物理寄存器可能会对应多个。实际上对于CP15的访问的指令相当简单,只有

2022-05-17 14:19:33

1、通过一段MMU的创建来说明MMU的工作方式下面这段代码是OAL进入kernel Start的一段代码,它也就是wince的页表初始化代码,涉及到两部分内如,分别为二级页表的创建和一级页表的创建

2022-05-18 16:19:41

1、基于二级页表的地址查询方式 上节讨论了当一级描述符[1:0]为01或者11的时候表示这是一种二级页表查询方式,而一级页表描述符仅仅做为二级页表的索引。下面我们将coarse page与fine

2022-05-17 14:29:49

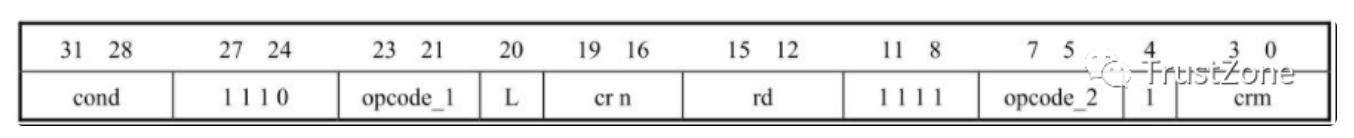

ARM访问MMU,一般cp15就是MMU。 {cond} p#, ,Rd,cn,cm{, }MRC 从协处理器移到ARM7寄存器(L=1)MCR 从ARM7寄存器移到协处理器(L=0){cond

2018-01-28 16:39:44

今天了解了一下单片机的处理器,记录下这些知识点。单片机由处理器、存储器和输入输端口组成的微型控制器。处理器有基于复杂指令集和基于精简指令集两类。而单片机的处理器是基于精简指令集的。常见的Intel

2021-11-29 06:41:51

在基于ARM的嵌入式应用系统中,存储系统通常是通过系统控制协处理器CP15完成的。CP15包含16个32位的寄存器,其编号为0~15。访问CP15寄存器的指令MCR ARM寄存器到协处理器寄存器

2022-05-17 14:38:17

80C186XL16位嵌入式微处理器是Intel公司在嵌入式微处理器市场的上导产品之一,已广泛应用于电脑终端、程控交换和工控等领域。在该嵌入式微处理器片内,集成有DRAM RCU单元,即DRAM刷新

2019-07-29 07:54:57

是程序存储区和数据存储器都是可以放到内存中,统一编码的,而哈弗结构是分开编址的。哈佛架构哪些处理器是哈佛架构、冯诺依曼架构?「哈佛架构」MCU(单片机)几乎都是用哈佛结构,譬如广泛使用的51单片机、典型

2022-08-17 15:20:52

了设计的一大挑战。FPGA可通过在单个FPGA中实现多个视频处理器来提供强大的处理能力。那么现在的挑战就变成了要使数据尽快且高效地从FPGA进出。DDR3存储器系统在大多数情况下可以为这些基于FPGA的系统

2019-05-27 05:00:02

的,CP15协处理器的SCTLR寄存器(系统控制寄存器)的bit[12]控制I-Cache的打开和关闭。I-Cache关闭时,CPU每次取指令都要读主存,所以性能比较低。因此应该尽快打开I-Cache。同样

2016-08-31 16:30:26

按照这句话的意思,协处理器拓展指令只能实现读写操作吗,官方的案例貌似也只是读写指令。那如何用协处理器拓展指令实现更高级运算呢,用内联汇编吗

2023-08-16 07:41:54

的数据类型,所以每个寄存器传送的字数与协处理器有关。ARM产生的存储器地址,但协处理器控制传送的字数。协处理器可能执行一些类型转换作为传送的一部分。例如,浮点协处理器将读取的值转换成它的80位内部表示形式

2022-04-24 09:36:47

`微机原理--数学协处理器[hide][/hide]`

2017-04-30 21:19:48

使用存储器访问的时序分析来揭示否则将被保密的数据。

每种机制都略有不同,有些机制依赖于微体系结构。

在《ARM内核软件概述》一文中介绍了每种变体对ARM内核的影响,以及解决方案和应用方法。

2023-08-25 07:15:47

高速缓存作为中央处理器 (CPU) 与主存之间的小规模快速存储器,解决了两者数据处理速度的平衡和匹配问题,有助于提高系统整体性能。多处理器 (SMP) 支持共享和私有数据的缓存,Cache 一

2021-02-23 07:12:38

本文设计了一种在多处理器系统中的Nios II软核处理器的启动方案,这个方案在外部处理器向Nios II的程序存储器和数据存储器加载数据时,可以控制Nios II处理器的启动。

2021-04-27 06:52:42

数据存储器 FLASH程序存储器 FLASH数据存储器 片内RAM数据存储器16M字节外部数据存储器各有什么区别?特点?小弟看到这段 很晕。ADuC812的用户数据存储器包含三部分,片内640字节的FLASH数据存储器、256字节的RAM以及片外可扩展到16M字节的数据存储器。求助高手。解释一下不同。

2011-11-29 09:50:46

指令操作的协处理器名.标准名为pn,n,为0~15 opcode1协处理器的特定操作码. 对于CP15寄存器来说,opcode1永远为0,不为0时,操作结果不可预知CRd 作为目标寄存器的协处理器

2017-01-12 21:10:30

STM32F103处理器内部存储器结构及映射 STM32F103存储器映像为预定义形式,严格规定了哪个位置使用哪条总线。 STM32F103的程序存储器、数据存储器、寄存器和IO端口被组织到

2021-12-09 07:51:09

状态及程序的运行状态,均为32位,目前只使用了其中的一部分。7种运行模式ARM微处理器支持7种运行模式,分别为:usr(用户模式):ARM处理器正常程序执行模式。fiq(快速中断模式):用于高速数据传输

2018-11-27 19:32:01

mrc p15,0,r1,c1,c0,0s3c2410芯片手册上只是说这个指令是把p15协处理器中c1和c0寄存器里面的值传给r1.但是协处理器的结构是什么样的?c1和c0两个寄存器里的值怎么存到

2015-01-23 14:05:28

ARM920到底有几个协处理器,手册上只看到了CP14,CP15,为什么说是若干个,是不是可以扩展,是不是每个协处理器只有一种功能?

2019-05-22 05:45:26

请问FPGA协处理器有哪些优势?

2021-05-08 08:29:13

ARM 官网文档是如何描述这部分内容,如下图所示。 上面红色框中,第一行翻译为“系统控制协处理器”,我觉得用“系统控制协处理器”还是容易理解,可以接收。它包含了 15 个特殊的寄存器,主要提供“所有

2019-07-29 15:36:26

处理器。这些可配置协处理器可帮助设计人员解决传统ASIC仿真中存在的许多问题,并更省力、更快捷地实现更精确的设计。

2019-07-23 06:24:16

什么是陶瓷传感器?陶瓷传感器的五大应用分别是什么?

2021-05-12 07:08:09

如果协处理器CP15:c1:c0中的1位和22位均为0,则ARM指令ldr的返回值是memory(addr & ~3, 4) ROR ((addr & 3) * 8)。前半句的含义是对4边界向下取整,在本例中就是0x10960,再取其内容就是 0x40302010,后半

2011-09-28 10:14:30 1348

1348 ARM存储系统有非常灵活的体系结构,可以适应不同的嵌入式应用系统的需要。ARM存储器系统可以使用简单的平板式地址映射机制(就像一些简单的单片机一样,地址空间的分配方式是固定的,系统中各部分都使

2017-10-17 16:34:58 1

1 2.4 I/O管理 ARM系统完成I/O功能的标准方法是使用存储器映射I/O。这种方法使用特定的存储器地址。当从这些地址加载或向这些地址存储时,它们提供I/O功能。某些ARM系统也可能有直接存储器

2017-10-18 13:57:03 2

2 ARM核具有协处理器15(CP15)、保护模块和数据和程序存储器。管理单元(MMU)具有表旁侧缓冲器。它有单独的16K字节指令和16KB字节。数据缓存。两者都是与虚拟索引虚拟标签(VIVT)的四路关联。手臂核心也具有8KB RAM(向量表)和64KB ROM。

2018-04-24 15:12:17 0

0 本文首先介绍了ARM处理器特点与主要模式,其次介绍了arm的协处理器有几个,最后介绍了CP14和CP15系统控制协处理器。

2018-04-24 15:34:25 8504

8504 ARM处理器使用协处理器15(CP15)的寄存器来控制cache、TCM和存储器管理。CP15的寄存器只能被MRC和MCR(Move to Coprocessor from ARM Register )指令访问,包含16个32位的寄存器,其编号为0~15。本篇重点讲解其中的 C7C2C13三个寄存器。

2020-11-19 15:34:05 14

14 处理器使用 C15 协处理器的寄存器来控制 cache、TCM(Tightly-Coupled Memory)和存储器管理。CP15 的各个寄存器的概要信息如下图,图片来自官方资料《ARM

2024-02-20 14:28:03 150

150

电子发烧友App

电子发烧友App

评论