PCI总线接口芯片PCI9054及其应用

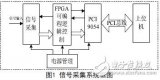

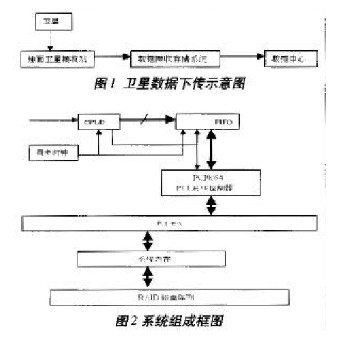

PCI9054是PLX公司推出的一种PCI主模式桥芯片。本文主要介绍了它的特性、功能及应用,说明了以PCI9054作为接口芯片,开发PCI总线扩展卡的硬件框架图,最后给出一个简单的实例。关键词:PCI总线;局部总线;PCI9054

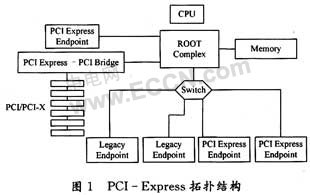

一、 引言 PCI 总线是英特尔公司推出的一种高性能局部总线,其数据总线为32 位,且可扩展成64 位,最大数据传输速率为128- 256MB/ s,远远大于ISA总线5Mbyte/s的速度,是目前使用广泛的一种总线,可以支持突发传送。PCI总线与CPU无关,与时钟频率也无关,因此它可以应用于各种平台,支持多处理器和并发工作。

PCI总线协议比较复杂,用户可以根据具体实际需求选择相应的开发方式,一般,PCI总线开发采用两种方式, 一是采用CPLD来设计控制接口。它的最大好处是比较灵活,用户可以根据自己的需要开发出适合于特定功能的芯片,而不必实现PCI的全部功能。现在有许多生产可编程逻辑器件的厂商,如Xilinx的LogiCore和Altera的AMPP都提供经过严格测试的PCI接口功能模块,用户只要进行组合设计即可。由于PCI总线协议复杂,设计PCI控制接口难度较大,对于产品不大又有时限的工程项目来说,成本巨大,不划算。 二是采用通用PCI接口芯片,例如南京沁恒公司的CH365,AMCC 公司的AMCC S5920、AMCC S5933,PLX 公司的PLX9054、PLX9080 等,通过专用芯片可以实现完整的PCI主控模块和目标模块的功能,将复杂的PCI总线接口转换为相对简单的用户接口,用户只要设计转换后的总线接口即可,它能实现PCI规范所要求的所有硬件接口信号和配置空间寄存器,专用接口芯片具有较低的成本和通用性,能够有效降低接口设计的难度,缩短开发时间, 并能获得较好的数据传输性能。下面将主要介绍PLX公司的PCI9054接口芯片。

二、 概述 PCI9054是由美国PLX公司生产的先进的PCI I/O加速器,采用了先进的PLX数据流水线结构技术,是32位、33MHz的PCI总线主I/O加速器;符合PCI本地总线规范2.2版,突发传输速率达到132MB/s,本地总线支持复用/非复用的32位地址/数据;有M、C、J三种模式;针对不同的处理器及局总线特性可选,尽量减少中间逻辑;具有可选的串行E2PROM接口,本地总线时钟可和PCI时钟异步。PC9054内部有6种可编程的FIFO,以实现零等待突发传输及本地总线和PCI总线之间的异步操作;支持主模式、从模式、DMA传输方式,因其强大的功能可应用于适配卡和嵌入式系统中。PCI 9054是一种性比高的PCI桥路芯片,比PCI9080、PCI9050等性能更优越。

PCI9054内部图

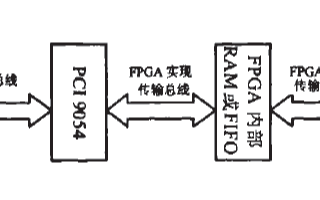

PCI 9054其内部框图如图所示。它采用了先进的PLX数据管道结构技术,是32Bit、33MHz的PCI总线主I/O加速器。 PCI9054主要特性如下: PCI总线接口 PCI总线状态机 FIFO本地总线状态机 本地总线接口 内部寄存器 串行EEPROM初始值 控 制 逻 辑 9054内部图本地总线 PCI总线 ·符合PCI V2.1,V2.2规范,包含PCI电源管理特性。 ·支持VPD(Vital Product Data)的PCI扩展。 ·支持PCI双地址周期,地址空间高达4GB ·具备I2O准备报文单元,完全兼容I2O V1.5规范。 ·提供了两个独立的可编程DMA控制器,每个通道均支持块和Scatter/Gather的DM方式,DMA通道0支持请求DMA方式。 ·在PCI启动模式下,PCI 9054可插入类型1和类型2的配置周期。 ·PCI和Local Bus数据传送速率高达132MB/S。 ·支持本地总线直接接口Motorola MPC850或MPC860系列、Intel i960系列、IBMPPC401系列及其它类似总线协议设备。 ·本地总线速率高达50MHz;支持复用/非复用的32bit地址/数据;本地总线有三种模式;M模式、C模式和J模式,可利用模式选择引脚加以选择。 ·具有可选的串行EEPROM接口。 ·具有8个32bit Mailbox寄存器和2个32位Doorbell寄存器。

三、 功能描述

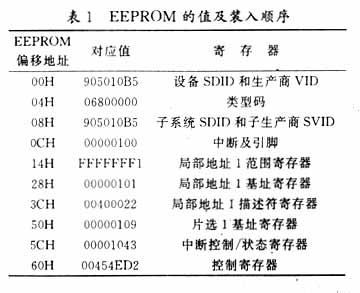

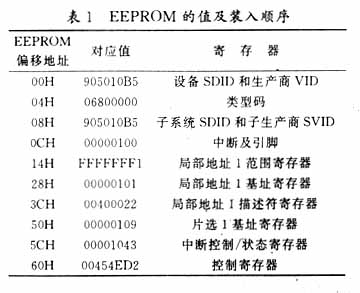

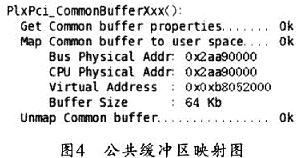

1、PCI9054的物理总线接口

PCI9054提供了三种物理总线接口:PCI总线接口,LOCAL总线接口,及串行EPROM接口。LOCAL总线的数据宽度为32位,时钟频率可达到50MHZ, 并且支持数据预取功能。 PCI9054的总线操作包括PCI总线操作和本地总线操作。对于PCI总线操作,它完全遵守2.2版本PCI规范。PCI9054本地总线支持非多路复用32位地址/数据总线,多路复用32位和8位,16位或32位本地总线设备从属访问,运行速率高达50MHz,可以获得200MB/S的本地总线突发传输速率。 PCI9054的LOCAL总线与PCI总线之间数据传输有三种方式:主模式(Direct Master),从模式(Direct Slave),DMA方式。其内部具有两个DMA数据通道,双向数据通路上各有6个FIFO进行数据缓冲,可同时进行高速的数据接收和发送。8个32位Maibox寄存器可为双向数据通路提供消息传送。PCI9054还提供了一个串行EEPROM接口,容量2K字节。在配置存储器中存放了厂家标示、设备标示以及本地总线的基地址空间、I/O空间、中断控制信号等信息。当初始化时,系统自动将串行EEPROM中的配置参数装入PCI配置寄存器,并根据本地总线对内存、I/O端口和中断的需求统一划分,自动配置。其中本地端寄存器也可以由本地CPU读写,直接进行配置。

2、PCI9054工作模式

PCI9054有3种工作模式,分别为C、M和J模式。M模式主要是针对Motorola公司高性能MPC850/860的应用而设计的,主要应用在电信领域,J模式的接口设计相对比较复杂,通常用的是C模式。 C模式下PCI9054分为PCI Initiator操作和PCI Target操作。在PIC Initiator操作过程中,本地处理器或本地总线主控设备能够直接通过PCI9054访问PCI总线,发起Local-to-PCI的数据传输。而在PCI Target操作过程中,PCI总线主控设备可以以可编程的等待状态、总线宽度和突发传输功能访问PCI9054的三个本地空间(空间0,空间1和扩充ROM空间)。

3、PCI9054的DMA突发模式

PCI9054集成了两个互相独立的DMA通道,每个通道都支持Block DMA和Scatter/Gather DMA,通道0还支持Demand DMA传输方式 Block DMA要求PCI主机或Local主机提供PCI和Local的起始地址、传输字节数、传输方向。主机设定DMA开始位启动数据传输,一旦传输完成,PCI9054设定DMA"传输结束位"结束DMA,如果中断允许位被使能,在传输结束时PCI9054将向主机申请中断。在DMA传输中,PCI9054既是PCI总线的主控器又是Local总线的主控器。 Scatter/Gather DMA要求主机在PCI空间或Local空间设定Descriptor模块,模块包括PCI和Local的起始地址、传输字节数、传输方向和下一个Descriptor模块的地址。PCI9054载入第一个Descriptor模块并发起传输,连续加载下一个模块,直到它侦测到"链结束位"有效,PCI 9054设置"传输结束位",或者申请PCI或Local中断。这种模式下,PCI9054也可以在每个模块加载时有效中断信号结束DMA传输。若Descriptor模块在本地存储空间,可以编程使DMA控制器在每次DMA传输结束后清除传输字节数。

4、PCI9054寄存器

PCI9054内部提供了5种寄存器:PCI配置寄存器,本地端配置寄存器,运行时间RUNTIME寄存器,DMA寄存器和I2O信息寄存器。,下面对PCI配置寄存器和本地端配置寄存器的功能做简要介绍。 PCI配置寄存器也就是我们常说的PCI配置空间,他提供了配置PCI的一些信息。其中VenderID,DeviceID,RevisionID,HeaderType,ClassCode用于PCI设备的识别。 命令寄存器(Command)包含设备控制位,包括允许存储器读写响应等。 状态寄存器(Status)用于记录PCI总线的相关事件。 PCI配置寄存器提供了6个基地址寄存器,这些基地址都是在系统中的物理地址范围内,其中BASE0和BASE1都是用来访问其他配置寄存器的基地址,BASE1是其他配置寄存器映射到PCI端内存的基地址,BASE2是其他寄存器映射到PCI端I/O的基地址。 所以可以通过PCI端内存和PCI端I/O来访问LOCAL配置寄存器与其他3种寄存器。BASE2~5四个空

间提供了访问本地端所接的4个芯片(当然可以少于4个),他们将本地端的芯片通过本地端地址(在LOCAL配置寄存器中设)翻译成PCI的地址,也就是将本地的芯片映射到系统的内存或I/O口。这样使得用程序操作这一段内存(或I/O)实际上就是对本地的芯片操作。 本地端配置寄存器提供了本地端的一些信息

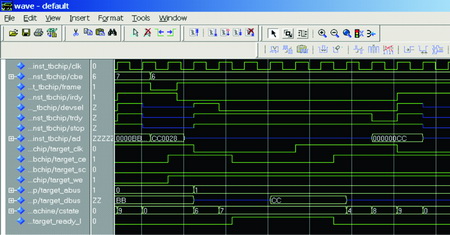

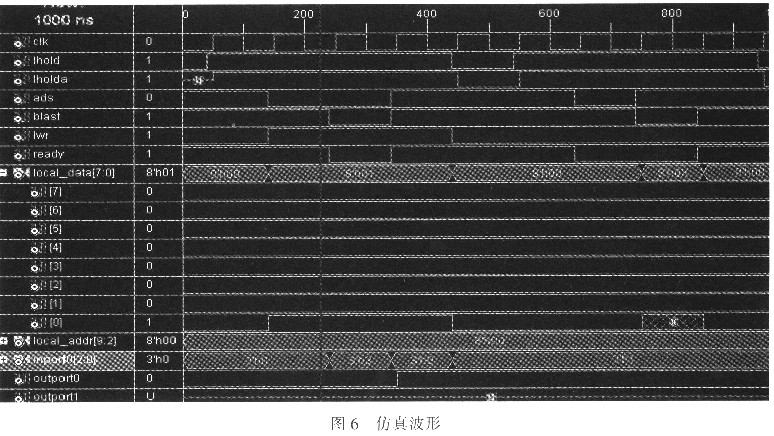

5、C模式部分时序图

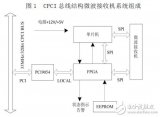

局部总线仲裁(LHOLD和LHOLFA) LCLK:输入信号,时钟信号 LHOLD:输入信号,申请使用本地总线。 LHOLFA:输入信号,对LHOLD应答。 四、 基于PCI9054的PCI接口设计 PCI 9054 以其强大的功能和简单的用户接口,为PCI总线接口的开发提供了一种简洁的方法,设计者只需设计出本地总线接口控制电路,即可实现与PCI总线的高速数据传输。 下图是应用PCI9054作为接口芯片,开发PCI总线扩展卡的总体硬件框架图

下面简单介绍以PCI9054为接口芯片的网卡设计,

1、 硬件设计 8051 RAM8位锁存器029AS

第一部分是9054和PCI插槽间的连接信号线。这些信号包括地址数据复用信号AD[31:0],总线命令信号C/BE[3:0]#和PCI协议控制信号PAR、FRAME#、IRDY#、TRDY#、STOP#、IDSEL、PERR#、SERR#、 第二部分是9054与EEPROM的连线。这里有四根信号线:EESK、EEDO、EEDI、EECS,串行EEPROM的数据通过烧写编程的方式,也可以通过本地CPU直接编程的方式来完成初始化 第三部分就是9054与应用电路的连接。其中LA地址总线、LD数据总线、LBE#字节使能信号和CPLD相连;LW/R读写信号、BLAST#、READY#、ADS#和8051单片机相连。 PCI9054工作在初始化器模式时,要求本地端的总线是32位的。在这里,用CPLD实现将80C51单片机的8位数据与16位地址转换成32位的数据和地址,使用RAM的目的是提高8051的数据传输速度和处理复杂的TCP/IP协议,EEPROM用来保存些相关的信息状态等。

2、软件设计 软件程序主要分为两大部分,一是对PCI9054芯片的PCI端配置寄存器和本地端配置寄存器进行正确的编程配置;二是网络通讯,包括网卡初始化、发送控制和接受控制3部分 五、 结束语 在实践开发中证明,用PCI9054开发各种高速数据采集系统、图象处理系统等PCI设备,能够减少许多相应的外围器件,降低了开发难度,缩短了开发周期,并且使成本有了大幅度的降低。

参考文献: [1 ] 李贵山,戚德虎. PCI局部总线开发者指南.西安:西安电子科技大学出版社,2001 [2 ] PCI Local Bus Specification Revision 2.2 December 18, 1998 [ 3 ] PCI9054 Data Book V2.1,PLX公司.2000 [4 ] 采用8位单片机驱动PCI总线网卡的设计方案,西安理工大学.闫全成,李琦, 杨延西 作者:黄身锞,司职于福州南南信息科技有限公司,从事PCI总线、USB总线开发

电子发烧友App

电子发烧友App

评论