固定逻辑器件和PLD各有自己的优点。,"可编程逻辑器件是逻辑器件产品中增长最快的领域,这主要有两个基本原因。可编程逻辑器件不断提高的单片器件逻辑门数量集成了众多功能,不然

2011-12-05 17:40:10 1248

1248 随着可编程逻辑器件的发展,FPGA的应用已经越来越广泛,且用可编程逻辑器件代替传统的普通集成电路已成为一种发展的趋势。可编程逻辑器件FPGA以其高集成度、高速度、开发周期短、稳定性好而受到了人们

2021-01-04 10:36:00 2066

2066

可编程逻辑器件到底是干什么用的呢,简单的说,就是通过重新写程序,重新注入到这个器件中达到实现其它的功能。最常见的当属电脑了。电脑本身除了加法,减法和简单的逻辑运算四种。比如要是想实现一个功能让电脑

2014-04-15 10:02:54

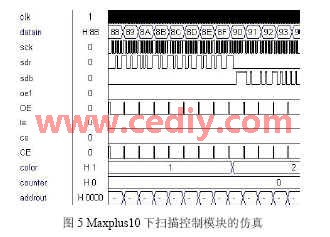

。LCMXO2-640HC-4TG100C可编程逻辑器件FPGA芯片---LED控制解决方案实现普通LED传输条码数据——条码仿真参考设计能够实现普通LED传输条码数据。可驱动LED来传输可供收款机读取的脉冲数

2019-09-20 15:13:30

可编程逻辑器件FPGA/CPLD结构与应用.ppt

2017-01-21 20:34:49

可编程逻辑器件(prog ramm able logic device,PLD)件的功能不是固定不变的,它可根据用户的需要而进行改变,即由编程的方法来确定器件的逻辑功能。可编程逻辑器件自 20 世纪

2019-02-26 10:08:08

芯片上,就可以得到一块专用集成电路。1.1 可编程逻辑器件可编程逻辑器件PLD(Programmable Logic Device)就是一种可以由用户定义和设置逻辑功能的数字集成电路,属于可编程

2021-07-13 08:00:00

可编程逻辑器件实验指导书

2009-09-16 15:11:22

可编程逻辑器件是如何发展的?

2021-04-29 06:23:22

同,只是实现原理略有不同,所以我们有时可以忽略这两者的区别,统称为可编程逻辑器件或PLD/FPGA。PLD是电子设计领域中最具活力和发展前途的一项技术,它的影响丝毫不亚于70年代单片机的发明和使用。PLD

2009-06-20 10:38:05

PLD可编程逻辑器件 英文全称为:programmable logic device 即 PLD。PLD是做为一种通用集成电路产生的,他的逻辑功能按照用户对器件编程来确定。一般的PLD的集成度很高

2021-07-22 09:05:48

约束设计与时序分析6.1 概述6.2 时序约束6.3 约束编辑器6.4 时序分析器6.5 本章小结第7章 可编程逻辑器件的高级设计7.1 概述7.2 宏生成器7.3 增量设计7.4 模块化设计7.5

2012-02-27 14:43:30

` 本帖最后由 eehome 于 2013-1-5 09:47 编辑

XILINX可编程逻辑器件设计技术详解第1章 可编程逻辑器件设计流程导论11.1 设计流程概述11.2 设计输入和综合

2012-04-24 09:18:46

专家都是如何使用超低功耗的复杂可编程逻辑器件(CPLD)的?从他们的嵌入式设计中的I/O子系统中学到了什么?

2021-04-08 06:31:20

为什么复杂可编程逻辑器件需要重新上电才能工作?如何去解决AVR单片机上电复位不可靠的问题?

2021-07-07 06:53:08

的平均销售增长速度。??主要电子设计贸易出版物《EDN》杂志说:"可编程逻辑器件是逻辑器件产品中增长最快的领域,这主要有两个基本原因。可编程逻辑器件不断提高的单片器件逻辑门数量集成了众多

2009-05-29 11:36:21

分享一款不错的基于可编程逻辑器件PLD的数字电路设计方案

2021-04-30 06:34:54

摘要:介绍了可编程逻辑器件在数字信号处理系统中的应用。并运用VHDL语言对采用Lattice公司的ispLSI1032E可编程逻辑器件所构成的乘法器的结构、原理及各位加法器的VHDL作了详细的描述

2019-06-28 06:14:11

CLC5958的内部结构及基本特性CLC5958应用的注意事项有哪些采用可编程逻辑器件和A/D转换器组成的高速数据采集卡的设计方案

2021-04-15 06:50:05

怎么实现基于可编程逻辑器件的数字电路设计?

2021-05-06 08:36:18

本文以乘法器的设计为例,来说明采用可编程逻辑器件设计数字系统的方法。

2021-04-29 06:22:10

数字电子技术-- 可编程逻辑器件[hide][/hide]

2017-03-05 10:51:17

数字电子技术--可编程逻辑器件[hide][/hide]

2017-05-01 22:29:19

本文提出一种利用复杂可编程逻辑器件(Complex Programmable Logic Device,CPLD)设计技术[3]实现专用键盘接口芯片的方案。

2021-04-15 06:55:36

为实现多点校正法,笔者设计了基于复杂可编程逻辑器件的硬件校正实现方案,实验表明,该校正系统可将图像传感器CL512J的非均匀度由40%校正到2%. 因此,多点校正法及其实现系统能在不提高制造工艺和进一步研究光敏元结构的基础上,有效地降低图像传感器的非均匀性,获得较为理想的图像质量。

2021-04-28 06:05:34

清华的可编程逻辑器件实验讲义cpld-2004-8-6-4

2012-08-16 17:06:20

随着智能制造的蓬勃发展进一步推动了智能工业的崛起。制造商及工程师在进行智能化系统设计时,将面临着不断提高性能、突出优势、降低成本、同时实现功能安全等诸多挑战,但同时也给全球可编程逻辑器件厂商带来

2013-04-12 09:57:41

大家好,我想制作一个用单片机编程(c语言)控制的或者直接购买的led控制卡(可编程否?)控制的led显示屏,用于显示一组很长的已知的数字(按时间显示,断电后,每次再来电时继续显示,但要跳过断电的那段时间),程序要自己编的,怎么搞比较便宜啊,多谢?

2019-09-30 04:27:46

如何选择PLC可编程逻辑器件?

2021-04-27 06:39:03

可编程逻辑器件设计

(264页,nlc格式)

2006-03-25 16:41:01 66

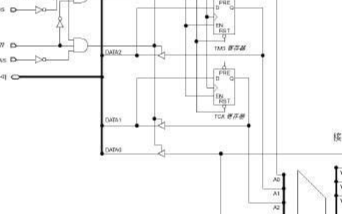

66 熟悉常用逻辑器件的分类;了解常用可编程逻辑器件的内部结构;熟悉可编程逻辑器件的开发流程;掌握MAX+plusII软件。重点:基于MAX+plusII软件进行PLD设计的流程。难点:PLD的

2008-12-01 17:36:45 19

19 XC6SLX100-3FGG484C FPGA现场可编程逻辑器件 XILINX 现场可编程门阵列

2022-08-04 11:37:16

介绍实现单片机与Xilinx公司XC9500系列可编程逻辑器件的读写逻辑功能模块的接口设计,以及Xilinx 公司的XC9500 系列可编程逻辑器件的开发流程。

2009-04-16 09:57:40 23

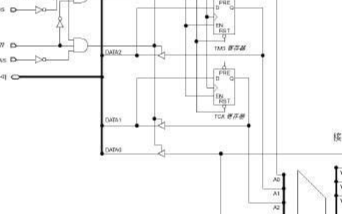

23 介绍了Altera公司生产的可编程逻辑器件EPM7032的内部结构和性能特点,给出了采用自顶向下的层次化设计方法进行自动交通控制系统的设计方案,同时给出了选用EPM7032可编程逻辑器件和M

2009-04-23 16:22:12 60

60 介绍实现单片机与Xilinx公司XC9500系列可编程逻辑器件的读写逻辑功能模块的接口设计,以及Xilinx 公司的XC9500 系列可编程逻辑器件的开发流程。

2009-05-15 14:18:11 28

28 本文通过详细介绍PLD 器件在积分式A/D 转换器数字控制部分的设计,说明可编程逻辑器件(PLD)主要是复杂可编程逻辑器件(CPLD)在数字逻辑系统设计中良好的移植性及稳定性。

2009-08-29 10:17:43 28

28 可编程逻辑器件(programmable logic device,简称PLD)是最大规模甚至超大规模集成电路技术的飞速发展与计算机辅助设计(CAD)、计算机辅助生产(CAM)和计算机辅助测试(CAT)相结合的一种产物

2009-09-01 08:59:53 0

0 一种基于可编程逻辑器件的等精度频率计的设计原理、硬件组成和软件实现关键词:可编程逻辑器等精度 频率 周期 脉宽 占空比

2009-09-07 16:05:34 31

31 可编程逻辑器件应用设计技巧100问:1. 么是.scf?答:SCF文件是MAXPLUSII的仿真文件, 可以在MP2中新建.2. 用Altera_Cpld作了一个186(主CPU)控制sdram的控制接口, 发现问题:要使得s

2009-10-01 19:00:00 41

41 介绍了PLD(可编程逻辑器件) 的技术特点,并针对当前DSP 系统中串并转换器选择调试困难的特点,提出利用PLD 开发DSP 系统中高速串行到高速并行的数据转换传输技术,以简化电路及

2009-12-04 11:49:04 17

17 可编程逻辑器件资料:Cyclone Device Handbook, Volume 1Stratix III Device Handbook, Volume 1MAX II Device Handbook

2009-12-08 16:32:17 0

0 基于复杂可编程逻辑器件(CPLD)的120MHZ高速AD采集卡的设计:介绍了一种基于复杂可编程逻辑器件高速AD采集卡的设计方法,给出了这种采集卡的硬件原理电路和主要的软件设计思路,采用

2010-01-17 09:37:46 39

39 可编程逻辑器件基础及应用实验指导书

《可编程逻辑器件基础及应用》是一门侧重掌握可编程逻辑器件的基本结构和原理的课程。重点是使学生掌握基于可编程

2010-03-24 14:22:46 29

29 基于单片机的复杂可编程逻辑器件快速配置方法

基于SRAM(静态随机存储器)的可重配置PLD(可编程逻辑器件)的出现,为系统设计者动态改变运行电路

2009-03-28 16:47:17 749

749

第三十二讲 可编程逻辑器件及应用第10章 可编程逻辑器件及应用10.1 概述10.1.1 PLD器件的基本结构10.1.2 PLD器件的分类10.1.3 PLD器件的优点一、

2009-03-30 16:37:51 1333

1333

【摘 要】 介绍了可编程逻辑器件的结构、优点,及其在一种高准确度A/D转换器中的应用。设计中采用了通用阵列逻辑芯片GAL16V8。

2009-05-15 22:30:08 781

781

PLC可编程逻辑器件的选择方法

随着PLC的推广普及,PLC产品的种类和数量越来越多,而且功能也日趋完善。近年来,从美国、日本、德国

2009-06-19 13:11:05 748

748

什么是PLD(可编程逻辑器件)

PLD是可编程逻辑器件(Programable Logic Device)的简称,FPGA是现场可编程门阵列(Field Programable Gate Array)

2009-06-20 10:32:32 14281

14281

摘要:介绍实现单片机与Xilinx公司XC9500系列可编程逻辑器件的读写逻辑功能模块的接口设计,以及Xilinx公司的XC9500系列可编程逻辑器件的开发流程。

2009-06-20 13:22:06 1332

1332

基于可编程逻辑器件的数字电路设计

0 引 言

可编程逻辑器件PLD(Programmable Logic De-vice)是一种数字电路,它可以由用户来进行编程和进行配置,利用它可以

2009-11-16 10:46:41 1473

1473

基于AT89S52单片机和ATF1508AS可编程逻辑器件实现LED显示屏的硬件设计

0 引言 LED显示屏主要由电流驱动电路及LED点阵阵列、控制系统和PC端管

2009-12-25 17:44:44 1451

1451

莱迪思半导体公司(NASDAQ: LSCC)今日宣布MachXO™ PLD(可编程逻辑器件)自量产起已经发运了超过7千5百万片。

2011-12-09 08:54:01 663

663 7.1 可编程逻辑器件的基本原理 7.2 可编程逻辑器件的设计技术 7.3 可编程逻辑器件的编程与配置

2012-05-23 10:46:19 142

142 可编程逻辑器件PLD(programmable logic device)是作为一种通用集成电路生产的,其逻辑功能按照用户对器件编程来决定。一般的PLD的集成度很高,足以满足设计一般的数字系统的需要

2012-06-16 22:13:38

Xilinx可编程逻辑器件的高级应用与设计技巧 作者:孙航;出版社:电子工业出版社 内容简介:介绍了Xilinx器件的结构和特性;以及ISE及其辅助设计工具,嵌入式处理器的原理与设计,

2012-11-28 14:18:01 249

249 可编程逻辑器件简介,相关详细学习。

2016-04-26 16:55:36 0

0 可编程逻辑器件学习,压缩包内共10篇学文档

2016-09-02 16:54:40 38

38 可编程逻辑器件FPGA/CPLD结构与应用

2016-12-11 23:38:39 0

0 数字电子技术--可编程逻辑器件

2016-12-12 22:07:22 0

0 数字电子技术-- 可编程逻辑器件

2016-12-12 22:07:22 0

0 由可编程逻辑器件与单片机构成的双控制器

2017-01-12 22:11:56 11

11 基于单片机的复杂可编程逻辑器件快速配置方法

2017-01-18 20:35:09 8

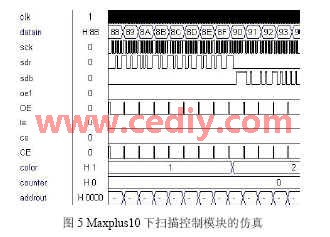

8 用可编程器件实现LED显示屏的硬件扫描控制

2017-01-18 20:40:33 21

21 可编程逻辑器件(书皮)

2022-07-10 14:34:54 0

0 可编程逻辑器件原理、开发与应用

2017-09-19 16:04:49 19

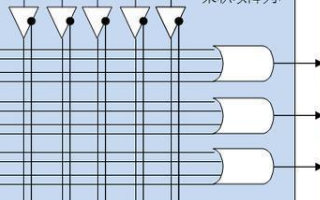

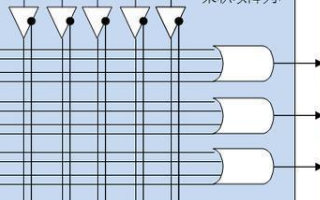

19 根据PLD器件的与阵列和或阵列的编程情况及输出形式,可编程逻辑器件通常可分为4类。第一类是与阵 列固定、或阵列可编程的PLD器件,这类PLD器件以可编程只读存储器PROM为代表。可编程

2017-11-25 01:36:57 3653

3653 在嵌入式系统里除了嵌入式处理器外还会经常使用到可编程逻辑器件,有些可编程逻辑器件在被焊接到印制电路板上之后还可以对其程序进行更新,这种特性称之为“在系统可重编程能力”(In SystemReprogrammability,ISR)。

2018-05-25 11:20:00 1458

1458

Peterson发起这个概念后,它们已经有很长的一段历史了。FPGA和它们最相近的兄弟复杂可编程逻辑器件(CPLD)的区别在于它们能够完成复杂功能的能力,它们就像一个“空白的画布”,它们的功能在之后被描绘在画布上,而不是由厂家预先特定地赋予。

2018-09-25 09:17:00 5847

5847 ,如运行字处理程序或视频游戏。逻辑器件提供特定的功能,包括器件与器件间的接口、数据通信、信号处理、数据显示、时序和控制操作、以及系统运行所需要的所有其它功能。 固定逻辑与可编程逻辑 逻辑器件可分类两大类 - 固定逻辑器件和可编程逻

2019-02-23 14:42:01 1471

1471 可编程逻辑器件即PLD。PLD是做为一种通用集成电路产生的,他的逻辑功能按照用户对器件编程来确定。一般的PLD的集成度很高,足以满足设计一般的数字系统的需要。

2019-12-11 07:03:00 2075

2075

FPGA可能确实很性感(以工程师的说法),但它们并不是唯一的可编程逻辑器件;其它设备也可以用单一设备提供一系列功能。看看来自Cypres半导体公司的“片上可编程系统”(PSoC)架构吧,它是工业上唯一一个在单片上结合了高性能模拟模块、可编程PLD、内存以及微控制器的可编程嵌入式SOC,并且功耗很低。

2019-08-28 08:35:50 3097

3097 CPLD(复杂可编程逻辑器件),它是从PAL和GAL器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。

2019-08-09 14:12:24 4769

4769

可编程逻辑器件(FPGA)一直以其设计灵活性以及现场可编程特性在市场上稳稳固守着一席之地,随着半导体制造工艺的进步,器件集成度越来越高,其应用也日益复杂。,

2019-11-21 14:51:27 533

533 在嵌入式系统里除了嵌入式处理器外还会经常使用到可编程逻辑器件,有些可编程逻辑器件在被焊接到印制电路板上之后还可以对其程序进行更新,这种特性称之为“在系统可重编程能力。

2020-01-26 09:29:00 1294

1294

可编程逻辑器件(ProgrammableLogicDevice,PLD)是一种半定制集成电路,在其内部集成了大量的门和触发器等基本逻辑单元电路(LEs),用户通过编程来改变PLD内部电路的逻辑关系或连线,就可以得到所需要的设计电路。

2020-06-04 14:26:27 7377

7377 可编程逻辑器件(PLD)是20世纪70年代发展起来的一种新型逻辑器件,是目前数字系统设计的主要硬件基础。根据可编程逻辑器件结构、集成度以及编程工艺的不同,它存在以下不同的分类方法。

2020-06-10 17:52:19 26761

26761 可编程逻辑器件PLD(Programmable Logic Device)就是一种可以由用户定义和设置逻辑功能的数字集成电路,属于可编程 ASIC。

2020-09-04 17:02:17 2382

2382 可编程逻辑器件的设计方法经历了布尔等式,原理图输入,硬件描语言这样一个发展过程。随着设计的日益复杂和可编程逻辑器件规模的不断扩大,人们不停地寻求更加抽象的行为级设计方法,以便在尽可能短时间内完成自己的设计构思。

2020-09-11 18:41:00 1114

1114 可编程逻辑器件(PLD--ProgrammableLogic Device):器件的功能不是固定不变的,而是可根据用户的需要而进行改变,即由编程的方法来确定器件的逻辑功能。

2021-01-21 17:04:00 33

33 可编程逻辑器件PLD课件下载

2021-08-13 10:58:22 31

31 FPGA CPLD可编程逻辑器件的在系统配置方法(深圳市村田电源技术有限公司)-FPGA CPLD可编程逻辑器件的在系统配置方法

2021-09-18 10:51:20 13

13 在过去的十年中,可编程逻辑器件(PLD)市场不断增长,对PLD的需求不断增加。具有可编程特性且可编程的芯片称为PLD。PLD也称为现场可编程器件(FPD)。FPD用于实现数字逻辑,用户可以配置集成电路以实现不同的设计。这种集成电路的编程是通过使用EDA工具进行特殊编程来完成的。

2022-03-22 12:36:24 5304

5304 电可编程逻辑器件(Electrically Programmable Logic Device,EPLD)是指采用电信号的可擦可编程逻辑器件。

2022-08-22 18:12:37 935

935 常见的可编程逻辑器件分为FPGA、EPLD(CPLD)。下面简单介绍两类器件的结构和区别。

2023-03-24 14:18:28 798

798

可编程逻辑器件 (Programmable Loeie Device,PLD)是一种用户编程实现某种逻辑功能的逻辑器件,主要由可编程的与阵列、或阵列、门阵列等组成,可通过编程来实现一定的逻辑功能

2023-06-06 15:35:59 659

659

可编程逻辑器件 (Programmable Loeie Device,PLD)是一种用户编程实现某种逻辑功能的逻辑器件,主要由可编程的与阵列、或阵列、门阵列等组成,可通过编程来实现一定的逻辑功能。

2023-06-06 15:37:45 404

404

可编程逻辑阵列(Programmable Logic Array, PLA):PLA是最早的可编程逻辑器件之一,由与非门阵列和或门阵列组成,通过编程配置来实现特定的逻辑功能。

2023-07-04 15:28:22 1360

1360 可编程逻辑器件(Programmable Logic Device,PLD)是一类集成电路器件,可以根据用户的需求进行编程和配置,以实现特定的逻辑功能。它们具有可编程的逻辑门、时钟资源和互连结构,可以替代传统的固定功能逻辑芯片,提供更灵活和可定制的解决方案。

2023-09-14 15:25:55 1100

1100 可编程逻辑器件是一种集成电路,具有可编程功能的特性。它们可以根据用户的需求进行编程,从而实现不同的逻辑功能。

2024-02-26 18:24:03 576

576

电子发烧友App

电子发烧友App

评论