DMA(Direct Memory Access)控制器是一种在系统内部转移数据的独特外设,可以将其视为一种能够通过一组专用总线将内部和外部存储器与每个具有DMA能力的外设连接起来的控制器。它之所以属于外设,是因为它是在处理器的编程控制下来 执行传输的。

DMA控制器特点:

8个独立的通道,4个可用于PL—PS间数据管理,每个通道有1024Byte的MFIFO;

使用CPU_2x 时钟搬运数据,CPU_2x = (CPU frq/6)*2;

执行自定义内存区域内的DMA指令运行DMA;

AHB控制寄存器支持安全和非安全模式;

每个通道内置4字Cache;

可以访问SoC的以下映射物理地址:

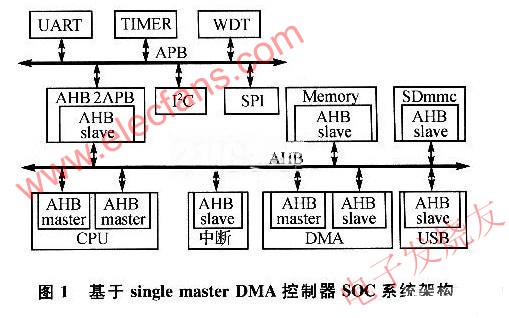

DDR、OCM、PL、Linear QSPI Read、SMC和M_AXI_GP设备,访问设备的互联结构如图1所示。

图一

从图1可以看出DMA控制器可以访问连接到Central Interconnect上的所有设备,并提供了四个通道的外设管理接口可用于控制PL的数据搬运。

dma控制器组成:

一个DMA控制器,实际上是采用DMA方式的外围设备与系统总线之间的接口电路,这个接口电路是在中断接口的基础上再加DMA机构组成。习惯上将DMA方式的接口电路称为DMA控制器。

(1)内存地址计数器:用于存放内存中要交换的数据的地址。在 DMA传送前,须通过程序将数据在内存中的起始位置(首地址)送到内存地址计数器。而当 DMA 传送时,每交换一次数据,将地址计数器加“1”,从而以增量方式给出内存中要交换的一批数据的地址。

(2)字计数器:用于记录传送数据块的长度(多少字数)。其内容也是在数据传送之前由程序预置,交换的字数通常以补码形式表示。在DMA传送时,每传送一个字,字计数器就加“1”。当计数器溢出即最高位产生进位时,表示这批数据传送完毕,于是引起DMA控制器向CPU发出中断信号。

(3)数据缓冲寄存器:用于暂存每次传送的数据(一个字)。当输入时,由设备(如磁盘)送往数据缓冲寄存器,再由缓冲寄存器通过数据总线送到内存。反之,输出时,由内存通过数据总线送到数据缓冲寄存器,然后再送到设备。

(4)DMA请求”标志:每当设备准备好一个数据字后给出一个控制信号,使“DMA

请求”标志置“1”。该标志置位后向“控制/状态”逻辑发出DMA请求,后者又向CPU发出总线使用权的请求(HOLD),CPU响应此请求后发回响应信号HLDA,“控制/状态”逻辑接收此信号后发出DMA响应信号,使“DMA 请求”标志复位,为交换下一个字做好准备。

(5)控制/状态”逻辑:由控制和时序电路以及状态标志等组成,用于修改内存地址计数器和字计数器,指定传送类型(输入或输出),并对“DMA请求”信号和CPU响应信号进行协调和同步。

(6)中断机构:当字计数器溢出时,意味着一组数据交换完毕,由溢出信号触发中断机构,向CPU提出中断报告。

DMA控制器接口函数

主要作用是配置DMA控制器并启动相应传输

s3c2440中关于公共DMA控制器的函数提供有:

s3c2410_dma_config()

s3c2410_dma_ctrl()

s3c2410_dma_enqueue()

s3c2410_dma_devconfig()

s3c2410_dma_set_buffdone_fn()

s3c2410_dma_request()

s3c2410_dma_free()

一般使用的顺序如下:

request =》set_buffdone_fn=》 devconfig =》 config =》 enqueue =》 ctrl =》 free

1、int s3c2410_dma_request(unsigned int channel, struct s3c2410_dma_client *client, void *dev)

2、static inline void s3c2410_dma_buffdone(struct s3c2410_dma_chan *chan, struct s3c2410_dma_buf *buf, enum s3c2410_dma_buffresult result)

设置相应的dma通道完成一次dma传输后的回调函数

3、int s3c2410_dma_devconfig(int channel, enum s3c2410_dmasrc source, unsigned long devaddr)

source: S3C2410_DMASRC_HW: source is hardware

S3C2410_DMASRC_MEM: source is memory

devaddr: physical addr of source

4、int s3c2410_dma_config(unsigned int channel, int xferunit)

根据xferunit设置通道的控制寄存器DCONx

xferunit为每次传输的数据大小:0:byte 1:half word 2:word

5、dma_alloc_coherent

DMA要求使用non-cached, 物理地址连续的内存。

将对应的内核虚拟地址转化为物理地址,供给后面的s3c2410_dma_enqueue函数使用。

6、int s3c2410_dma_enqueue(unsigned int channel, void *id, dma_addr_t data, int size)

7、int s3c2410_dma_ctrl(unsigned int channel, enum s3c2410_chan_op op)

8、int s3c2410_dma_free(unsigned int channel, struct s3c2410_dma_client *client)

DMA控制器接口函数使用实例

s3c2440 DMA datasheet

s3c2440 DMA控制器支持4种情况的DMA传输:

a. source and destination are in the system bus

b. source in the system bus while destination in the peripheral bus

c. source in the peripheral bus while destination in the system bus

d. source and destination are in the peripheral bus

但是在arch/arm/plat-s3c24xx/dma.c的函数s3c2410_dma_devconfig中却只实现了b和c两种情况。

s3c2440有4个DMA channel,每个channel都有DISC/DISCC/DIDST/DIDSTC寄存器,DISC和DIST可以填入不同source类型(具体参考S3c2440 Datasheet Table 8-1),除此之外还能填入内存的物理地址作为source或destination。

和传输相关的3个参数:

TSZ:DCON[28],0:unit模式:一次transfer1个data size,burst模式:一次transfer4个data size

DSZ:DCON[21:20],0:data size is BYTE,1:data size is Half WORLD,0:data size is WORLD

TC:DCON[19:0],transfer count

传输的数据量=TC * (DSZ * 8) * TSZ

request source: DCON[23]

0:S/W request mode, DMA is triggered by setting SW_TRIG bit of DMASKTRIG control register

1:DMA source selected by bit[26:24] triggers the DMA operation

service mode:DCON[27]

0:single service mode,一次DMA请求完成一次原子操作,等待下一次请求

1:whole service mode,一次DMA请求完成一批原子操作,当TC=0表示完成一次whole service

电子发烧友App

电子发烧友App

评论