AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一种总线协议, Xilinx从 6 系列的 FPGA 开始对 AXI 总线提供支持,目前使用 AXI

2020-12-04 12:22:44 6179

6179

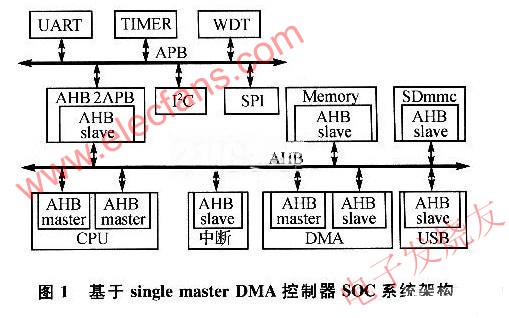

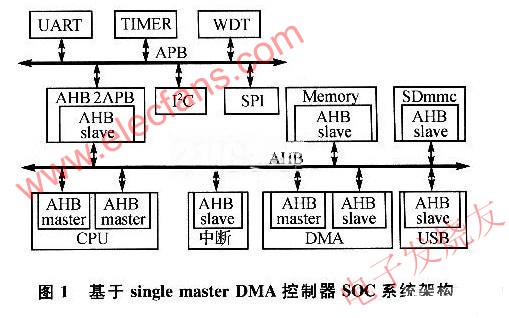

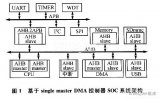

断给中断控制器; 5. 拥有8个DMA触发事件并且可以编码控制; 6. 128个(64bit)的MFIFO,在传输的时候读写端可写入到此FIFO; 7. 支持任意内存到内存的传输; 整个系统中的DMA

2020-12-05 10:17:17 3606

3606 前面一节我们学会了创建基于AXI总线的IP,但是对于AXI协议各信号的时序还不太了解。这个实验就是通过SDK和Vivado联合调试观察AXI总线的信号。由于我们创建的接口是基于AXI_Lite协议

2020-12-23 15:32:37 2169

2169 构成的传输数据的通道, 一般由数据线、地址线、 控制线构成。 Xilinx从6系列的 FPGA 开始对 AXI 总线提供支持, 此时 AXI 已经发展到

2020-12-25 14:07:02 2957

2957

一、AXI DMA介绍 本篇博文讲述AXI DMA的一些使用总结,硬件IP子系统搭建与SDK C代码封装参考米联客ZYNQ教程。若想让ZYNQ的PS与PL两部分高速数据传输,需要利用PS的HP

2020-12-31 09:52:02 7165

7165

利用AXI-DMA批量发送数据到DMAinit_intr_sys函数分析

2021-03-10 06:57:39

AXI总线学习AXI协议的主要特征主要结构通道定义读写地址通道读数据通道写数据通道写操作回应信号接口和互联寄存器片基本传输Read burstOverlapping read burstWrite

2022-02-09 07:17:23

1 DMA系统简介DMA(direct memory access)是一种外设与存储器或者存储器与存储器之间直接传输数据的方式,在进行DMA存取时,CPU让出总线控制权,不在采用输入输出指令的方法

2021-07-26 08:11:30

DMA控制器8237A是什么工作原理?DMA控制器8237A的引脚功能及工作方式是什么?

2021-09-18 06:48:59

本帖最后由 yyeee312 于 2015-11-12 15:17 编辑

DMA控制器是一种在系统内部转移数据的独特外设,可以将其视为一种能够通过一组专用总线将内部和外部存储器与每个具有DMA

2015-11-04 22:50:56

DMA控制器的主要用途是什么?GPIO引脚的I/O端口有何作用?

2022-01-25 06:59:37

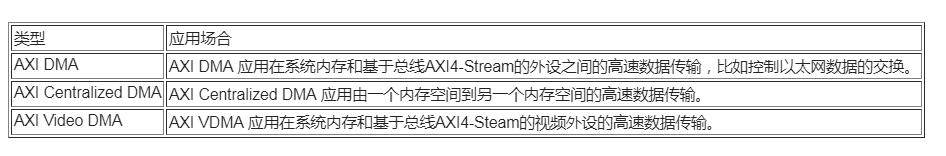

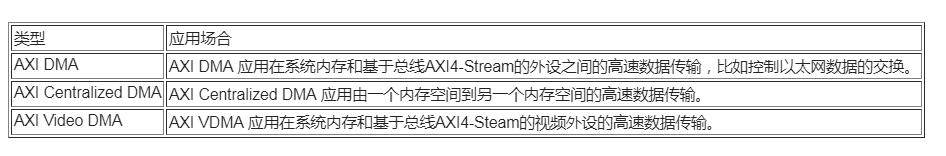

;独立的控制和状态流通道,提供相关的包信息;DMA的中断与系统中断控制器相连。 (2) AXI Centralized DMA 图4‑41 AXI CDMA 在此系统中,AXI CDMA与处理器

2020-12-23 17:48:04

大家好, 我通过dma tx通道(AXI DMA0)将数据发送到fpga。几秒钟后,我希望通过DMA rx通道接收某些字节。执行下面的代码后(请参考CODE1 :)我正在检查tx通道的第1位状态

2020-04-14 07:31:36

。

•适用于具有高初始访问延迟的内存控制器。

•提供了实现互连架构的灵活性。

•向后兼容AHB和APB接口。

AXI协议的主要特点是:

•独立的地址/控制和数据阶段。

•支持使用字节选通进行未对齐的数据传输

2023-08-02 09:44:08

ARM处理器中有些总线APB AHB AXI 3 AXI 4,他们的有什么不同,各自作用?

2023-10-24 07:16:36

CoreLink DMA-350是一款具有AMBA®AXI5接口的直接内存访问控制器(DMAC),

它提供快速存储器到存储器、外围设备到存储器、存储器到外围设备拷贝,以及

多个通道上的外设到外设能力

2023-08-02 08:03:53

DMA-330周期型号是一款高性能、面积优化的SDRAM或移动SDR内存控制器,可为DMA传输提供AXI接口。

它由两个APB接口编程和控制,一个在TrustZone安全模式下运行,另一个在非安全

2023-08-16 06:41:45

EtherCAT总线运动控制器硬件是如何进行接线的?EtherCAT总线运动控制器有哪些参数设置?

2021-07-15 13:02:24

的理解:1)DMA连接到IP总线。2)OCRAM连接到AXI64总线。3) ITCM和DTCM连接到TCM接口。是否可以将 DMA 缓冲区放在 OCRAM 中,将任务的缓冲区放在 DTCM 或 ITCM

2023-04-04 07:09:50

我已经通过AXI互连将用于PCI Express的DMA子系统连接到DDR4控制器IP。然而,这是在块设计之外完成的。实际上我没有使用块设计。如果我使用块设计,地址编辑器将出现在一个选项卡中,可以指定每个块的AXI地址。但是如果没有块设计,我该如何打开地址编辑器?

2020-05-08 07:30:19

PL341内存控制器是一款高性能、面积优化的DDR2 SDRAM内存控制器,兼容高级微控制器总线架构(AMBA)AXI协议。

有关AXI协议的详细说明,请参阅AMBA AXI协议规范。

本节总结了周期模型的功能与硬件的功能,以及周期模型的性能和准确性。

2023-08-12 06:01:49

µDMAC是一种符合高级微控制器总线架构(AMBA)的片上系统(SoC)外围设备,由ARM开发、测试和许可。

它是一个非常低的门计数DMA控制器,与AMBA AHB Lite协议兼容

2023-08-02 15:36:45

PL340内存控制器是一款高性能、面积优化的SDRAM或移动SDR内存控制器,兼容高级微控制器总线架构(AMBA)AXI协议。

有关AXI协议的详细说明,请参阅AMBA AXI协议规范。

本节总结

2023-08-12 06:25:03

的请求,还有一个仲裁器来协调各个DMA请求的优先权。DMA 控制器和Cortex-M3核共享系统数据总线执行直接存储器数据传输。当CPU和DMA同时访问相同的目标(RAM或外设)时,DMA请求可能会

2015-01-13 14:02:03

你好,我正在尝试深入学习 DMA,但在某些时候我很困惑。它是关于总线矩阵和仲裁机制。STM32F446RE中有2个DMA控制器,每个控制器有1条外设总线和1条内存总线。问题不是关于 DMA 的内存

2022-12-27 06:34:33

我正在使用ZC706套件和ISE14.4。我在PL中使用XPS生成AXI.DDR控制器。 AXI.DDR控制器的S_AXI总线通过AXI互连连接到M_AXI_GP1。当我在板上运行它时,我看到

2019-09-10 07:58:12

stm32的dma控制器有多少个通道,DMA简介直接存储器存取(DMA)用来提供在外设和存储器之间或者存储器和存储器之间的高速数据传输。无须CPU干预,数据可以通过DMA快速地移动,这就节省了CPU

2021-08-05 07:29:16

DMA控制器的主要特性有哪些?DMA控制器通道的配置过程该怎样去完成呢?

2021-12-13 06:12:53

这篇应用笔记描述了怎么使用STM32F101xx 和 STM32F103xx的直接存储器访问(DMA)控制器。STM32F101xx和STM32F103xx的DMA控制器、CortexTM-M3内核

2023-10-10 08:20:48

它们如何用于接口SoC组件。图6.AXI互连(AXI4规范)结论在本文中,我们介绍了高级微控制器总线体系结构或AMBA。AMBA是一个开放标准,概述了SoC上的组件如何快速有效地交换数据。AMBA

2020-09-28 10:16:11

的控制和状态流通道,提供相关的包信息;DMA的中断与系统中断控制器相连。(2) AXI Centralized DMA图4‑41 AXI CDMA在此系统中,AXI CDMA与处理器等设备通过AXI

2022-10-14 15:23:41

世界的新手。vivado hls用户指南(Ug902)告诉我,对于ap_memory它不需要总线进行通信,而是一个bram控制器可以完成将数据“馈送”到输入的工作,所以我添加了一个Bram控制器IP

2019-02-28 13:47:30

我需要设计一个Zynq(可能是Zynq-7030)主板,支持ARM处理器的SATA硬盘驱动器。我想知道是否可以用GTX收发器实现SATA控制器并将其连接到芯片中的AXI总线。是否有任何参考设计或评估板支持此功能?

2020-07-29 10:28:58

STM32F4的DMA控制器有何作用?如何去实现STM32F4的DMA控制器的收发配置呢?

2021-12-07 07:06:57

我能拿到相应的附件的控制器板吗?1.PSOC3控制器板-CY8C34 46AXI099具有USB接口FRC连接器取出的所有GPIO2.PSOC5控制器板-CY8C5668 AXI-060具有USB接口FRC连接器取出的所有GPIO请向我提供上述建议。谢谢和问候,卡马拉吉

2019-07-31 11:41:36

`1、在开发zynq工程时遇到多个axi_hp总线读写ddr时,总线锁死。现象就是axi_hp的wready信号一直为低。架构图: 2、应用write1、wrtie2、read1同时并行读写ddr3

2020-04-15 21:57:28

CAN总线及控制器工作原理是什么?流接口驱动程序工作机制是怎样的?怎样去设计CAN总线控制器sJAl000驱动程序?

2021-04-27 06:41:09

EtherCAT总线扩展模块包含哪些?怎样去使用正运动技术运动控制器EtherCAT总线?

2021-09-27 08:34:04

嗨,我正在使用Zedboard来测试我们的设计。例如,我们正在尝试使用AXI_DMA,带有AXI接口的FIFO,带有AXI接口的自定义逻辑来建立设计。我们正在尝试执行简单的环回测试。当我们进行此测试

2019-03-08 13:57:18

直接存储器存取DMACPU太忙了,那DMA你来帮我吧,这样很多事情CPU就不用停下来去管了。在DMA模式下,CPU只须向DMA控制器下达指令,让DMA控制器来处理数据的传送,数据传送完毕再把信息反馈

2021-12-09 06:00:30

eXtensibleInterface)协议是一种面向高性能、高带宽系统设计的总线协议,能够满足各种高速系统的总线互联。AXI协议的主要特点有:●独立的地址、控制和数据接口●支持使用字节选通的不对齐数据的传输

2019-05-06 16:55:32

总线控制器是如何进行验收滤波的?

2021-05-18 06:28:38

你好,我正在设计一个 PMSM 电机控制器,我有一个问题,PMSM控制器需要直流总线纹波补偿吗?

2024-01-22 07:56:17

通过 DMA 控制器进行介质访问控制 (MAC)STM32F4xx系列控制器内部集成了一个以太网外设,它实际上是一个通过DMA控制器进行介质访问控制(MAC),它的功能就是实现MAC 层的任务。借助

2021-08-13 08:47:19

DMA(Direct Memory Access)的概念DMA方式不用处理器干预完成M与I/O间数据传送。DMA期间系统总线由其它主模块控

2008-12-09 11:03:56 50

50 引言

DMA(Direct Memory Access,直接存储器存取)是一种快速传送数据的机制。DMA控制器能够有效替代微处理器的加载/存储指令,显著提高系统的并行能力。DMA是在

2010-09-08 11:08:36 2281

2281

在以SD卡为图像存储器件的图像协处理器中,基带芯片和SD卡控制器在速度上的差异经常会导致数据传输错误。为解决此问题,设计了一种可适应多种时序情况的DMA控制器。该DMA控制器的状态机,一方面对基带芯片和SD卡控制器的操作请求进行仲裁,在响应基带芯片请

2011-01-15 17:06:20 0

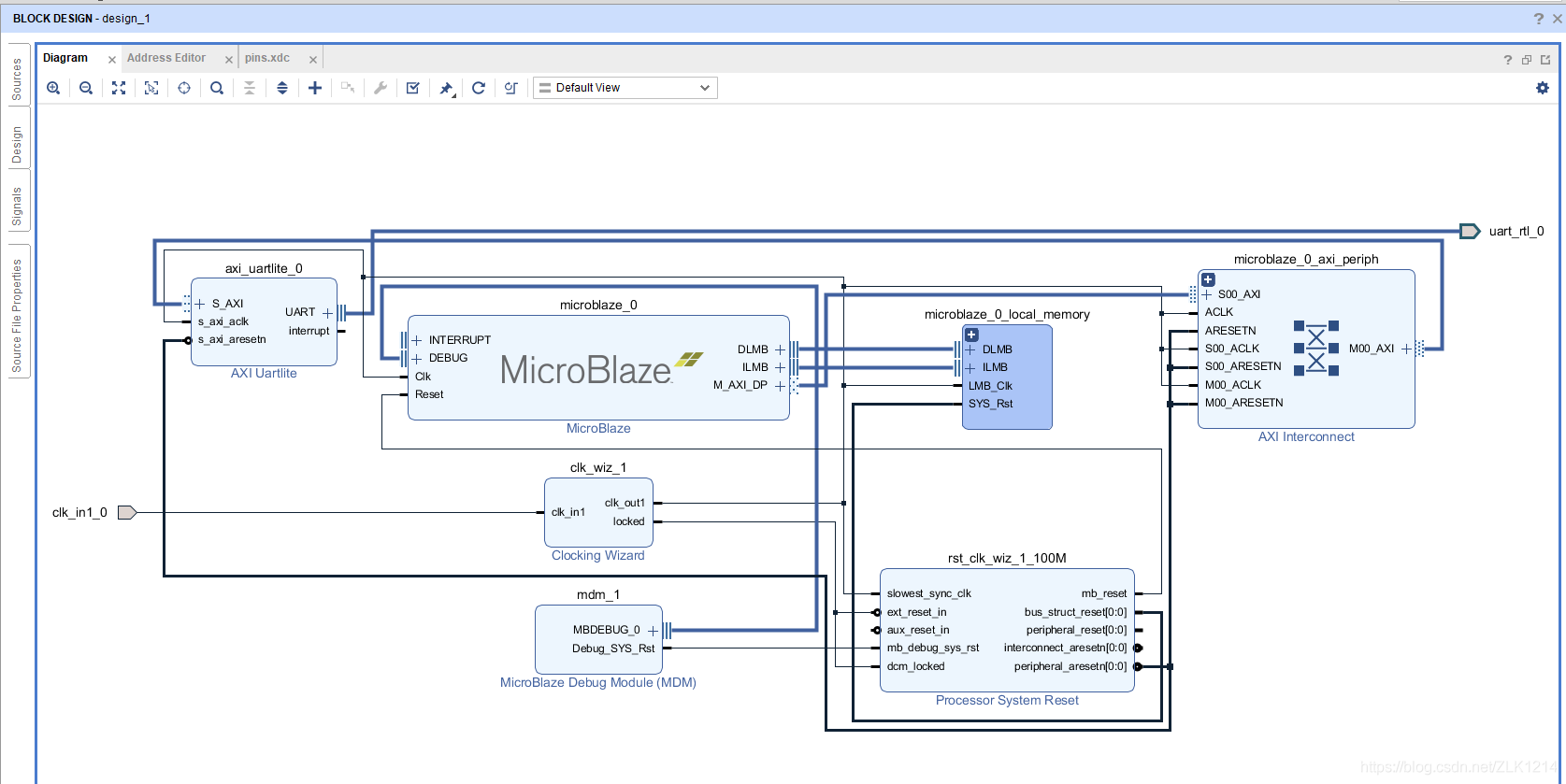

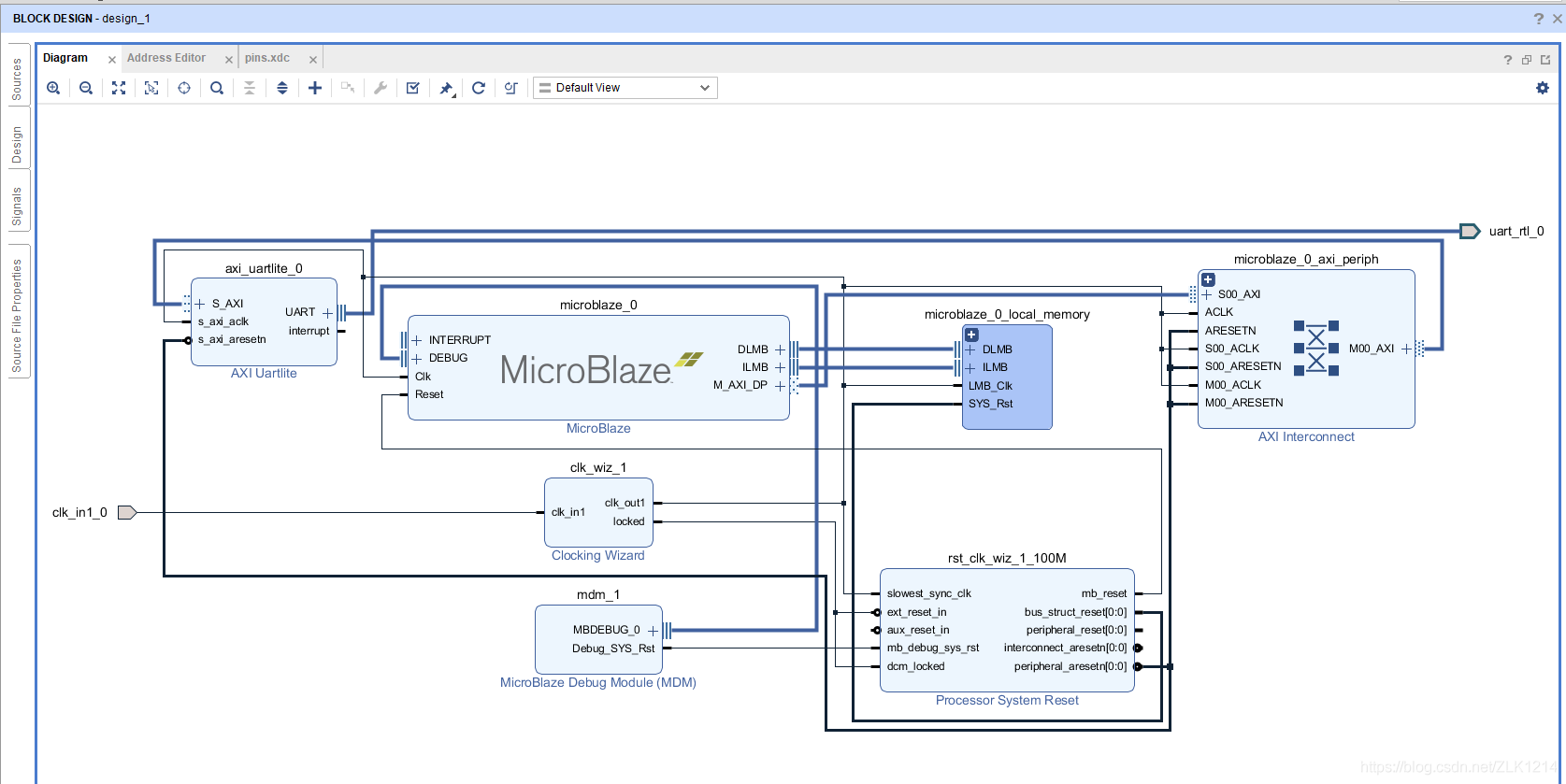

0 目的是利用嵌入在Xilinx FPGA中的MicroBlaze核实现基于AXI总线的双核嵌入式系统设计以及共享实现LED灯的时控.

2012-03-09 14:17:01 91

91 针对大数据量的串口间通信,在常规的UART串行数据通信的基础上,结合Cortex-M3微控制器中DMA控制器的作用,实现DMA控制的UART串口数据包收发。设计链表项缓存,最终实现DMA的分散/聚集

2012-04-20 10:54:07 46

46 AMBA AXI 总线学习笔记,非常详细的AXI总线操作说明

2015-11-11 16:49:33 11

11 上周的博客中我们完成了硬件的搭建,并且把硬件部分导入到SDK,见Adam Taylor’s MicroZed Chronicles Part 67: AXI DMA II,下一步通过写一个简单的程序

2017-02-08 05:53:11 303

303

上周的博客中我们学习了Zynq SoC的AXI DMA,我解释了怎样利用AXI DMA控制器将数据从PL搬运到PS。在本期博客中我们将学习怎样完成硬件的搭建。 首先我们要更深入的了解一下AXI

2017-02-08 08:10:39 286

286 本文主要介绍zynq linux AXI DMA传输步骤教程,具体的跟随小编一起来了解一下。

2018-07-08 05:46:00 29549

29549

DMA 控制器在外设与主存之间直接传送数据期间,完全代替 CPU 进行工作。

2017-09-19 16:11:03 6

6 AXI总线的MicroBlaze双核SoPC系统设计

2017-10-31 08:54:44 8

8 DMA控制器是常见的总线设备之一,很多厂商都有自己的DMA控制器IP核。比如嵌入式处理器的龙头ARM公司就有自己的DMA控制器解决方案提供给客户,另外像Freescale,Fujitsu等芯片

2017-12-06 13:41:59 3329

3329

介绍一种基于PCI总线的高效链式DMA控制器的设计与实现,用于高速宽带的计算机外设接口。利用Altera公司的PCI核——PCI_MT32搭建基于此控制器的数据采集平台,并成功应用在DVB数据接收卡中。

2017-12-06 13:56:13 2782

2782

DMA(Direct Memory Access)控制器是一种在系统内部转移数据的独特外设,可以将其视为一种能够通过一组专用总线将内部和外部存储器与每个具有DMA能力的外设连接起来的控制器。它之所以属于外设,是因为它是在处理器的编程控制下来 执行传输的。

2017-12-06 19:19:12 3458

3458 DMA控制器是一种在系统内部转移数据的独特外设,可以将其视为一种能够通过一组专用总线将内部和外部存储器与每个具有DMA能力的外设连接起来的控制器。它之所以属于外设,是因为它是在处理器的编程控制下来 执行传输的。

2017-12-07 08:51:27 2024

2024

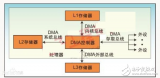

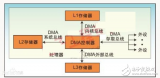

为了具体介绍本多通道 DMA 控制器的设计方案,下面首先对基于 Crossbar 的多通道 DMA 控制器的工作原理进行详细分析,接着具体说明各个模块的设计实现,然后对设计进行验证和分析比较实验结果,并进行总结。

2017-12-07 09:37:22 4585

4585

DMA既可以指内存和外设直接存取数据这种内存访问的计算机技术,又可以指实现该技术的硬件模块(对于通用计算机PC而言,DMA控制逻辑由CPU和DMA控制接口逻辑芯片共同组成,嵌入式系统的DMA控制器内建在处理器芯片内部,一般称为DMA控制器,DMAC)。

2017-12-07 10:23:24 15810

15810

DMA(Direct Memory Access)控制器是一种在系统内部转移数据的独特外设,可以将其视为一种能够通过一组专用总线将内部和外部存储器与每个具有DMA能力的外设连接起来的控制器。它之所以属于外设,是因为它是在处理器的编程控制下来 执行传输的。

2017-12-07 14:43:14 3368

3368

DMA控制器是一种在系统内部转移数据的独特外设,可以将其视为一种能够通过一组专用总线将内部和外部存储器与每个具有DMA能力的外设连接起来的控制器。它之所以属于外设,是因为它是在处理器的编程控制下来 执行传输的。

2017-12-07 15:41:09 3168

3168

DMA既可以指内存和外设直接存取数据这种内存访问的计算机技术,又可以指实现该技术的硬件模块(对于通用计算机PC而言,DMA控制逻辑由CPU和DMA控制接口逻辑芯片共同组成,嵌入式系统的DMA控制器内建在处理器芯片内部,一般称为DMA控制器,DMAC)。

2017-12-07 16:08:38 5155

5155

基于前面对DMA控制器工作流程的详细分析。运用SystemC 语言,建立DMA控制器的Cye le-Accurat级参考模型。控制器由以下几个模块组成:寄存器赋值、状态转换。输出模块和顶层模块。具体工作过程可以参考如图3所示的有限状态机

2017-12-07 16:21:12 2350

2350

1、AXI 总线通道,总线和引脚的介绍 AXI接口具有五个独立的通道: (1)写地址通道(AW):write address channel (2)写数据通道( W): write data

2018-01-05 08:13:47 9601

9601

本文实现的基于FPGA的PCIe总线接口的DMA控制器是在Altera PHY IP和Synopsys Core IP的基础上实现的,利用Synopsys VIP验证环境进行了功能仿真验证

2018-01-11 10:57:04 11281

11281

在图1所示架构中,每次DMA传输都要发起1次读与1次写操作。若在DMA传输期间有需要紧急处理的异常响应,AHB总线此时又被DMA控制器占用,则处理器只能等DMA控制器释放AHB总线后才能占用AHB总线进行操作,影响处理器效率与系统对异步事件的响应速度。

2018-08-24 15:34:53 1563

1563

一个DMA控制器,实际上是采用DMA方式的外围设备与系统总线之间的接口电路,这个接口电路是在中断接口的基础上再加DMA机构组成。习惯上将DMA方式的接口电路称为DMA控制器。

2019-04-01 16:08:06 10025

10025 DMA(Direct Memory Access)控制器是一种在系统内部转移数据的独特外设,可以将其视为一种能够通过一组专用总线将内部和外部存储器与每个具有DMA能力的外设连接起来的控制器。它之所以属于外设,是因为它是在处理器的编程控制下来 执行传输的。

2019-11-15 10:25:56 12384

12384 在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过AXI

2020-09-24 09:50:30 4289

4289

XDMA是Xilinx封装好的PCIE DMA传输IP,可以很方便的把PCIE总线上的数据传输事务映射到AXI总线上面,实现上位机直接对AXI总线进行读写而对PCIE本身TLP的组包和解包无感。

2020-12-28 10:17:23 2692

2692 不同类型的DMA GPIO PL general purpose AXI GP AXI utlilizing PS DMAC High performance w/DMA ACP w/DMA 几种

2020-10-09 18:05:57 6390

6390

基于AXI的DMA对内部寄存器的读写有着相同的方式。在普通传输模式下,DMA内部的寄存器都是由处理器通过AXI-Lite总线进行读写的;但基于AXI总线的三种DMA,都增加了S/G传输模式,它卸载

2020-10-10 10:23:37 6203

6203

ZYNQ中DMA与AXI4总线 为什么在ZYNQ中DMA和AXI联系这么密切?通过上面的介绍我们知道ZYNQ中基本是以AXI总线完成相关功能的: 图4‑34连接 PS 和 PL 的 AXI 互联

2020-11-02 11:27:51 3880

3880

在 AMBA 系列之 AXI 总线协议初探 中,了解到 AXI 总线交互分为 Master / Slave 两端,而且标准的 AXI 总线支持不同的位宽,既然是总线,那么必须要支持总线互联,多 Master,多 Slave的场景

2022-02-08 11:44:02 12802

12802 在介绍AXI之前,先简单说一下总线、接口以及协议的含义。总线、接口和协议,这三个词常常被联系在一起,但是我们心里要明白他们的区别。

2021-02-04 06:00:15 10

10 本系列我想深入探寻 AXI4 总线。不过事情总是这样,不能我说想深入就深入。当前我对 AXI总线的理解尚谈不上深入。但我希望通过一系列文章,让读者能和我一起深入探寻 AXI4。

2021-03-17 21:40:29 25

25 AXI是个什么东西呢,它其实不属于Zynq,不属于Xilinx,而是属于ARM。它是ARM最新的总线接口,以前叫做AMBA,从3.0以后就称为AXI了。

2021-04-09 17:10:10 4970

4970

本系列我想深入探寻 AXI4 总线。不过事情总是这样,不能我说想深入就深入。当前我对 AXI总线的理解尚谈不上深入。但我希望通过一系列文...

2022-02-07 11:36:33 4

4 本文以浮点数Floating-point IP核将定点数转换为浮点数为例,详细讲解AXI DMA IP核的使用方法。

2022-02-16 16:21:37 7545

7545

AXI (高性能扩展总线接口,Advanced eXtensible Interface)是ARM AMBA 单片机总线系列中的一个协议,是计划用于高性能、高主频的系统设计的。AXI协议是被优化

2022-10-10 09:22:22 8632

8632 AN3109_用STM32F10x微控制器的DMA和DMA超时仿真通信外设FIFO

2022-11-21 08:11:29 0

0 AN4104_STM32F0xx的DMA控制器的使用

2022-11-21 08:11:37 2

2 在zynq开发过程中,AXI总线经常遇到,每次看到AXI总线相关的信号时都一头雾水,仔细研究一下,将信号分分类,发现其实也不难。

2023-05-25 11:22:54 570

570

从 FPGA 应用角度看看 AMBA 总线中的 AXI4 总线。

2023-06-21 15:21:44 1729

1729

电子发烧友网站提供《STM32F0xx的DMA控制器的使用.pdf》资料免费下载

2023-09-21 14:49:49 0

0 LogiCORE™IPAXI IIC总线接口连接到AMBA®AXI规范,提供低速、两线串行总线接口,可连接大量流行的设备。

2023-09-28 15:56:16 4484

4484 LogiCORE IP AXI 通用异步接收发送器 (UART) 16550 连接到高级微控制器总线架构 (AMBA) AXI,为异步串行数据传输提供控制器接口。该软 IP 核旨在通过 AXI4-Lite 接口进行连接。

2023-10-16 11:02:01 1762

1762

由由数据线、地址线、控制线等构成。 接口是一种连接标准,又常常被称之为物理接口。 协议是传输数据的规则。 1.简介 AXI4总线协议是 ARM 公司 提出的AMBA( Ad vanced Microcontroller Bus Archi te cture)3.0协议中最重要的部分,是一种面向高性能、高带

2023-12-16 15:55:01 248

248 Transaction Layer的所有功能特性,不仅内置DMA控制器,而且具备AXI4用户接口,提供一个高性能,易于使用,可定制化的PCIe-AXI互连解决方案,同时适用于ASIC和FPGA。

2024-02-21 15:15:03 144

144

Transaction layer的所有功能特性,不仅内置DMA控制器,而且具备AXI4用户接口,提供一个高性能,易于使用,可定制化的PCIe-AXI互连解决方案,同时适用于ASIC和FPGA。

2024-02-22 09:15:46 0

0 或Scather Gather DMA,提供FIFO/AXI4-Stream用户接口。

基于PCI Express Integrated Block,Multi-Channel PCIe RDMA

2024-02-22 11:11:55 156

156

电子发烧友App

电子发烧友App

评论