中断处理程序的执行可以被具有更高优先级的异常抢占。可以执行多少个具有更高优先级的异常中断?产生了两个中断。这个数字是无限的吗?

2022-12-09 08:01:35

关系吗? 中断和 EVAL_6EDL7141_TRAP_1SH之间是否存在优先级关系?

如果是, EVAL_6EDL7141_TRAP_1SH 处理程序是否可以被另一个优先级更高的 EVAL_6EDL7141_TRAP_1SH 或中断中断

2024-01-18 08:48:42

如何从异常中断返回?异常中断处理程序结构什么样?何为异常中断向量表?哪一种异常中断优先级最高?

2021-12-14 07:40:24

处理器模式和内部多线程和外部多处理器的处理器结构。在嵌入式系统中具有重要意义的异常中断技术在S3C4510B系统中也体现了ARM体系独有的一些的特点。本文根据S3C4510B系统的特点,分析了该系统中

2020-03-31 07:59:41

,SWI异常中断处理函数分为两级,第一级的SWI处理函数用于从SWI指令中提取24位的立即数即中断号,通第一级函数通过汇编语言、内嵌汇编来完成。第二级SWI异常中断处理程序实现各个SWI的具体功能,第二级

2017-01-10 15:09:37

IRQ中断,当进入FIQ模式时,禁止IRQ中断。(3).将寄存器lr_mode设置成返回地址。(4).将程序计数器(PC)值,设置成该异常中断的中断向量地址,从而跳转到相应的异常中断处理程序处执行。上述

2020-08-28 08:09:17

(这时处理器决定的,无法更改!)即 A+8 返回后,应执行被中断而没有执行的指令(上面的 A+4),所以返回时,pc = lr-4 3,指令预取中止异常中断处理的返回:指令地址APC-8执行本指令时发生

2016-03-31 16:09:03

后,应执行被中断而没有执行的指令(上面的 A+4),所以返回时,pc = lr-4 3,指令预取中止异常中断处理的返回:指令地址APC-8执行本指令时发生中断,A+4PC-4处理器将 A+4(PC-4

2017-05-05 14:47:47

的,无法更改!)即 A+8 返回后,应执行被中断而没有执行的指令(上面的 A+4),所以返回时,pc = lr-4 3,指令预取中止异常中断处理的返回:指令地址APC-8执行本指令时发生中断

2016-07-22 11:32:45

E8018A/19A Hitachi SH7708,7709分析探头,B3759A仿真解决方案接口软件

2019-03-14 19:49:31

`请问PCB过孔阻焊的处理方式有哪些?`

2019-12-31 15:28:04

如果我注册一个外部中断,但是其中断服务函数需要处理1s,但是在这1s内又出现了多次外部触发,那么rtthread的默认处理方式是什么样的啊?1.中断嵌套,停止当前的中断服务函数,进入新触发后的中断

2022-03-21 15:56:02

目录1、系统异常中断2、外部中断(全部)3、优先级5、如何开关中断示例6、抢断优先级、响应优先级说明7、定时器说明7.1基本定时器7.2高级/通用定时器7.3定时器拓展补充-主要特性F429 在内

2021-08-18 06:32:24

BOSStartHang ,//根据提示,应当永远不会到这步的。其实很简单,因为STM32本身的异常中断PendSV_Handler替代了UCOS的异常中断OSPe

2021-08-23 08:19:41

(这时处理器决定的,无法更改!)即 A+8 返回后,应执行被中断而没有执行的指令(上面的 A+4),所以返回时,pc = lr-4 3,指令预取中止异常中断处理的返回:指令地址APC-8执行本指令时发生

2016-07-25 11:19:25

后,应执行被中断而没有执行的指令(上面的 A+4),所以返回时,pc = lr-4 3,指令预取中止异常中断处理的返回:指令地址APC-8执行本指令时发生中断,A+4PC-4处理器将 A+4(PC-4

2016-09-23 14:35:11

如何对串口DMA进行初始化呢?串口IDLE中断的处理方式是什么?

2021-12-08 07:28:12

返回后,应执行被中断而没有执行的指令(上面的 A+4),所以返回时,pc = lr-4 3,指令预取中止异常中断处理的返回:指令地址APC-8执行本指令时发生中断,A+4PC-4处理器将 A+4

2014-04-02 15:16:51

中断而没有执行的指令(上面的 A+4),所以返回时,pc = lr-4 3,指令预取中止异常中断处理的返回:指令地址A PC-8执行本指令时发生中断,A+4PC-4处理器将 A+4(PC-4)保存

2016-07-04 16:20:49

在使用RTT开发过程中我们有发现TCP网络在外置百兆PHY进行传输时,会出现持续进入DMA RBUS异常中断的情况,与之共同出现的还有TCP调用write失败,其他网络功能失效,验证发现设备未死机

2022-10-12 06:18:18

`此项目实现的是双机在2.4GHz频段上的单向数字通信。采用实验室现有的SH3开发板,所作的主要工作是了解7709s单片机的编程方法,CRM2401HNC的操作方法和无线通讯程序的编写。`

2011-03-04 13:52:50

按键消抖都有哪些处理方式除了硬件消抖电路用软件怎么实现

2023-11-01 07:06:20

的值已经更新,它指向当前指令后面第3条指令(对于ARM指令,它指向当前指令地址加12字节的位置;对于Thumb指令,它指向当前指令地址加6字节的位置),当FIQ/IRQ异常中断产生时,处理器将值

2022-08-18 15:26:04

日立SH7709A/29微处理器

2019-03-22 09:23:20

日立SH7709A/29微处理器

2019-03-27 15:55:40

日立SH7709A/29微处理器的仿真和分析解决方案

2019-04-01 17:14:37

时,pc = lr 即可。2.IRQ 和 FIQ 异常中断处理的返回:指令地址对应于 PCAPC-8执行此指令完成后(!)查询 IRQ 及 FIQ,如果有中断请求则产生中断. A+4 PC-4A+8 PC

2018-06-26 08:42:18

请问一下STM32F429系统异常中断有哪些呢?

2021-11-23 06:57:11

部件号 LSM6DS3 的标记“SH”和“S2”有什么区别?请告知正确的顶部标记 SH" 和 "S2" 是否均有效。谢谢

2023-01-06 06:56:07

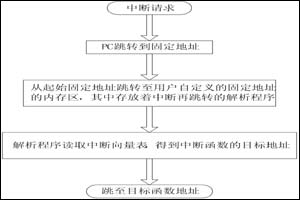

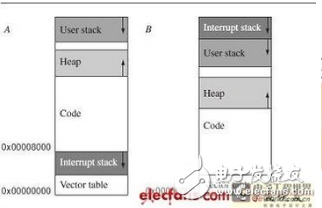

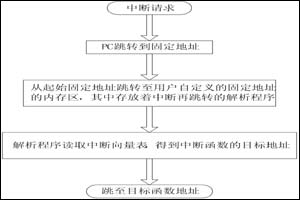

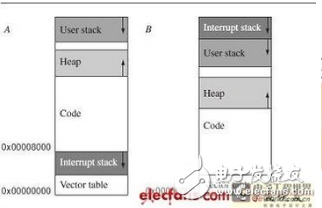

摘要:本文首先简要概述了ARM处理器的异常中断种类、响应和返回过程;然后重点讨论了中断解析程序的原理和实现,并分别给出了普通中断和向量中断的处理示例流程图和详细

2006-03-11 12:18:54 760

760

ARM体系中的异常中断及其应用

2017-09-22 16:51:52 4

4 PLC作为一种采用微处理器技术的工业控制装置,其基本系统包括CPU,输入/输出接口,系统程序和用户程序存储单元等部分,SH/SH1/SH2系列PLC作为一个整体式固定I/O的PLC,其内部也包含了这些功能部分。

2017-09-24 10:06:51 0

0 SH2是光洋公司在SH1的基础上,新开发的一个PLC系列产品。与SH1相比较,SH2主要增加了一个RS485(三线式)通讯口。

2017-09-24 10:09:08 1

1 3.4 异常中断处理 异常或中断是用户程序中最基本的一种执行流程和形态。这部分主要对ARM架构下的异常中断做详细说明。 ARM有7种类型的异常,按优先级从高到低的排列如下:复位异常(Reset

2017-10-18 13:29:56 1

1 11.7 异常中断产生指令(断点指令) Thumb异常中断产生指令与ARM指令集下的异常中断指令十分相似。同ARM指令集相同,Thumb指令集中同样包含两条异常中断产生指令:软件中断指令SWI用于

2017-10-19 09:32:58 0

0 当异常中断发生时,系统执行完当前指令后,将跳转到相应的异常中断处理处执行。当异常中断处理程序执行完成后,程序返回到发生中断指令的下一条指令处继续执行。在进入异常中断处理程序时,要保存被中断程序的执行线程。从中断处理程序退出时要恢复被中断程序的执行现场。

2017-12-16 08:57:03 4440

4440 本文介绍A了RM S3C4510B系统 的 异常中断 机制,包括异常中断的分类,响应与返回;中断处理程序的安装与调用;SWI,IRQ中断的实例与关键代码。随着人们对于电子产品的要求越来越高

2018-02-03 05:32:01 1561

1561

ARM单片机是大多数新手选择的入门切入点,但由于知识的不足,在设计过程中新手们经常会遇到这样或那样的问题,ARM异常中断返回就是这样一种令人头疼的问题。在ARM的使用问题中异常中断返回是新手们较为苦恼的问题,本文就将对ARM异常中断的集中情况进行总结,并给出了一些解决方法。

2018-02-08 09:29:45 6187

6187

ARM中异常中断的类型问题分析总结 一、ARM中异常中断的类型: 异常中断名称 含义 复位(Reset) 当处理器复位引脚有效时,系统产生复位异常中断,程序跳转到复位异常中断处理程序处执行。复位

2018-04-05 10:51:00 1148

1148 当ARM异常中断发生时,系统执行完当前指令后,将跳转到相应的异常中断处理程序处执行。当异常中断处理程序执行完成后,程序返回到发生中断指令的下条指令处执 行。在进入异常中断处理程序时,要保存被中断程序的执行现场,从异常中断处理程序退出时,要恢复被中断程序的执行现场。

2020-06-17 10:05:12 7044

7044 外部中断请求(IRQ) 当处理器的外部中断请求引脚有效,而且CPSR的寄存器的I控制位被清除时,处理器产生外部中断请求异常中断。系统中个外设通过该异常中断请求处理服务。

2020-08-27 14:21:29 2354

2354 异常是能够引起程序流偏离正常流程的事件,当异常发生时,正在执行的程序就会被挂起,处理器转而执行一块与该事件相关的代码(异常处理)。事件可以是外部输入,也可以是内部产生的,外部产生的事件通常被称作中断

2021-10-12 17:14:18 4165

4165 在Cortex‐M0内核上搭载了一个异常响应系统,支持众多的系统异常和外部中断。其中,编号为1-15的对应系统异常,大于等于16的则全是外部中断,优先级的数值越小,则优先级越高。除了个别异常的优先级被定死外,其它异常的优先级都是可编程的。

2022-06-01 14:41:41 3613

3613 个人收集的一些异常处理方式

2022-08-11 15:01:08 0

0 电子发烧友网站提供《SH6612,SH6612A,SH66P12差异表.pdf》资料免费下载

2022-10-12 15:22:07 0

0 电子发烧友网站提供《SH67P33和SH67P33A/SH66K33A与SH67P33C之间的差异表.pdf》资料免费下载

2022-10-12 15:31:32 0

0 电子发烧友网站提供《SH69K20A与SH69P20,SH66P20A,SH6620A差异对照表.pdf》资料免费下载

2022-10-12 15:17:52 0

0 电子发烧友网站提供《SH67P33和SH67P33A/SH66K33A与SH67P33C差异对照表.pdf》资料免费下载

2022-10-12 15:05:54 0

0 SH7266 组, SH7267 组 用户手册: 硬件

2023-03-23 19:26:21 6

6 SH7268 组, SH7269 组 用户手册: 硬件

2023-03-23 19:26:50 0

0 SH726A 组, SH726B 组 用户手册: 硬件

2023-03-29 19:07:41 0

0 SH7457 组, SH7459 组 用户手册: 硬件

2023-03-31 18:35:37 0

0 SH7750, SH7750S, SH7750R 组 用户手册: 硬件

2023-03-31 18:42:23 0

0 SH7214 组, SH7216 组 用户手册: 硬件

2023-03-31 19:13:55 0

0 the SH7264, SH7262, SH7266, SH7267, SH7268, SH7269, SH726A, and SH726B

2023-04-03 18:51:46 0

0 SH72A2 组, SH72A0 组 用户手册: 硬件

2023-04-11 19:16:03 0

0 SH7710, SH7712, SH7713 组 用户手册: 硬件

2023-04-12 18:36:39 0

0 SH7280 组, SH7243 组 用户手册: 硬件

2023-04-17 19:29:25 0

0 SH74504 SH74513 SH74552 SH74562 SH74504_Debug_MCU_BOARD and SH74552_Debug_MCU_BOARD)

2023-04-17 20:12:57 0

0 SH7720 组, SH7721 组 用户手册: 硬件

2023-04-18 18:58:08 0

0 the SH72546RFCC SH72546R SH72544R SH72543R SH72531RFCC SH72531FCC and SH72531)

2023-04-18 19:20:07 0

0 SH-2E SH7059 F-ZTATTM SH7058S F-ZTATTM 硬件手册

2023-04-19 19:46:05 0

0 SH7709A 硬件手册

2023-04-20 18:47:30 0

0 SH-2A SH-2 E200F 仿真器用户手册附加文档(关于使用 SH7083 SH7084 SH7085 SH7086 SH7146 SH7149 SH7124 和 SH7125 的补充信息)

2023-04-20 19:38:42 0

0 SH7125群 SH7124群 硬件手册

2023-04-21 19:37:24 1

1 SH-2A SH-2 E200F Emulator Additional Document for 用户手册 (Supplementary Information on Using SH72546RFCC SH72544R SH72543R SH72531 and SH72531FCC)

2023-04-21 19:46:55 0

0 SH-2A SH-2 E200F 仿真器用户手册附加文档(使用 SH7286 SH7285 和 SH7243 的补充信息)

2023-04-21 19:47:12 0

0 SH-1/SH-2/SH-DSP 软件手册

2023-04-21 19:58:03 0

0 SH-2A、SH2A-FPU 软件手册

2023-04-26 19:22:48 1

1 SH-2A SH-2 E200F 仿真器用户手册附加文档(关于使用 SH7136 SH7137 SH7142 和 SH7147 的补充信息)

2023-04-27 19:57:13 0

0 SH-2A SH-2 E200F 仿真器用户手册附加文档(关于使用 SH7203 和 SH7263 的补充信息)

2023-04-28 18:57:09 0

0 SH7014 SH7016 SH7017F-ZTATTM 硬件手册

2023-04-28 19:20:32 0

0 SuperH 系列 E10A-USB 仿真器用户手册附加文档(关于使用 SH7670 SH7671 SH7672 和 SH7673 的补充信息)

2023-04-28 19:40:53 1

1 SH7125群、SH7124群 硬件手册

2023-05-04 19:27:13 0

0 SH-3/SH-3E/SH3-DSP 软件手册

2023-05-08 18:45:15 0

0 SH-4A SH4AL-DSP E200F Emulator Additional Document for 用户手册 (Supplementary Information on Using SH7785)

2023-05-08 19:49:46 0

0 SH7032 SH7034 硬件手册

2023-05-09 19:02:12 0

0 SH7050群 SH7050F-ZTAT SH7051F-ZTAT 硬件手册

2023-05-09 19:24:33 1

1 SH7262 组, SH7264 组 用户手册: 硬件

2023-05-15 20:28:55 0

0 SH-3/SH-3E/SH3-DSP 软件手册

2023-06-26 21:05:55 1

1 SH7032 SH7034 硬件手册

2023-06-27 20:23:12 1

1 SH7050群 SH7050F-ZTAT SH7051F-ZTAT 硬件手册

2023-06-27 20:46:34 0

0 SH7268 组, SH7269 组 用户手册: 硬件

2023-07-10 19:17:54 0

0 SH726A 组, SH726B 组 用户手册: 硬件

2023-07-11 19:32:06 0

0 SH7262 组, SH7264 组 用户手册: 硬件

2023-07-12 19:21:26 0

0 SH7457 组, SH7459 组 用户手册: 硬件

2023-07-13 19:40:33 0

0 SH7750, SH7750S, SH7750R 组 用户手册: 硬件

2023-07-13 19:47:41 0

0 SH7751 组, SH7751R 组 用户手册: 硬件

2023-07-13 19:48:02 0

0 SH7239 组, SH7237 组 用户手册: 硬件

2023-07-14 09:25:04 0

0 the SH7264, SH7262, SH7266, SH7267, SH7268, SH7269, SH726A, and SH726B

2023-07-14 09:52:05 0

0 SH7710, SH7712, SH7713 组 用户手册: 硬件

2023-07-21 11:16:13 0

0 SH7455 组, SH7456 组 用户手册: 硬件

2023-09-05 18:30:51 0

0 当异常中断发生时,程序将当前执行指令的下一条指令的地址存入新的异常模式的链接寄存器LR中(R14_<mode>),以便程序在异常处理完后,能正确返回原程序。

2023-10-18 17:25:43 302

302 arm处理器有哪些中断源?arm处理器对异常中断的响应过程 ARM处理器是一种广泛使用的嵌入式处理器,运行着各种不同类型的应用程序。为了保证应用程序的稳定性和正确性,ARM处理器需要在遇到异常

2023-10-19 16:35:59 675

675 ARM中的异常中断是如何实现进入中断程序的?如何进入呢? 在计算机系统中,异常和中断是两个常见的概念。 在ARM中,异常和中断的主要目的是帮助处理器响应与系统操作相关的事件。 由于处理器必须同时执行

2023-10-19 16:36:11 481

481

正在加载...

电子发烧友App

电子发烧友App

评论