设计基于DS12C887高精度时钟的意义

DS12C887时钟芯片能够自动显示年、月、日、时、分、秒等时间信息,同时还具有校时,报时,闹钟等功能。DS12C887也可以很方便的由软件编程进行功能的调整或增加。所以设计基于DS12C877时钟芯片的高精度时钟的设计具有十分重要的现实意义和实用价值。

设计方案

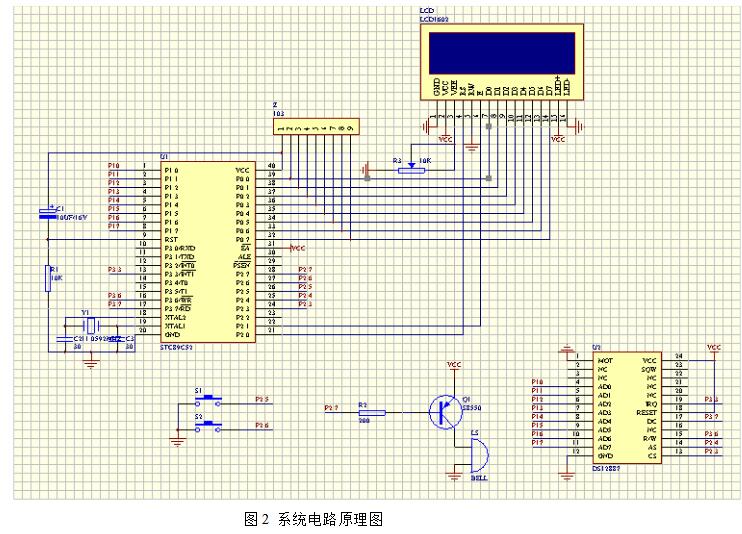

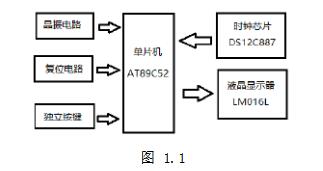

在传统的基于单片机的数字时钟设计的基础上经过一些改进,引入DS12C887时间芯片,本次设计可分为两部分:硬件部分包括:体积小功能丰富的STC89C52单片机、具有掉电保护的DS12C887时钟芯片电路简单易于实现的1602LCD液晶显示器,键盘输入电路等。具体说来,系统智能控制部分由单片机及其相关的外围电路组成,外围电路包括解决死机等问题的复位电路、波形稳定的晶振电路、键盘设计、闹铃电路以及合适的直流电源电路。

利用单片机将复位电路、能够降低功耗和减少显示器外部引线的显示电路、电源电路等正确的连接在一起,并通过单片机的编程来实现本次设计任务中的要求。软件部分主要包括了主程序模块,DS12C887模块,LCD1602模块,键盘控制模块。DS12C887芯片具有掉电保护功能,内部自带锂电池,能够在断电的情况下保持时间信息,等到外部电路恢复供电之后能够不必调整时间,为时钟的校时操作节省了很多时间,而且这种设计更节能,在需要观察时间的时候比如白天就可以给主电路通电。而在夜晚不需要观察时钟的时候就可以给主电路断电,这样可以节约大量电能。

时间芯片DS12C887采用了内部集成晶振的电路,并且具有内部温漂补偿电路设计。能够准确计时,提供精确的时间,这样就简化了电路的器件选择,另外也使程序的设计更加简洁。在硬件设计方面,由于只增加了一个DS12C887时间芯片,因此并不是特别复杂,而且这种独立计时的设计使得产品排故更加方便。

设计过程详解

一、系统组成

1、系统原理与硬件设计

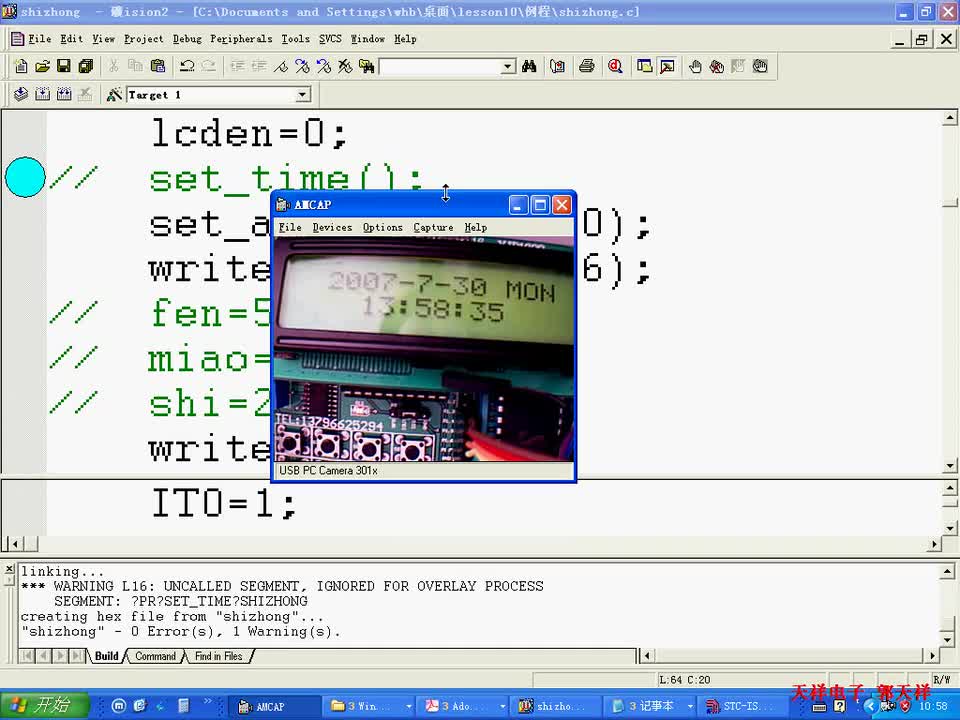

本次的设计题目是电子万年历设计,要求实现年、月、日、时、分、秒的正常显示,需要硬件和软件的结合来实现。本次设计利用时钟日历芯片DS12C887的特性和STC89C52单片机的功能利用实现的。根据设计的要求万年历要显示年、月、日、时、分、秒的显示同LCD1602。

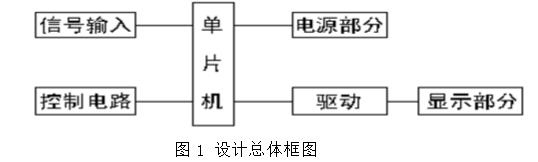

在明确本次设计思路之后,画出设计框图,总体框图如图2.1所示。

2、硬件选择

(1)时钟芯片选择 选用DS12C887时钟芯片。

(2)单片机的选择 选用STC89C52单片机,并配备11.0592MHz晶振,复位电路采用上电复位。

(3)显示电路选择 采用LCD1602液晶显示。

(4)电源选择 采用直流5V电源供电。

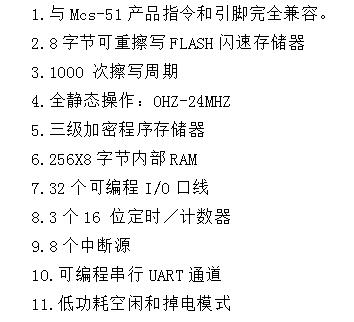

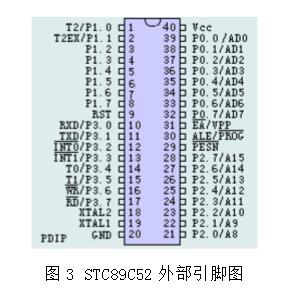

3、单片机STC89C52中文资料

STC89C52 是STC公司生产的低电压,高性能CMOS 8位单片机.片内含8K byTES的可反复擦写的只读程序存储器(PEROM)和256 bytes的随机存取数据存储器(RAM),器件采用STC公司的高密度、非易失性存储技术生产,与标准MCS-51指令系统及8052 产品引脚兼容,片内置通用8位中央处理器(CPU )和FLASH由存储单元, STC89C52单片功能强大,适用于许多电子产品。

主要性能参数:

Vcc:电源电压 GND:地线

P0:P0口是一组8位漏极开路型双向1/O 口,也即地址/数据总线复用口。作为输出口用时.每位能吸收电流的方式驱动8个TTL 逻辑门电路,对端口P0 写“1”时,可作为高阻抗输入端用。

当访问外部数据存储器或程序存储器时,这组口线分时转换地址(低8位)和数据总线复用,在访问期间激活内部 上拉电阻。

在FLASH由编程时,P0口接收指令字节,而在程序校验时,输出指令字 节,校验时,要求外接上拉电阻。

P1口:PI 是一个带内部上拉电阻的8位双向I/O口,Pl的输出缓冲级可驱动(吸收或输出电流)4个TTL逻辑门电路。对端口写“1”,通过内部的上拉电阻把端口拉到高电平,此时可作输入口。作输入口使用时,因为内部存在上拉电阻某个引脚被外部信号拉低时会输出一个电流IIL

与AT89C51不同之处是,Pl.0 和P1.1还可分别作为定时/计数器2 的外部计数输入(Pl.0/T2 )和输入(P1.1/T2EX) ,参见图3

FLASH编程和程序校验期间,Pl接收低8位地址。

图3 PI.O 和PI.l 的第二功能

口:P2 是一个带有内部上拉电阻的8位双向I/O口,P2的输出缓冲级可驱动(吸收或输出电流)4个TTL逻辑电路。对端口P2写“l“,通过内部的上拉电阻把端口拉到高电平,此时可作输入口,作输入口使用时,因为内部存在上拉电阻,某个引脚被外部信号拉低时会输出一个电流(llt )。

在访问外部程序存储器或16位地址的外部数据存储器(例如执行MOvx@DPTR 指令)时,P2送出高8 位地址数据。在访问8位地址的外部数据存储器、如执行MOVX@RI指令)时,P2口输出P2锁存器的内容。

FLASH编程或校验时,P2亦接收高位地址和一些控制信号。

·P3口:P3口是一组带有内部上拉电阻的8位双向I/O口。P3口输出缓冲级可驱动(吸收或输出电流)4个TTL逻辑门电路。对P3口写入“1”时,内部上拉电阻把它们被拉高,并作为输入的端口。这个时候,被外部拉低的P3口将用上拉电阻输出电流(IIL) 。

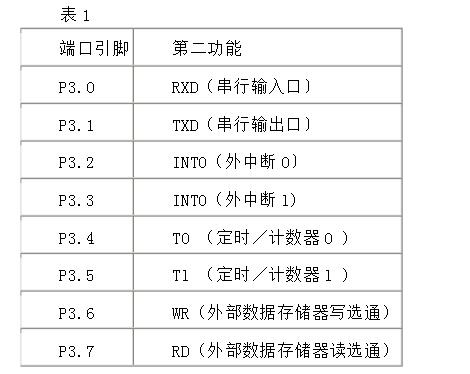

P3口除了作为一般的I/0口线外,更重要的用途是它的第二功能,如图表1:

此外,P3口还接收一些用于FLASH闪速存储器编程和程序校验的控制信号。 RST:复位输入。当振荡器工作时,RST引脚出现两个机器周期以上的高电平时单片机复位。

·ALE/PROG:当访问外部程序存储器或数据存储器的时候,ALE(地址锁存允许)输出脉冲用来锁存低8位字节的地址.通常,ALE依然以时钟振荡频率的1/6输出固定的脉冲信号,所以可以用来实现对外输出时钟或用于定时目的。每次访问外部数据存储器时将跳过一个ALE脉冲。

对Flash存储器编程的时候,这个引脚还用于输入编程脉冲(PROG)。可以通过对特殊功能寄存器(SFR)区中的8EH单元的D0位置位.可禁止ALE操作。该位置位后,只有一条MOVX和MOVC指令才能将ALE激活,另外,此引脚会被拉高一点点,当单片机执行外部程序得时候,应该把ALE设置为禁止。

·PSEN:程序储存允许PSEN输出是外部程序存储器的读选通信号,当AT89C52由外部程序存储器取指令时,每个机器周期两次PSEN有效,就是输出两个脉冲。这个时候,当访问外部数据存储器时,就会跳过两次PSEN信号。

·EA/VPP:外部访问允许。欲使CPU 仅访问外部程序存储器(地址为0000H-FFFFH ) , EA端必须保持低电平(接地).

如EA端接在高电平上, CPU就执行内部程序存储器中的指令。

flash存储器编程时,该引脚加上+12V的编程允许电源VPP ,该器件必须使用12V编程电压VPP 。

·XTAL1:振荡器的反相放大器的及内部时钟发生器的输入端. ·XTAL2:振荡器的反相放大器的输出端。

AT89C52的特殊功能是,在AT89C52 片内存储器中,80H-FFH 共128 个单元为特殊功能寄存器(SFR),SFR 的地址空间映象如表2 所示。

并非所有的地址都被定义,从80H—FFH 共128 个字节只有一部分被定义,还有相当一部分没有定义。对没有定义的单元读写将是无效的,读出的数值将不确定,而写入的数据也将丢失。

不应将数据写入未定义的单元,由于这些单元在将来的产品中可能赋予新的功能,在这种情况下,复位后这些单元数值总是“0”。

AT89C52除了有AT89C51所有的定时/计数器0 和定时/计数器1 外,还增加了一个定时/计数器2。定时/计数器2 的控制和状态位位于T2CON,T2MOD,寄存器对(RCAO2H、RCAP2L)是定时器2 在16 位捕获方式或16 位自动重装载方式下的捕获/自动重装载寄存器。

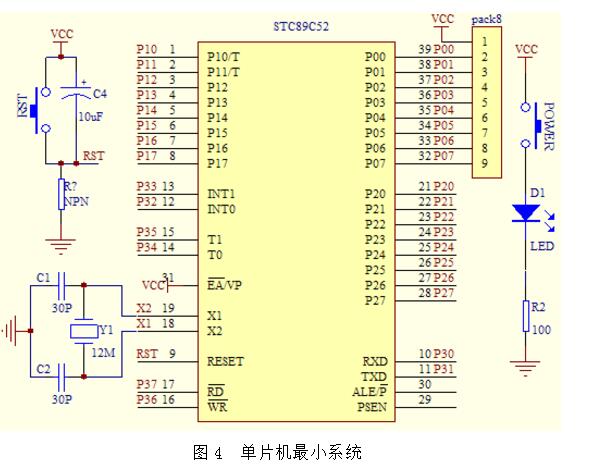

4、STC单片机最小系统

STC单片机是一种高性能、低功耗的8位CMOS微处理芯片, STC单片机虽然功能强大,但要想完成其强大的功能,单靠它也是不的行的,因此要让它运行起来,就要创设其工作的环境,即最小系统,STC单片机最小系统如图1所示,它包括由一个晶振,两个电容组成的振荡电路,一个复位按钮一个10UF电容和一个10K电阻组成的复位电路,电源电路三个电路组成。本系统以STC89S52单片机为核心,使用11.0592MHZ的晶振,复位电路为按键高电平复位。

二、系统硬件电路设计

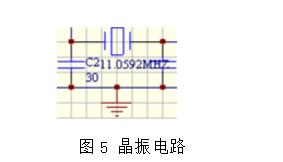

1、晶振电路

在晶振电路中,C1、C2为晶振的负载电容,分别接在晶振的两个脚上和对地的电容,电路中取了30PF。因为晶振与单片机的振荡电路中脚XTAL0和脚XTAL1会产生偕波,虽然谐波对电路的影响不大,但是会影响电路中时钟振荡器的稳定性。 在晶振的脚XTAL0和脚XTAL1之间接分别接入两个5pf-30pf的瓷片电容接可以增加电路的稳定性。

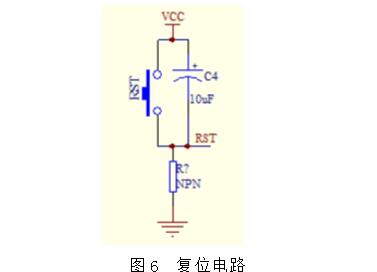

2、复位电路

单片机复位电路有上电自动复位和手动复位两种方式。上电复位要求接通电源后,自动进行复位操作。手动复位要求接通电源的前提下,在单片机运行的条件下,在单片机运行期间,用按钮开关操作使单片机进行复位的操作。这里采用的是手动复位。

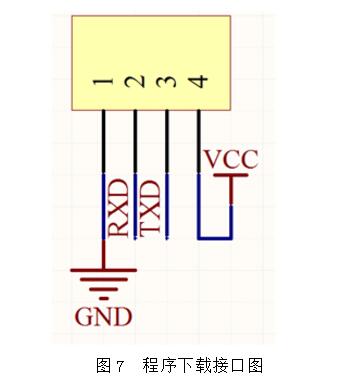

3、程序下载接口

1)1602液晶概述

1602LCD是指显示的字符和数字为16X2,即可以显示两行,每行16个字符液晶模块共32个字符和数字。

1602LCD主要技术参数:

1.显示大小:16×2个字符

2.芯片额定电压:4.5—5.5V

3.额定电流:2.0mA(5.0V)

4.工作时的电压:5.0V

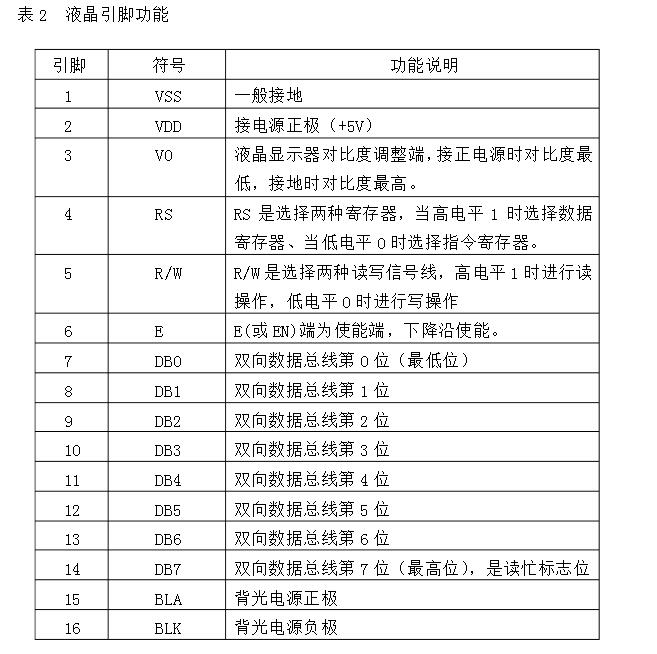

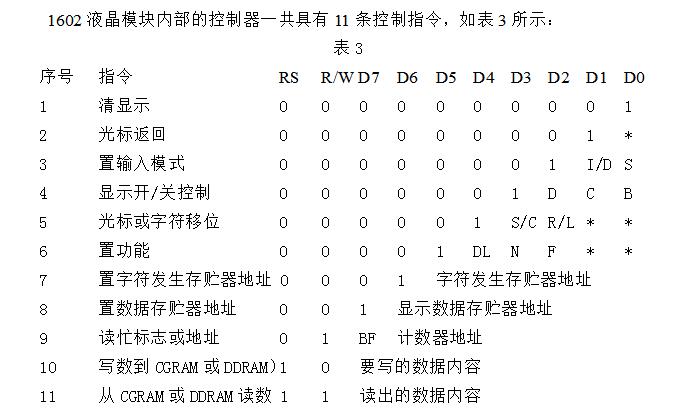

2)1602液晶引脚功能

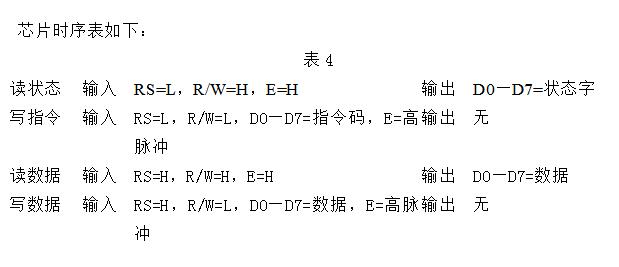

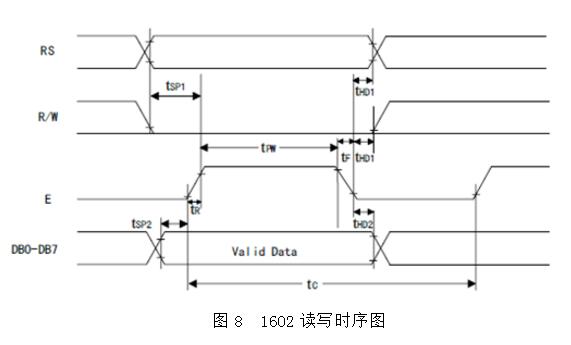

3)1602读写时序图

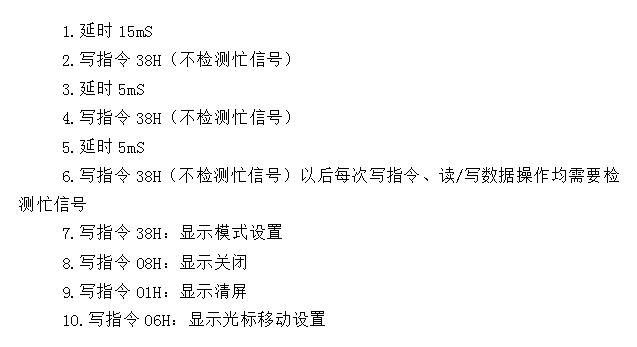

4、1602LCD的一般初始化(复位)过程

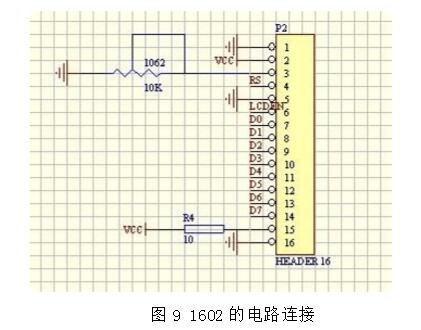

5、1602LCD的电路连接

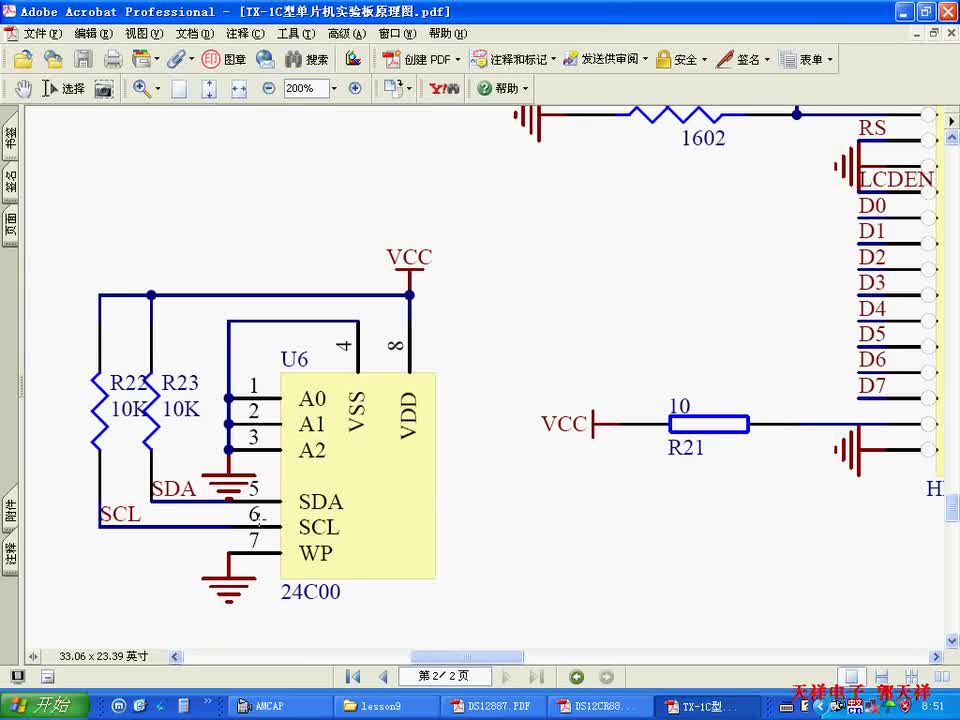

液晶5端为读/写选择端,因为我们不从液晶中读取数据,只向其写入命令和显示数据,因此此端始终选择为写状态,即低电平接地。液晶6端为使能信号,是操作时必须的信号。其电路如图2-11所示:

1)DS12C887概述

DS12C887具有DS12R885裸片,32.768HZ石英晶体和一个可充电电池三个部分, DS12C887与计算机常用的时钟芯片MC146818B和DS12887管脚兼容,同时可直接替换可以用来直接代替IBM PC上的时钟日历芯片DS12887。采用DS12C887芯片设计的时钟电路有良好的微机接口,并且不需要任何外围电路和器件。时钟芯片DS12C887具有如下的特征:

(1)DS12C887里面自带一个锂电池,外部掉电时,内部信息还能保持10年的时间,保证不丢失数据。

(2)能够自动产生秒、分、时、天、星期、日、月、年、世纪等时间信息, 并 有闰年补偿功能。其内部还增加了世纪寄存器,利用硬件电路解决了“千年”问题。

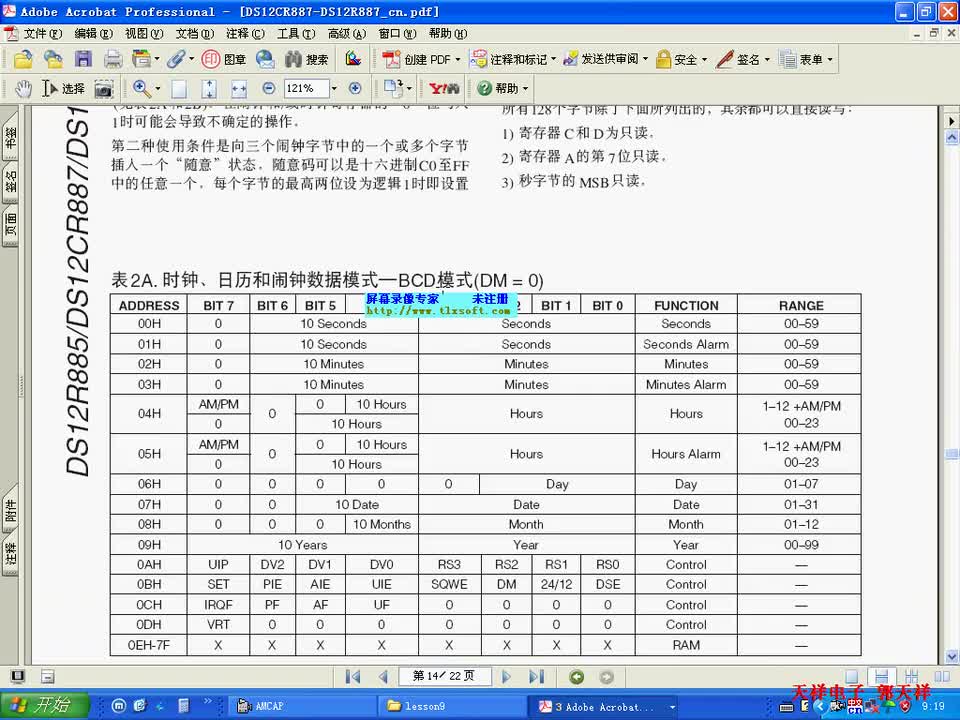

(3)具有二进制数码和BCD码两种表示时间的方法、具有日 历和定时闹钟功能。

(4)一天内的时间记录具有12小时制和24小时制两种,12小时时钟模 式中,具有PM和AM用来区分上午和下午。同时可选用夏令时模式;

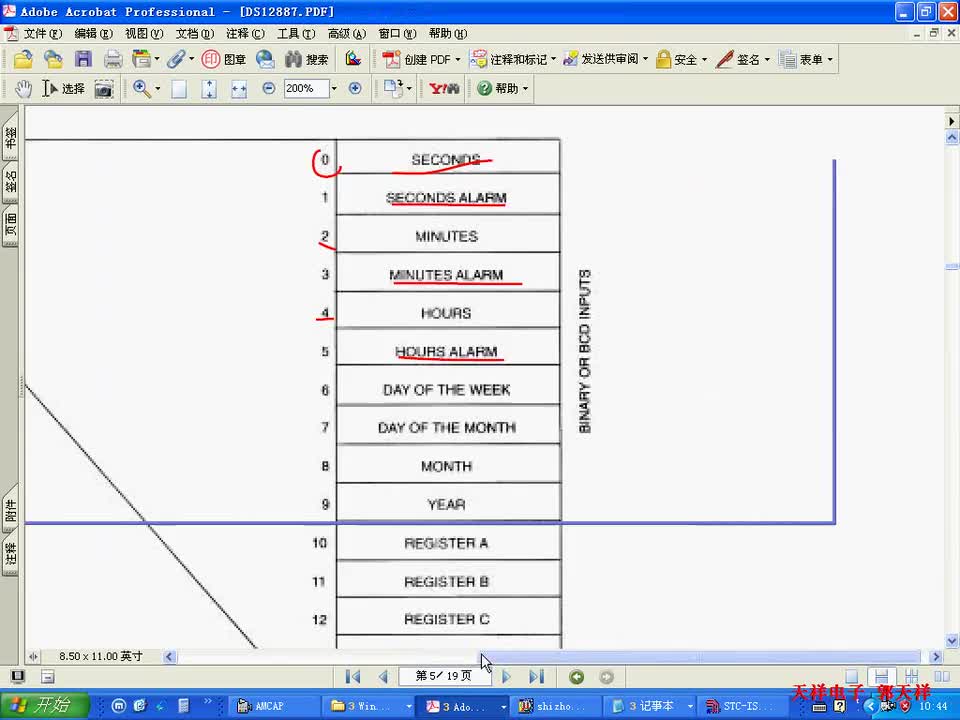

(5)有128个RAM单元与软件接口,其中有11字节RAM用来存储时间信息,4字节RAM用来存储DS12C887的控制信息,称为控制寄存器14个作为字节时钟和控制寄存器,113字节通用RAM使用户使用。

(6)用户还可对DS12C887进行编程以实现多种方波输出,并可对其内部的三路中断通过软件进行屏蔽

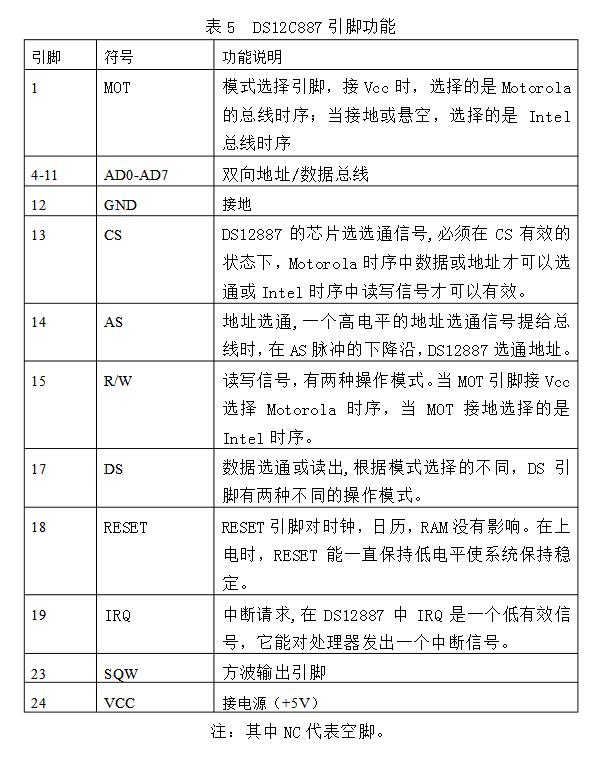

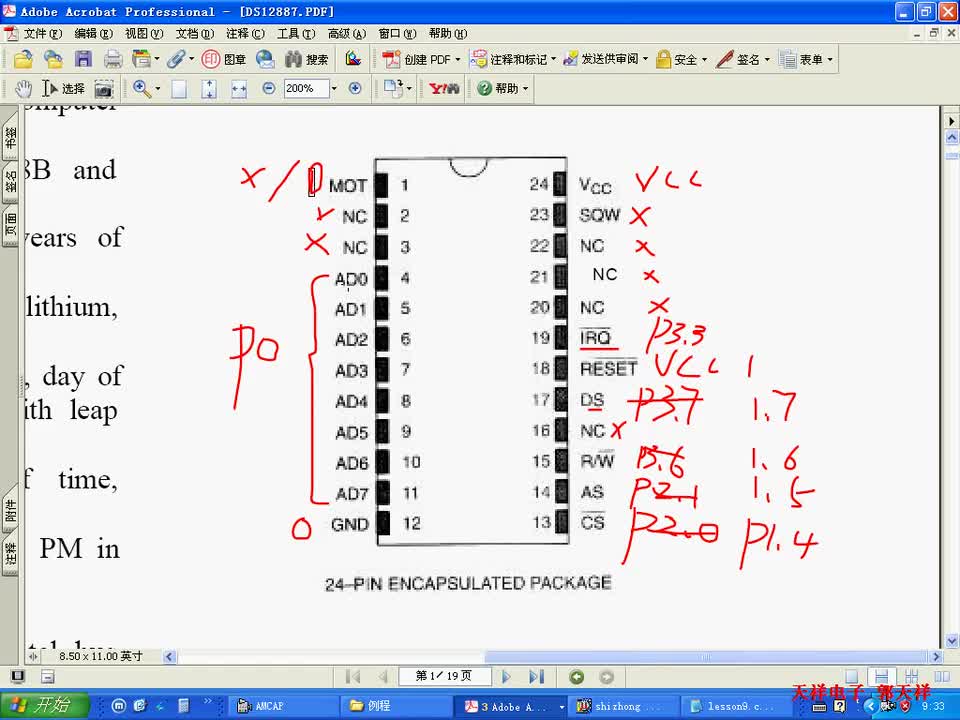

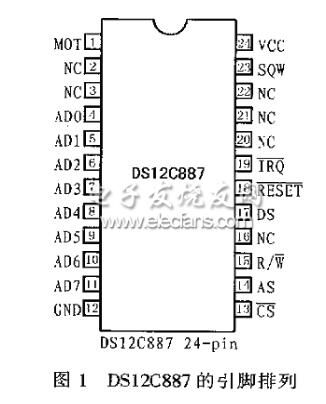

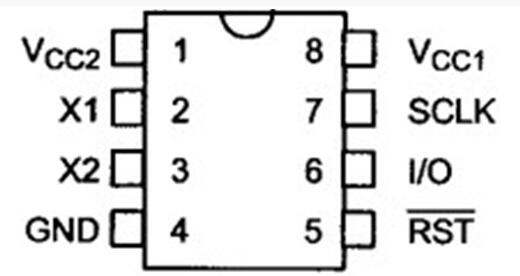

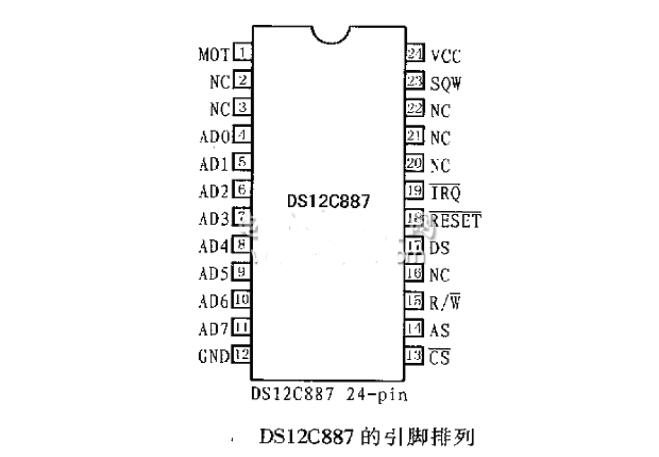

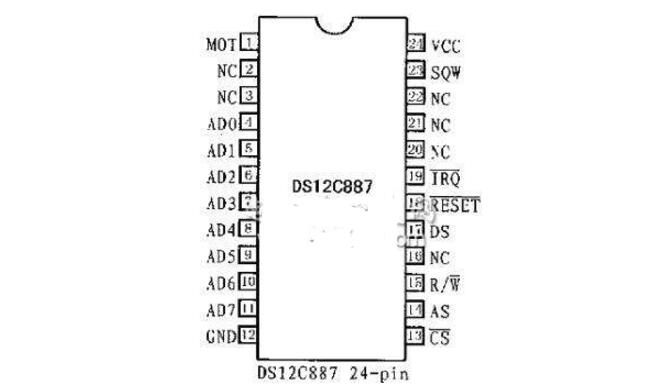

2)DS12C887引脚功能

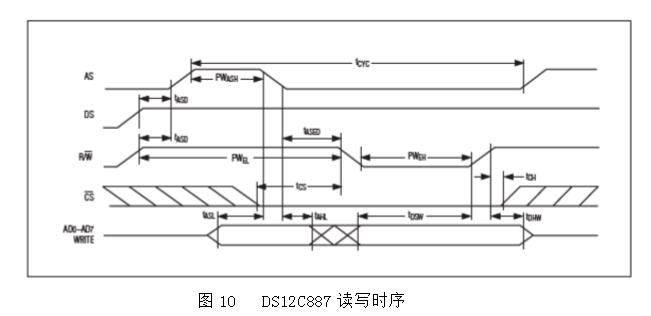

3)DS12C887读写时序

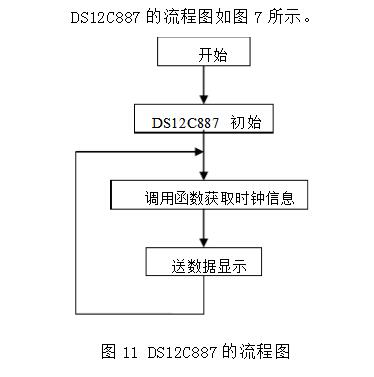

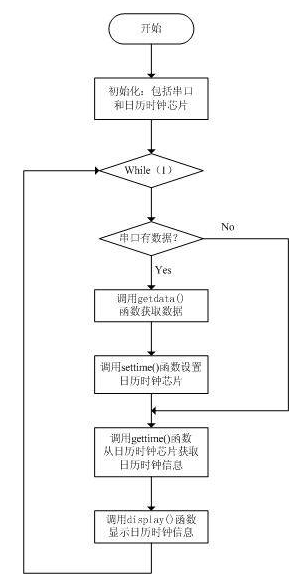

4)DS12C887流程图

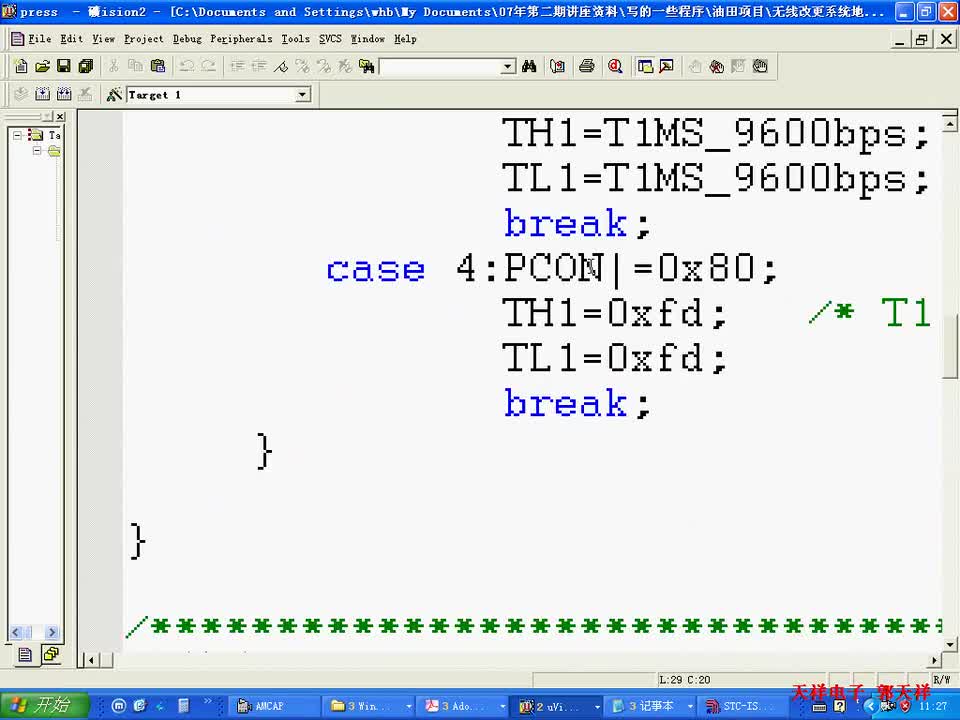

进入主程序后,DS12C887首先进行初始化设置,当串行口有数据时,则调用函数从日历时钟芯片获取日历时钟信息,调用显示函数显示日历时钟信息显示出来,重复进行。这部分包括DS12C887某个单元写、读DS12C887某个单元的内容 和DS12C887设定时间。

和DS12C887设定时间。

5)时钟芯片引脚介绍

1)时钟芯片DS12C887,其引脚分布图如下所示

MOT (1脚) :总线时序模式选择脚。接高电平时,选择MOTOROLA总线方式工作;接低电平或悬空时,芯片按照INTEL总线方式工作。此时其工作时序与MCS51芯片的片外RAM读写时序相伺。

NC (2,3,16,20,21,22脚):不解任何引脚。 AD0~AD7(4~11脚):地址/地址数据复用总线引脚。

CS(13脚):片选脚,低电平有效。

AS(14脚):地址锁存输入脚。引脚上的正脉冲用于切换地址/数据复用总线。脉冲后沿将地址锁入DS12887中,在Intel总线方式下,该脚等效于MCS一51系列单片机芯片的ALE脚。

R/W(15脚):读/写输入脚。此引脚有两种工作方式,在选择MOTOROLA总线方式下,此引脚用于指示当前的读写周期,高电平表示一个读周期,低电平表示一个写周期;选择INTEL中线时序模式时,此引脚为低电平有效的输入脚,相当于通用RAM的写使能信号(/WE)

DS(17脚):此引脚有两种工作方式,当MOT接高电平时时,此引脚为数据锁存脚;当MOT接低电平时,此引脚为读输入脚,在Mcs一51系统中,Ds相等于RD脚。·

RESET(18脚):复位输入,当 RESET为低电平且VCC≥4.25时,DS12C887芯片执行复位操作。该脚上的电压不影响时钟、日历及片内RAM的内容。

IRQ(19脚):中断申请输出脚,低电平有效,只要引起中断的状态位有效且相应的中断允许位为1,则IRQ变为低。微机需靠读寄存器C来清除该脚信号,RESET脚也可清除该信号。

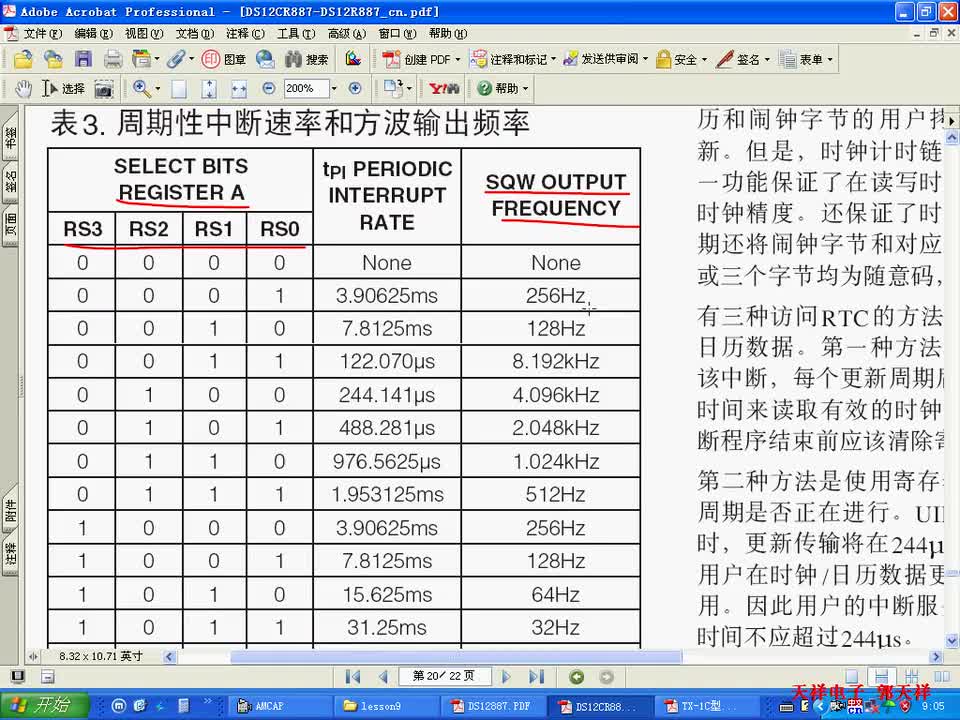

SQW(23脚):方波信号输出脚。可通过设置寄存器位SQWE关断此信号输出,此信号的输出频率也可通过对芯片内部的寄存器编程予以改变。

VCC(24脚):+5V电源端。当Vcc≤3v时,芯片内部自动将Vcc切换至片内置电池上,当VCC恢复为》4.25V后须经过100ms才能对它进行访问。

6)4个控制寄存器介绍

DS12C887有4个控制寄存器,在任何时间都可以进行访问,即使处于更新周期。

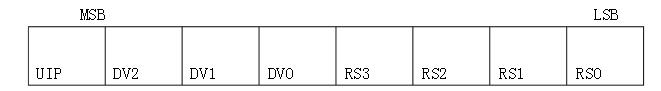

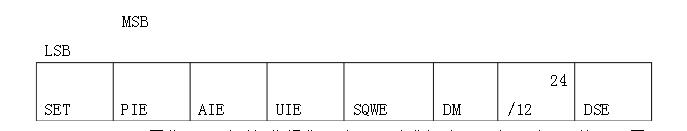

寄存器A字节的内容如下。

SET:设置位,不受到复位操作影响,可以进行读写。当0时,不处于设置状态,芯片更新时间数据;当1时,抑制数据更新,可以通过程序设定时间和日历信息。

PIE:周期性中断使能位,复位时清除此位,可以进行读写。当1时,允许寄存器C中的周期中断标志位PF,驱动/IRQ引脚向低产生中断信号输出,中断信号产生的周期通过RS0~RE3决定。

AIE:闹钟中断使能位,可以进行读写。当1时,允许寄存器C中的闹钟中断标志位AF、闹钟发生时就会通过/IRQ引脚产生中断输出。

VRT;RAM和时间有效位。用于指示和VBAT引脚连接的电池状态。此位不可写入,也不受操作的影响,一般的时候读取时总去为1,如果出现读取为0的情况,就说明电池没电了,时间数据和RAM中的数据就会变得不准确。

芯片DS12CR887的113字节普通RAM空间为非易失性RAM空间,可以在未处理器程序中作为非易失性内存空间使用。

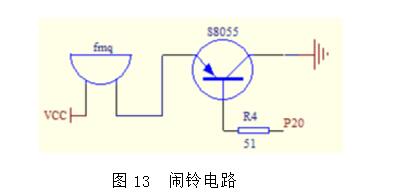

闹铃电路

闹铃功能是由单片机的I/O口输出一定频率方波信号,驱动蜂鸣器发出特定频率的声音信号实现的。当闹铃设置的时间到达时钟的时间时,单片机发送一个低电平给蜂鸣器,三极管导通驱动蜂鸣器发出声音作为定时闹铃。

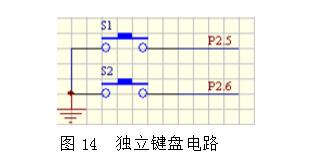

独立键盘电路

当单片机检测到有按键被按下时,就发射与之相对应的二进制编码信号

时钟的电源为+5V直流电源,本设计中可以使用4节1.5V电池,电源模块的原理图如图2-15所示

电子发烧友App

电子发烧友App

评论