描述此参考设计是基于 66AK2Gx DSP + ARM 处理器片上系统 (SoC) 和配套 AIC3106 音频编解码器的参考平台,可提供实现音频处理算法设计和演示的捷径。该音频解决方案设计包括

2018-10-19 15:35:45

DSP D 56371AF180 处理器是否包括 DSP B 56371AF180 的所有功能?也就是说,DSP D 56371 在其软件代码中有 Generic、mini-SA 和 PPP 作为其

2023-06-02 08:46:52

DSP处理器与通用处理器的比较1 对密集的乘法运算的支持GPP不是设计来做密集乘法任务的,即使是一些现代的GPP,也要求多个指令周期来做一次乘法。而DSP处理器使用专门的硬件来实现单周期乘法。DSP

2021-09-03 08:12:55

对比项属性/特征 硬件乘法器/累加器AUL 通用的MCU在执行乘法操作时是通过软件编程的方式的来实现的,通常需要几十甚至上百个时钟周期,而DSP处理器却有自己的硬件乘法器,使用硬件的方式来执行乘法

2021-11-03 08:41:44

怎样根据某些条件选择DSP处理器的类型?比如:要求数据输出时间间隔为1ms,速度数据类型为1个浮点型类型数据。急求大神指导!谢谢了!我对DSP处理器不太了解,暂时会用到这个技术。求指导!

2013-06-08 23:33:51

处理器存贮器的带宽加倍,更重要的是同时为处理器核提供数据与指令。在这种布局下,DSP得以实现单周期的MAC指令。 还有一个问题,即现在典型的高性能GPP实际上已包含两个片内高速缓存,一个是数据,一个

2011-01-07 15:34:45

指令。还有一个问题,即现在典型的高性能GPP实际上已包含两个片内高速缓存,一个是数据,一个是指令,它们直接连接到处理器核,以加快运行时的访问速度。从物理上说,这种片内的双存储器和总线的结构几乎与哈佛

2008-06-19 15:19:47

ADSP2106x的Link口组成多DSP互连并行系统 首先对ADSP2106x做一简单介绍。ADSP2106x是一种高性能的32 b数字信号处理器,采用超级哈佛结构。内有3条片内总线,他们是PM总线(程序存贮器

2019-04-08 09:36:19

本帖最后由 tianyi223 于 2015-9-9 20:34 编辑

两个dsp之间sci通信的话 数据会移位吗,会的话怎么解决,如果不会为什么发送正确,接收到的却是乱码

2015-09-09 15:30:07

我没有在当前文档中找到明确的答案:两个内核同时访问 SRAM 是如何处理的?内部 SRAM 是双端口的(我的意思是两个内核可以在没有额外等待状态的情况下寻址和访问同一个 SRAM),还是存在某种仲裁

2023-03-01 06:49:21

TI工程师,您好!我们计划两片DSP(28377)之间用SPI通信,还有一些DI和DO的信号交互。请问是否可以将两片DSP管脚直接连接在一起?是否中间需要串入电阻或者其他逻辑门器件?应用中有什么需要注意的地方吗?

2018-09-20 14:13:37

的是DSP133.33MHZ,当时钟上升沿来到的时候,读取DSP地址线上的数据,存入sram_wa中。lcd_sram1_d和lcd_sram2_d是从DSP的16根数据线上读出来的数据,通过原语存入这两个

2014-03-26 10:14:48

ADSP-21xx处理器包括片内振荡器电路,因此也可以使用外部晶体。晶体应通过CLKIN和XTAL引脚连接,两个电容器如图2所示连接。应使用并联谐振、基频、微处理器级晶体。 时钟输出信号(CLKOUT

2020-07-17 14:23:24

显示了运行在200MHz的处理器的性能基准。表2显示了各个产品的特性。如第1页图1中的功能框图所示,a DSP-2126x使用两个计算单元,在一系列DSP算法上比以前的SHARC处理器性能提高5到10

2020-10-14 16:59:05

SRU)。如第1页图1所示,处理器使用两个计算单元,在一系列DSP算法上比以前的SHARC处理器提供显著的性能提升。使用SIMD计算硬件,处理器可以在450mhz下运行2.7gflops,在

2020-10-12 17:17:43

性能要求同时保持足够的灵活性以满足多种应用的需求)的特定需求。配备了多达两个ARM®Cortex®-A15内核、两个C66x DSP内核、若干视频/图形加速器、一个四核可编程实时单元(PRU)以及两个ARM

2018-09-04 09:54:55

ARM946E-S™ 是一个可合成的宏小区,结合了ARM9E-S™ 带指令和数据高速缓存的处理器核心、带保护单元的紧密耦合指令和数据SRAM存储器、写缓冲区和AMBA™ (高级微处理器总线体系结构

2023-08-02 17:50:31

ARM946E-S™ 是一个可合成的宏小区,结合了ARM9E-S™ 加工机具有指令和数据缓存、紧密耦合的指令和数据SRAM的核心带有保护单元、写缓冲区和AMBA的存储器™ (高级微处理器总线体系结构

2023-08-08 07:33:30

ARM966E-S是一个可合成的宏单元,将ARM处理器与紧密耦合的SRAM存储器相结合。它是ARM9 Thumb系列高性能32位片上系统(SoC)处理器解决方案的一员,面向广泛的嵌入式应用,在这

2023-08-02 07:46:42

姚钢,EDN China资深记者Blackfin和SHARC处理器是ADI两大DSP产品线,目前一些在工控、测试测量的客户正转向超越MCU的DSP解决方案。例如,以太网(IEEE1588和802.3

2019-07-23 06:27:17

/Processor,数字信号处理),另外两个是MCU(Micro Control Unit,微控制器单元)和MPU(Micro Processor Unit,微处理器单元)。MCU集成了片上外围器件;MP...

2021-11-03 06:03:15

/Processor,数字信号处理),另外两个是MCU(Micro Control Unit,微控制器单元)和MPU(Micro Processor Unit,微处理器单元)。MCU集成了片上外围器件;MPU不带外围

2021-11-03 07:00:26

FPGA系统设计中,如果用两个FPGA工作,应该如何设计两片之间的通信?从片的配置和时钟输入与主片有何不同?一个做主片用于数据处理和控制,一个做从片用于IO扩展。硬件和软件上应该如何设计两片之间

2023-05-08 17:18:25

SPI Flash中代码搬到 SRAM中运行,应该如何操作?需要自行编程?

4. 看到有两个文件 SRAM.mac 和 SPIROM.mac ,其功能是什么?

2023-06-16 08:18:54

本文以MP3解码器为例,介绍了一种在嵌入式Linux系统下配置使用处理器片内SRAM的应用方案,有效提高了代码的解码效率,降低了执行功耗。该方案不论在性能还是成本上都得到了很大改善。

2019-09-24 07:09:13

本文以MP3解码器为例,介绍了一种在嵌入式Linux系统下配置使用处理器片内SRAM的应用方案,有效提高了代码的解码效率,降低了执行功耗。该方案不论在性能还是成本上都得到了很大改善。

2020-03-05 07:01:34

种布局下,DSP得以实现单周期的MAC指令。 还有一个问题,即现在典型的高性能GPP实际上已包含两个片内高速缓存,一个是数据,一个是指令,它们直接连接到处理器核,以加快运行时的访问速度。从物理

2014-04-17 10:45:08

分枝,一个是DSP(Digital Signal Processing/Processor,数字信号处理),另外两个是MCU(Micro Control Unit,微控制器单元)和MPU(Micro

2017-06-29 11:37:24

用于SHARC处理器的ADZS-21489-EZLITE,ADSP-2148x EZ-KIT Lite评估系统。 SHARC处理器基于32位超级哈佛架构,包括一个独特的内存架构,由两个大型片上双端口

2020-03-16 10:19:26

SPC58EC 有一个中断控制器,支持两个处理器。您可以为每个核心提供不同的向量表。假设两个内核处于活动状态并且发生了一个外部中断(ADC,定时器),这之后的过程是什么?哪个内核将运行中断处理程序?

2022-12-12 08:10:22

2106x只具有SISD(单指令流单数据流)功能。为了充分利用这种新的功能,一些指令做了一些改变。ADSP21160包括1个100/150MHz的运算核、双端片内SRAM、1个支持多处理器的集成在片内

2019-04-03 09:40:03

应用处理器与MCU“跨界”处理器—从性能差距到新解决方案领域降低成本—去除片内闪存集高性能、低延迟、高能效和安全性于一体相关行业和应用 i.MX RT跨界处理器

2021-02-19 06:06:39

通信的场合。特别适合于进行数字信号处理运算的微处理器,其主要应用是实时快速地实现各种数字信号处理算法。根据数字信号处理的要求,DSP芯片一般具有如下主要特点:(1)在一个指令周期内可完成一次乘法和一次

2017-11-17 14:10:37

ADSP2106x SHARC是一个适用于语音、通信和图像处理的高速32位数字信号处理器。该芯片是基于ADSP21000系列DSP芯片发展起来的一个完整的单片系统,增加了一个双口片内SRAM,并集成

2019-07-19 08:16:35

为什么要片内RAM大的DSP效率高?

2019-09-03 05:55:24

嗨,我有新的要求,我必须开发一台有10个电极和12个引线的心电图机,它将通过USB向PC机发送数据,PC机应用程序将显示心电信号。我对ECG系统设计是全新的,为什么需要DSP处理器?我需要开发哪个过滤器?问候,Akshay

2020-03-13 07:13:48

举例说明FPGA作为协处理器在实时系统中有哪些应用?FPGA用于协处理器有什么结构特点和设计原则?

2021-04-08 06:48:20

1.微处理器的两个发展趋势?2.常用可编程处理器有哪三种?3.单片机的结构特点和应用特点是什么?4.什么叫混合信号处理器?5.什么是“单片”解决方案?6. MSP430的工作电压多高?是多少位

2021-07-21 08:19:24

处理器,有TI的C66x系列、ADI的Blackfin系列。二、DSP处理器有什么特点?你可以把DSP处理器想象成一个科学计算器。它非常擅长做运算。1、并行性。某些型号的DSP处理器内部有两个独立的乘法器

2020-09-04 10:31:13

SRAM是当今处理器上最普遍的内存。当芯片制造商宣布他们已经成功地将更多的电路封装到芯片上时,通常是较小的晶体管引起了人们的注意。但是连接晶体管形成电路的互连也必须收缩。IMEC的研究人员提出了一个

2020-05-11 15:40:48

本文提出了一个通用微处理器(ARM)与DSP的接口设计方案,以实现两者的实时通信。

2021-06-08 06:36:41

端口SRAM(Dual-Port SRAM, DP-SRAM)凭借其两个端口可以同时进行读写的能力在SRAM 领域占有重要的一席之地,尤其在多核、实时信号处理系统中有着广泛的应用。 由于功耗的限制,片

2020-07-06 16:26:25

哪位大神关于《数字信号处理与数字信号处理器》的DSP论文,求分享。。。。

2014-05-27 16:25:52

视觉处理器(PVP),支持HD。像素合成器。全集成式DMA控制器,支持与所有片内和片外存储器和外设进行DMA传输。3个增强型并行外设接口(ePPI),支持最高24位的数据宽度、ITU-R BT.656

2018-08-30 11:41:29

两个方面的内容:IP核生成和IP核复用。文中采用IP核复用方法和SOC技术基于AVR 8位微处理器AT90S1200IP Core设计专用PLC微处理器FSPLCSOC模块。

2019-07-26 06:19:34

DSP并行系统。因为该系列的处理器在构成并行处理系统时其本身就提供了实现互连所需的片内总线仲裁控制和特有的链路口,可以以各种拓扑结构互连DSP,满足大运算量和片间通信灵活的要求。此外,选用ADSP

2019-05-21 05:00:19

,主机通过它可以直接访问DSP片内的一段RAM。在早期的DSP中,这段公用的RAM是一段2K字的双口RAM(对于TMSVC5402则可以访问所有的片内RAM)。当主机和DSP同时访问同一地址时,主机优先

2019-06-06 05:00:39

ADZS-21369-EZLITE,ADSP-21369用于SHARC处理器的EZ-KIT Lite评估系统。 SHARC处理器基于32位超级哈佛架构,包括一个独特的内存架构,由两个大型片上双端口

2020-03-16 10:19:26

内的高速互联总线和各个处理器交互数据。 和网络相关的片内设备如图1右下角灰色模块所示,主要包括两个对外的SGMII接口、以太交换和网络交换模块,以及用于数据管理的安全加速器和包加速器,是为了快速检测

2016-11-28 23:47:01

内的高速互联总线和各个处理器交互数据。 和网络相关的片内设备如图1右下角灰色模块所示,主要包括两个对外的SGMII接口、以太交换和网络交换模块,以及用于数据管理的安全加速器和包加速器,是为了快速检测

2016-10-15 22:43:53

,它连接到两个SRAM。考虑到PCB布局的困难(因为我们使用的是512k x 36个SRAM - 每个SRAM有36条数据线和19条地址线),建议两个SRAM具有相同的时钟频率,但有两个IO。请帮助我们继续最近的方法。我需要输入这些用于FPGA实现以及PCB上的布线。

2020-08-27 07:38:50

上的片内FIR和IIR硬件加速器也分别称为FIRA和IIRA,我们可以利用这些硬件加速器来分担FIR和IIR处理任务,让内核去执行其他处理任务。在本文中,我们将借助不同的使用模型以及实时测试示例来探讨如何在实践中利用这些加速器。

2020-12-28 06:26:54

我现在的板子上有两片C6678dsp,请问,如何在一个打开的CCS5界面下面创建用于这两个c6678DSP的工程,然后如何进行load和调试?还是说要打开两个CCS5界面?

另外,如果每个DSP我需要用两个核(0核和1核),那该怎么创建工程呢?是不是要创建4个工程,写4个main函数?

2018-06-21 05:21:59

如何去选择数字信号处理器 (DSP)?

2021-05-25 07:20:05

你好,我打算建立通信以在两个处理器之间读写。一方面是ASIC(MCIMX6)上的四核ARM Cortex A9处理器,另一方面是FPGA(ZC7020)。我在FPGA端没有任何PCIe硬端口。因此

2020-04-16 09:04:30

处理器DSP4、嵌入式片上系统SOC(System-on-a-Chip)三、多核处理器四、嵌入式操作系统EOS五、嵌入式实时操作系统RTOS六、嵌入式系统设计七、嵌入式系统的软件一、嵌入式微处理器体系结构1、冯诺依曼体系结构(1)程序和控制共用一个存储

2021-11-08 06:57:02

音频和视频通信的场合。特别适合于进行数字信号处理运算的微处理器,其主要应用是实时快速地实现各种数字信号处理算法。根据数字信号处理的要求,DSP芯片一般具有如下主要特点:(1)在一个指令周期内可完成一次

2017-04-26 09:37:34

概述:MM58167B是美国国家半导体公司生产的一款微处理器实时时钟芯片。作为总线型微处理系统中的实时时钟源,其内部包括一个可寻址的实时计数器、56bit片内RAM和两个输出中断,而且POWER DOWN引脚的有效信...

2021-04-20 06:53:56

微控制器:CPU + 片内内存 + 片内外设微处理器:CPU处理器通常指微处理器、微控制器和数字信号处理器这三种类型的芯片。微处理器(MPU)通常代表一个功能强大的CPU,但不是为任何已有的特定

2022-02-09 07:48:39

的运算,根据标志位跳转等。很少有微处理器具备这些强大的位操作能力,因为设计者在设计微处理器时,仅考虑以字节或更大的单位来操作数据。讲清楚了微处理器和微控制器的区别,还要补充一个概念,说说常用的DSP

2017-04-22 22:04:50

如题,本人在参与的一个项目,用到DSP TMS320C6472 六核处理器。准备使用其中两个核来相关处理。每个核的代码我已经写好,但是本人是DSP新手,现在不知道怎么链接.out文件使其从Flash

2013-12-16 09:12:49

本文以MP3解码器为例,介绍了一种在嵌入式Linux系统下配置使用处理器片内SRAM的应用方案,有效提高了代码的解码效率,降低了执行功耗。该方案不论在性能还是成本上都得到了很大改善。

2021-04-26 07:01:55

本帖最后由 luna 于 2011-3-3 13:12 编辑

不断发展的DSP技术迅速地拓宽扩展到了各应用领域,但传统的DSP处理器由于以顺序方式工作而数据处理速度较低,且在功能重构及应用目标

2011-03-03 10:05:43

用于SHARC处理器的ADZS-21479-EZLITE,ADSP-2147x EZ-KIT Lite评估系统。 SHARC处理器基于32位超级哈佛架构,包括一个独特的内存架构,由两个大型片上双端口

2020-03-13 09:35:38

ADZS-21262-EZLITE,ADSP-21262 EZ-KIT Lite评估系统,用于SHARC处理器。 SHARC处理器基于32位超级哈佛架构,包括一个独特的存储器架构,由两个大型片上双

2020-03-13 09:30:16

问个问题,能不能利用低成本前两三代的arm处理器来搭架一个万元内的超算?

2022-09-13 14:59:36

ADI 你好: 我想咨询下ADI的DSP处理器,因为一直没有使用过ADI的DSP的系列处理器,对此不熟悉。 我的应用是DSP读取ADC的信号(前端模拟电路都由ADI的模拟器件搭建并测试完成,目前

2018-11-02 09:18:18

等。很少有微处理器具备这些强大的位操作能力,因为设计者在设计微处理器时,仅考虑以字节或更大的单位来操作数据。 DSP芯片分类以及特点 数字信号处理器里的CPU是专门设计用来极快地进行离散时间信号

2017-10-27 15:51:04

做了一款基于arm处理器的SOC芯片,流片回来后测试发现,ARM能正常和片内SRAM和ROM通信,却不能和片外SRAM进行通信,请教高手,ARM不能和片外SRAM通信的可能的原因?

2022-06-10 15:50:38

请问SRAM 存储数据具体是怎么存储的? 还有就是在处理器和SRAM之间用VERILOG实现一个总线仲裁器怎么实现?谢谢高手指教!

2008-08-28 20:31:21

AVR对片内SRAM的访问需要多久?

2023-10-24 07:49:15

28027片内有两个比较器,想利用起来。从母线电流采集过来的信号输入片内比较器的一个脚,跟给定电压信号比较,超过后就翻转触发保护。可以这样做吗?

2020-07-22 14:58:01

我是QorIQ处理器的SRAM存储器接口(cy62167g18-55zxi)。我无法知道如何接口的#(Byte Low使)和他#(高字节使能)信号目前SRAM处理器。CY62167G18-5ZXI

2018-08-14 05:38:52

最近接触到了DSP处理器,关于定点处理器处理浮点运算有两个疑问,我是用C语言开发的,16位处理器,两个浮点数进行加减乘除,定点处理器运算出来结果的精度有多高,能保留几位有效数字??另外,关于定点

2019-05-13 01:09:48

来实施软件加密。相比传统 MCU,这是一个明显的优势。6、大存储容量在理想环境中,当可执行代码和数据被存储在片内 SRAM 中,并从此存储中执行 CPU内核操作时,嵌入式处理器的性能达到最高。即便在片内

2018-10-30 11:17:45

信号处理器(DSP),信号处理器(DSP)是什么意思

DSP是(digital signal processor)的简称,是一种专门用来实现信号处理算法的微处理器芯片

2010-03-26 14:53:54 15467

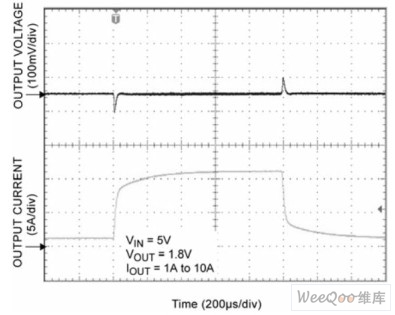

15467 为复杂的DSP处理器设计良好的电源是非常重要的。良好的电源应有能力应付动态负载切换并可以控制在高速处理器设计中存在的噪声和串扰。DSP处理器中的不断变化的瞬态是

2010-07-02 11:56:12 1714

1714

如何选择 DSP 处理器

2017-10-23 14:30:46 8

8

电子发烧友App

电子发烧友App

评论