IEEE1394是最初由Apple公司提出的高速串行总线,1995年IEEE(电气和电子工程师协会)将其认可为IEEE1394-1995规范[1]。但是在IEEE1394-1995中存在一些模糊定义[2],为了解决这些问题,又提出了IEEE1394a规范和IEEE1394b规范。1394作为一种成熟的总线,具有传输速率高(传输速率可达1.6 Gb/s,采用塑料光纤时可达3.2 Gb/s)、支持热插热拔、即插即用、拓扑方便等优点。被广泛应用于军事和航空业,更被美国航天局NASA确定为未来航天器的高速数据总线[9]。随着1394技术的推广和应用,将其应用到工业控制系统中更是一种趋势,而国内对1394总线在工业系统中的应用研究还不深入。本文主要介绍1394总线在TFT-LCD检测系统中的应用,通过实验证明了方案的可行性。

1 1394通信模块的硬件结构

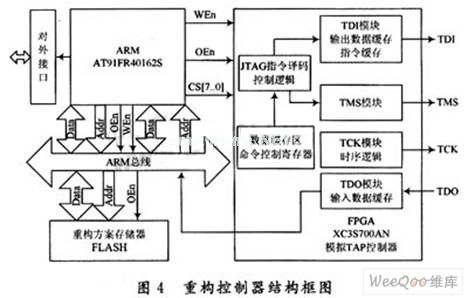

1394通信模块的主要功能为采集激光光斑的图像数据,负责图像采集板和Z-轴控制器以及PC之间的通信。它包括1394芯片(LLC和PHY)、FPGA、ARM7和2片SRAM。系统总体框图如图1所示。

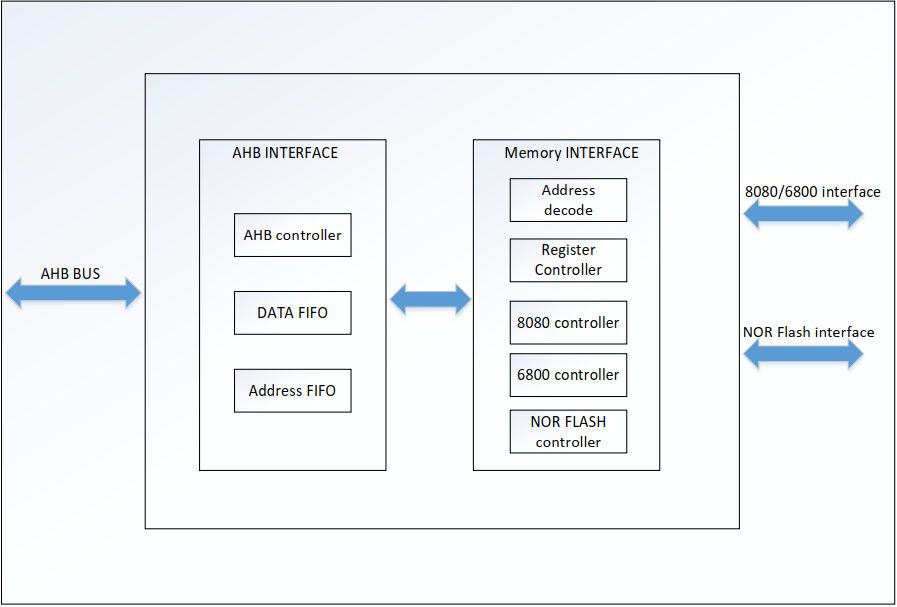

ARM7的主要功能是对1394芯片初始化,根据1394协议对经过FPGA转发的1394指令进行解析,控制1394链路层(LLC)芯片的数据接收和发送,以及通过链路层芯片间接地控制物理层(PHY)芯片。几乎所有的地址线、数据线和控制信号线都和FPGA相连,因此FPGA在整个1394通信模块中起着非常重要的作用,其实现的主要功能包括:(1)通过1394LLC芯片的“主机接口”配置ROM、初始化寄存器、设置中断、自标识和异步数据传输。(2)借助“DM端口”进行等时/异步数据的传输。(3)控制1394总线上数据的接收和存储。为了方便检测1394通信模块对指令的具体执行情况,在1394通信模块上扩展了一个串口,通过它与PC连接,即可在PC上通过软件实时监控1394通信模块的运行情况,也可以通过软件发送指令控制1394通信模块执行相应的动作。

相机的图像数据经过1394物理端口发送到1394总线上,经过1394链路层芯片和物理层芯片的处理,在ARM7和FPGA的控制下,通过乒乓操作的方式将其写入扩展的SRAM中。为了验证采集的图像数据是否正确,在1394通信模块上扩展了VGA接口。FPGA通过乒乓的方式读取SRAM中的图像数据,再通过VGA接口将数据输出到显示器上直观显示。

1394通信模块要与PC进行正常通信,必须先强制PC做为1394总线上的根节点。因此1394通信模块在接入1394网络后必须检测PC是否为根节点,否则要一直进行强制复位,直至PC为根节点。在PC为根节点后,两者之间就可以进行数据和指令的传输。另外,Z轴控制器可以通过1394总线接收来自PC或者1394通讯模块的运动控制指令。

ARM7芯片选用NXP公司的增强型LPC2200系列的LPC2292。FPGA选用Altera公司的Cyclone系列的EP1C6Q240C8。SRAM选用ISSI公司的IS61LV51216,用于缓存采集的图像数据,在后期进行图像处理或者显示。1394芯片选用TI公司的TSB12LV32(LLC)和TSB41AB3(PHY),这两款芯片兼容IEEE1394-1995和IEEE1394a-2000规范,并集成了3个支持400 MB/s传输速率的物理端口,TSB12LV32提供了8/16位可选择的MCU接口,支持异步传输和等时传输。

ARM7、FPGA、SRAM以及1394芯片(LLC+PHY)之间的连接如图2所示。

2 1394通信模块的软件设计

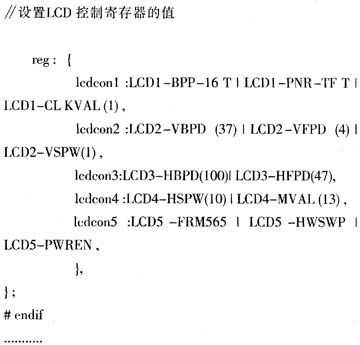

1394通信模块的软件设计主要包括ARM7-LPC2292和FPGA-EP1C6Q240C8的软件设计。根据功能的不同,ARM7的软件设计可以细化为ARM7的初始化、对LLC芯片指令的解析、对FPGA的读写操作以及和PC的串口通信。FPGA的软件设计可以分为对LLC芯片的读写操作、与ARM7的通信、控制VGA输出以及对SRAM的操作。

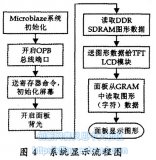

2.1 1394的初始配置

系统要正常运行,上电后的初始化配置非常重要。初始配置的作用为:(1)正确初始化配置ROM的内容,这是PC识别1394通信模块并正确安装对应驱动的前提。(2)如果是与PC通信,将PC设置为根节点。(3)TSB12LV32相关寄存器的初始化。主要包括DM Control寄存器(设置DM口的状态和一些参数),Interrupt(使能所有中断),Isochronous Port(等时传输的状态,设置每个物理端口的状态,等时数据包的事务标签等)。

1394配置流程如图3所示。

2.2 ARM7对TSB12LV32中断的响应

确保ARM7对TSB12LV32芯片指令正确响应的重要因素就是准确检测到TSB12LV32芯片的中断信号,并能够读取CFR寄存器的中断寄存器数值,根据具体的数值判断具体发生了哪种中断,清除掉中断位后,再根据中断类型决定要做出的反应。例如在检测到TSB12LV32的中断信号后,读取偏移地址为0x0C的中断寄存器数值,判断出bit9为1,即Data Mover packet received,则表明从DM口接收到了一个数据包。ARM7只需要清除该中断位即可。但是并不是所有的中断只对其中断位进行清除即可,而不需要做出其他响应。例如:bit18,FIFO acknowledge interrupt,表明先前从ATF传输的数据被1394接收节点成功接收,此时ARM7除了要清除中断位,还需要读取ACK代码的数值来确认1394接收节点是否做出了正确的响应。

2.3 LLC芯片配置ROM的实现

配置ROM的格式有最小格式和正常格式两种。执行事务的1394串行总线节点都应该实现配置ROM,它为配置和诊断与设备相关的问题提供了必要信息。一些1394控制芯片(如TSB43AA82A)可以对读取配置ROM的读请求自动响应,编程人员只要把配置ROM放在预先设定的区域内即可。但是本方案中选取的LLC芯片不具备这种功能,因此需要人为地对主机发送的读配置ROM请求做出正确的响应,以使配置ROM可以正确读到主机中。

1394通信模块需要充当总线管理器、循环控制器或者等时资源管理器,因此必须对其进行正常格式下的配置ROM。配置ROM的正常格式中主要配置项包含根目录(Root Directory)和总线信息块(Bus_Info_Block)。根目录提供了用来识别驱动程序和诊断软件的值,同时也提供了指向其他目录和数据结构的可选指针,这些指针指向的地址和根目录有相同的结构。总线信息块用来制定与总线相关的功能[2]。ARM7设置配置ROM的具体步骤如下:

(1)根据需要提供的信息填写配置ROM表,并根据IEEE1394-1995协议中提到的CRC校验算法计算校验值。

(2)对异步读请求数据包进行解析,分析到其为读事务,并且读的目标地址在配置ROM范围之内,则将分析的目标地址的数据填写到读响应数据包中,对读请求做出响应。

上位机正确地读取到配置ROM的内容后就会提示发现新的硬件,识别出1394通信模块后自动为其安装相应的驱动程序。

2.4 IEEE1394等时数据传输的实现

实现等时数据传输,需要先做以下准备工作:具有两个或两个以上的1394节点,至少有一个节点具有充当等时资源管理器的资格,将要发送等时数据的节点DM口模式设置为传输模式(transmit mode),同时将接收等时数据的节点DM口模式设置为接收模式(receive mode)。等时数据传输分为自动插入包头和手动插入包头两种;等时数据接收分为自动去除包头和包尾以及包头和包尾一起接收两种情况。为了方便后期的数据处理,将等时数据发送节点的等时模式设置为自动插入包头和包尾,而将等时数据接收节点的等时模式设置为自动去除包头和包尾。

自动插入包头的等时数据传输流程如下:

(1)接收到DMREADY一个周期的高脉冲信号。

(2)DMDONE置为低电平。

(3)DM口读取自动存储在38h地址的包头信息,并向链路核请求将要发送的数据读取到1394总线上。

(4)链路核获得header0寄存器存储的头信息。

(5)DMPRE产生一个周期的高脉冲。

(6)DMRE为高电平时,开始获取要发送的数据。

(7)链路核读取到最后一个数据时,DM口开始检查是否向控制寄存器所定义的通道发送了数据。如果已经向所有的通道发送完毕,则在经过一个小间隙后将DMDONE置为高电平,此时等时传输结束;否则DM口继续插入头信息,进行数据传输,直至向所有的通道发送完数据。

自动去除包头和包尾的等时数据接收流程如下:

(1)包头中的sysc位如果和等时接口寄存器(地址为0x18h)的ISYNCRCVN信息相同,DMPRE置高一个周期。

(2)在接收完包头后,DMDONE置高一个周期。在后面有数据通过时DMRW置高。

(3)在接收完所有的数据后,DMRW置低,则DMD数据线不接收包尾。

3 通信测试

对1394通信模块的通信实验分为两部分:对1394协议所规定的通信功能的测试;对采集到的数据正确性进行验证。实验步骤如下:

(1)将1394通信模块和PC连接起来,模块加电后,首先进行总线配置、树标识和自标识。在整个网络形成后,已经确定根节点,各个节点的地址也就确定了。在1394总线执行上述动作时,同时通过扩展的串口输出自标识数据包的内容,包括当前网络中的节点数、当前节点为第几个节点、是否为根节点、是否具有等时资源管理的功能。至此,1394通信模块已和PC建立连接。

(2)通过PC读取1394通信模块的配置ROM,看其是否能进行正确响应。

(3)进行异步读和异步写的测试,分为对字节的异步读写和对数据块的异步读写两种。

(4)进行等时数据传输的测试。看PC是否能接收到1394通信模块发出的等时数据包。

(5)连接相机,通过等时传输将相机的图像数据存入到1394通信模块的SRAM中,并由VGA接口输出到显示器上显示。

除了第(5)步,以上每一步的执行都会在串口调试助手软件上有结果输出。例如:1394通信模块在上电后收到自标识包并进行复位,并在调试界面上会输出“SID RCVD 2 Y 0 BUS RST..”。其中“SID RCVD”表示节点收到自标识数据包,“2 Y 0”表示当前总线中存在两个1394节点,当前节点为根节点,具有等时资源管理功能的节点是节点0。“BUS RST..”表示节点开始进行总线复位。当前节点发起读取0x0400地址数据的异步读请求,则在界面上会显示“ACK00010,0x04049c44”。“ACD00010”表示另一个节点接收到了异步读请求的命令,“0x04049c44”则为返回的0x0400地址存储的数据。两个1394节点要进行等时数据传输,假如数据发送方为节点0,数据接收方为节点1。按照以下步骤进行节点间等时数据传输的测试:(1)先设置节点0的DM口模式为发送模式,节点1的DM口模式为接收模式。(2)节点0先读取总线上的有效带宽,上层界面接收到“0x00000f33”,它是用十六进制表示的当前总线的有效带宽。节点0再向等时资源管理节点申请一定的带宽,上层界面接受到“ACK 00010”,表示带宽申请成功。(3)读取总线上的有效通道并且申请通道。1394总线的有效通道数存在两个寄存器上,申请时按照由低到高的顺序。在申请通道前需先确认当前网络中使用的通道数,通信结束后再释放该通道。发出读取有效通道的指令后,上层界面接收到“0xffffffff”和“0xffffffff”,表示目前总线上所有通道均处于空闲状态。可以申请通道1,申请后低位通道寄存器的值变为“0xfffffffe”。经过前面三步已经建立了节点0和节点1进行等时通信所需要的带宽和通道。(4)发送等时传输的指令,看节点1是否接收到了指定量的等时数据包。通过中断寄存器的bit9(Data Mover packet receive)进行判断。

本文分析了基于FPGA+ARM的1394总线在TFT-LCD检测系统中的应用,对于1394总线技术的推广具有较强的借鉴意义。测试实验表明,1394总线在进行等时通信时分配固定的带宽,保证了图像数据又快又准的传输,同时整个检测系统的各个模块通过1394总线连接起来,可以完全脱离PC单独运行,采用异步传输进行控制指令的传输,既方便又稳定。

电子发烧友App

电子发烧友App

评论