漫谈系列的前两期分别介绍了 MM32F5270 所采用的 “星辰”STAR-MC1 处理器和多并发总线架构设计,相信读者在读完了前面的介绍后,已经对 MM32F5270 的高性能设计特点有了一定的了解。本期,笔者接着来聊聊在 MM32F5270 中首次采用的外设间互联矩阵 MindSwitch 和组合逻辑单元 CLU,看看 MM32F5270 是如何通过 MindSwitch 和 CLU 来实现可任意编程、任意重组的外设间互联系统的。

注:为避免读者把外设互联和上期谈到的总线互联混淆,这里做一个简单的解释。总线互联指的是CPU、DMA 等总线 Master 和存储、外设等总线 Slave 间的数据传递,而外设互联指的是外设间的控制信号的交互。

痛点:IP-to-IP

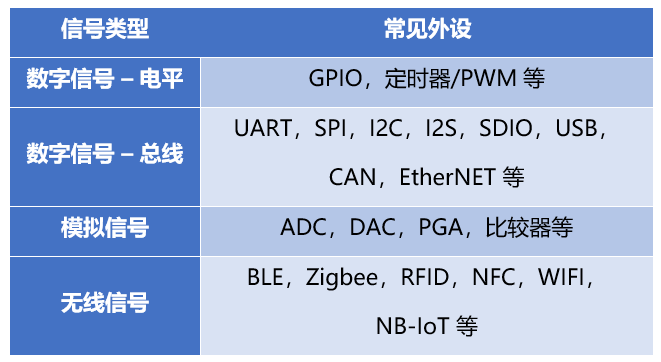

MCU 中文翻译为微控制器,可以定义为使用处理器来控制外围设备以实现和外部世界交互的控制单元,这里的交互包括外部信号的采集、通信以及对外部电路的控制。因此, MCU 一般具备比较丰富的外围设备(外设,Peripherals),常见的外设如下表所示:

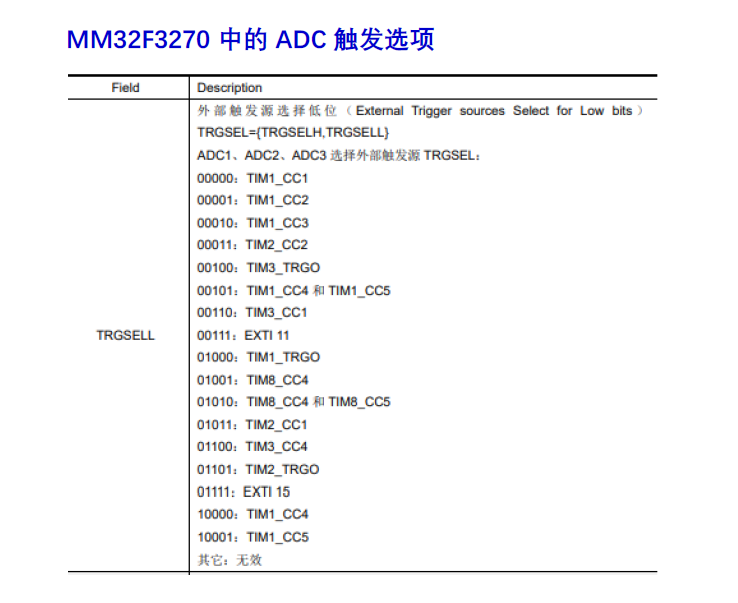

需要补充说明的是,上表中仅仅列举了外设的类型,而在一个 MCU 中,其每种外设的数量可能是有很多个的,这样一来,所有外设的数量就变得很庞大。 而在实际应用中,这些外设往往不是孤立的,很多情况下都需要多个外设间的协同配合去实现某项功能,典型的例子如电机控制系统,这类系统中往往需要 ADC、定时器、PWM等模块间的精确同步。因此,当这些数量庞大的外设间需要交互时,如何高效便捷的管理成了芯片设计中的一个主要难题(芯片设计人员一般将此叫做 IP-to-IP 设计)。 而 MCU 的一个主要特点是其面向的应用非常广泛,这就导致不同的用户对于外设资源的使用千差万别,外设间的同步逻辑更是各不相同。 为满足不同应用的需求,就需要外设间的互联做到灵活可配。但在很多市面上常见的 MCU 中,外设间的同步逻辑是固定的,是软件无法配置的。这种 IP-to-IP 设计虽然能够满足一些典型应用的需求,但确无法满足所有用户的需求。 以灵动的产品为例,MM32F3270 和 MM32F5270 中均配备了2 个 5 通道高级定时器和 4 个 4 通道通用定时器,每个定时器都有一路触发脉冲输出(TRGO 信号,具体含义参考用户手册),同时定时器的每个通道都可以产生一个触发脉冲输出,因此,这里一共有 32 个触发脉冲信号,这些脉冲可用于触发其它模块的执行,如触发 ADC 的采样和 DAC 的转换,或触发其它定时器的计数以实现多计数器间的同步。 以定时器触发 ADC 采样为例,传统的做法是根据应用经验,固定几种常见的触发方式,这里可以参考 MM32F3270 中的做法,如下图所示。可以看到,这里 ADC 的触发源是通过一个 5 位的 TRGSEL 寄存器来选择的。 这里主要有两个局限: 触发源有限 这里的触发源仅覆盖了 32 个触发脉冲信号中的半数,例如如果用户想选择 TIM1\_TRGO,或者 TIM2\_CC3 等来触发,这里是无法实现的 触发源的组合有限 假如用户需要在 1 个 PWM 周期内多次触发 ADC,则需要多个触发源的逻辑组合(OR 运算),但这里支持的信号组合非常有限。

互联矩阵 MindSwitch

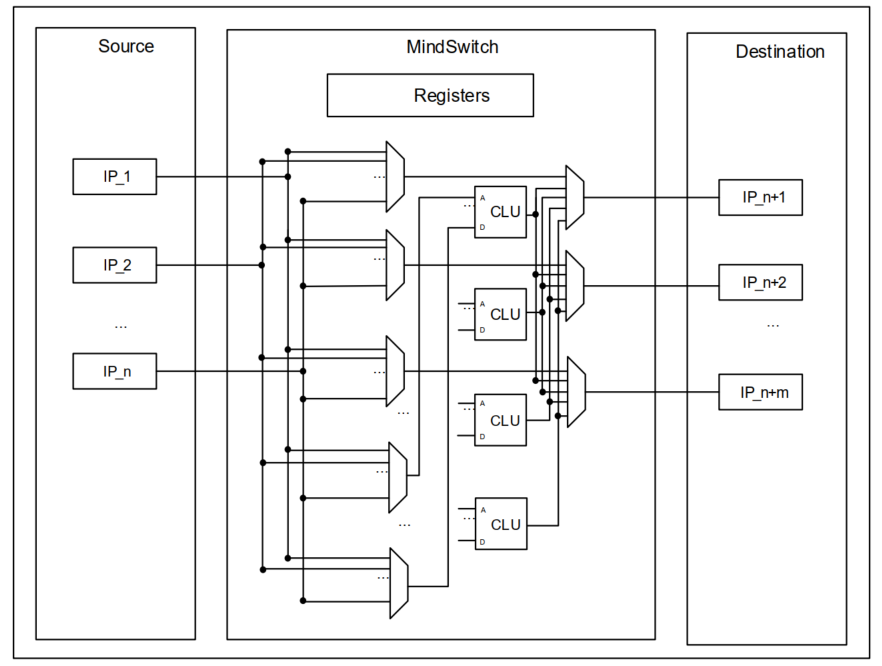

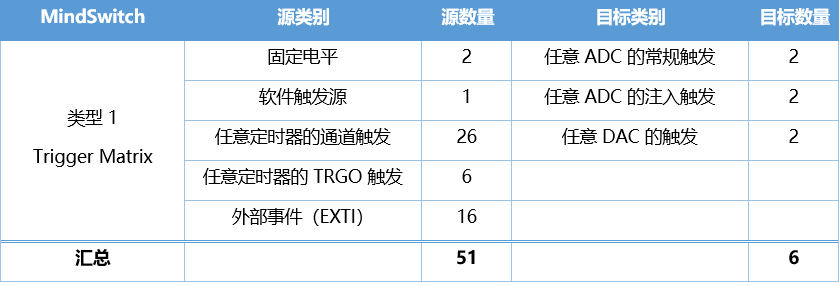

MindSwitch就是针对这一痛点而设计,实现了可以任意编程、任意重组的 IP-to-IP 互联网络。MindSwitch 将系统常用的触发源都连接到了其输入端,解决了触发源限制;而 MindSwitch 内置的组合逻辑单元 CLU (Combinational Logic Unit) 则支持任意信号的逻辑组合,解决了触发源组合限制。 MindSwitch 和 CLU 的构造如下图所示,其主要特性包括: 分为触发矩阵(Trigger Matrix)和连接矩阵(Connection Matrix) 可配置触发源和触发目标

触发源和触发目标可自由配置

支持外设硬件触发和软件触发

内部集成四个组合逻辑单元 CLU,提供 OR-OR 组合逻辑操作

可配置连接源和连接目标

连接源和连接目标可自由配置

内部集成四个组合逻辑单元 CLU,提供多种组合逻辑操作

支持不同时钟频率的触发源和触发目标之间协同工作 读者可以把 MindSwitch 理解成两个独立的 M 到 N 映射矩阵,其中 M 是源的数量,N 是目标数量,任意源可以映射到任意目标上。

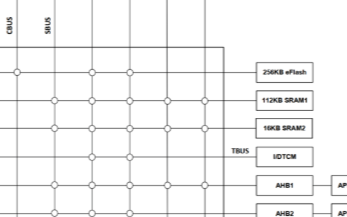

这里,触发指的是边沿触发(上升沿、下降沿),而连接指的是电平信号的直连。 在 MindSwitch 内部,这两种类型的互联矩阵是互相独立的,即 MindSwitch 内部包含了 1 个触发类型互联矩阵(Trigger Matrix)和 1 个连接类型 互联矩阵(Connection Matrix),两个 Matrix 互相独立,互不干扰,触发源仅能连接到触发目标上,而连接源仅能和连接目标相连。 这里 CLU 是一个 4 输入 1 输出的组合逻辑单元,后文会有更具体的介绍,这里先跳过。 用户可将任意触发源连接到任意触发目标上,或者通过 CLU 将任意 4 个触发源进行 OR-OR 逻辑组合后连接到任意触发目标上。这里的配置都是软件编程的,即用户可以根据其应用场景的需要进行任意配置。 触发和连接的区别是,触发信号需要 MindSwitch 做同步处理,且触发信号仅支持 OR-OR 逻辑操作。 下表整理了 MM32F5270 中的所有源和目标的数量和类别,具体列表可参考芯片的用户手册。

组合逻辑单元 CLU

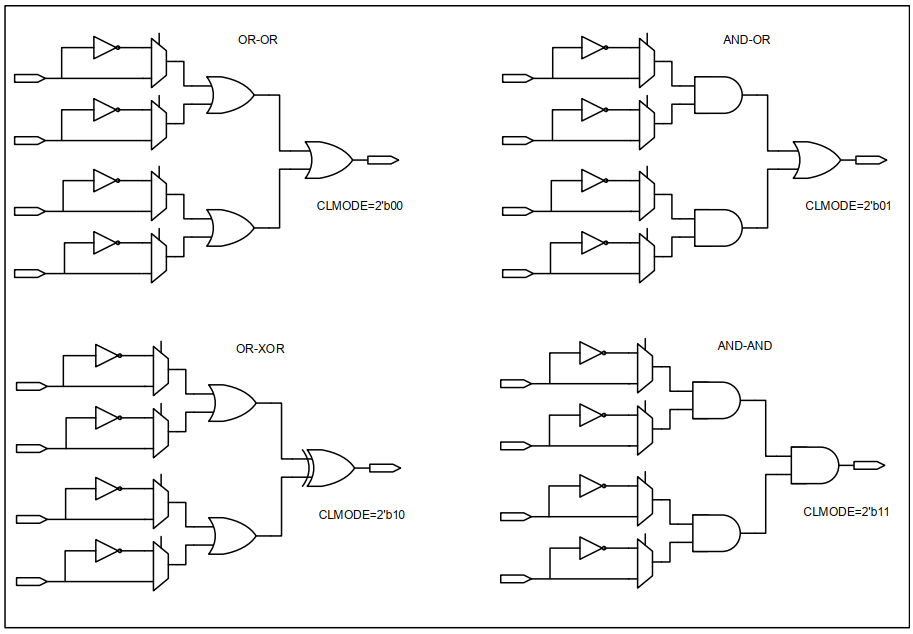

上文已经提到过 MindSwitch 中内置了 4 个 CLU 单元 (CLU0~CLU3),CLU 的全称是 Combinational Logic Unit,即组合逻辑单元。顾名思义,即实现与、或、非等组合逻辑运算的单元。 每个 CLU 都是一个 4 输入 1 输出的单元。4 个输入命名为 CLUxIN0~CLUxIN3,这里将 CLUxIN0 和 CLUxIN1,CLUxIN2 和 CLUxIN3 两两组合(第一级组合),再将组合后的信号进行组合(第二级组合),得到 CLUx 的输出。CLU 的运算类型根据两级组合的不同进行区分,可以分为:

OR-OR

AND-OR

OR-XOR

AND-AND

以 AND-OR 为例,即CLUxIN0 和 CLUxIN1 做逻辑与(AND)运算,CLUxIN2 和 CLUxIN3 做逻辑与运算,两者的结果再进行逻辑或(OR)运算,其逻辑表达式如下: CLUxOUT = (CLUxIN0 & CLUxIN1) | (CLUxIN2 & CLUxIN3) 具体四种模式的电路图如下图所示。 对于 Connection Matrix,每个 CLU 都可以通过 CLUMODE 寄存器来配置成上述任意模式;对于 Trigger Matrix,仅支持 OR-OR 操作。 对于很多应用场景,用户可能仅需要 2 个或 3 个信号的逻辑组合,此时,用户只需要将空闲的一路或多路 CLUxINx 选择为固定电平即可。同时注意到,任意 CLU 输入都可以选择逻辑取反操作,这大大增加了 CLU 的灵活性。

实例说明

经过上述介绍,读者可能还是无法直接感受到 MindSwitch 和 CLU 的强大。这里,以几个典型用例来进一步说明。

单电阻 FOC 中的 ADC 采样控制

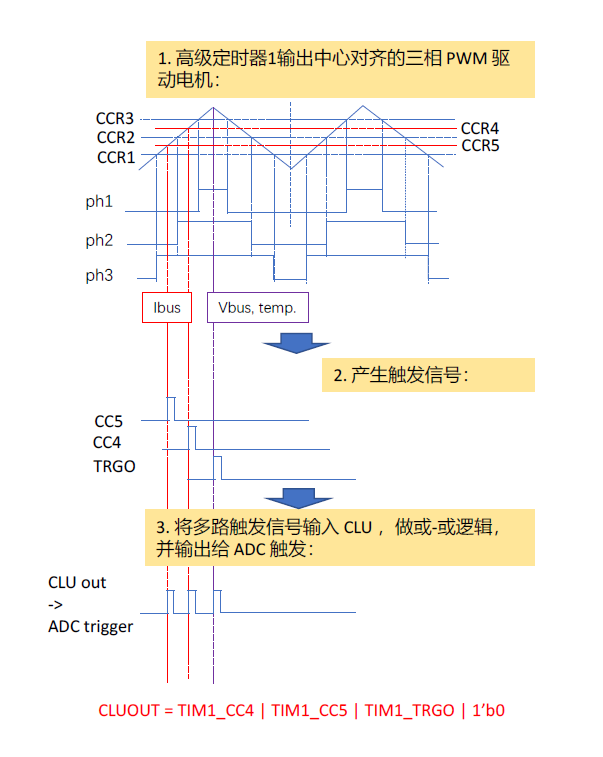

在单电阻 FoC 控制中,需要在一个 PWM 周期内依次采集两相电流、母线电压和环境温度等信息。因此,需要在一个 PWM 周期内触发多次 ADC 的采样,这里以 3 次为例说明。 还是以 MM32F3270 为例,参考上文中 MM32F3270 的 ADC 触发源配置表,可知 MM32F3270 的多路触发源仅支持 TIM1 或者 TIM8 的 CC4 或 CC5 触发,因此其驱动电机的时候的资源分配是这样的:

通过 TIM1 的通道 1、2、3 来做为三相电机的驱动,而通道 CC4 和 CC5 用于触发 ADC 的采样。

可以看出,这样的操作有两个弊端:

1 个 PWM 周期仅能触发两次 ADC 采样,如果想要实现更多的采样,则需要采用更复杂的软件手段

假如使用其它定时器(TIM2/3/4/5)去做触发,则仅支持最多一次采样

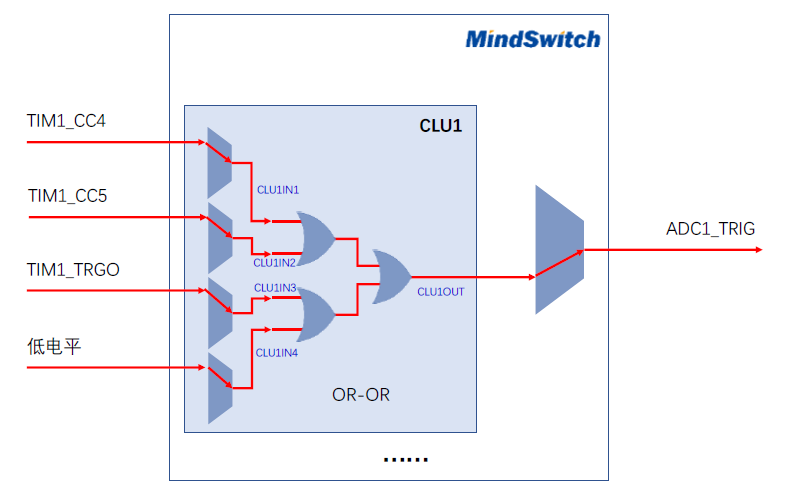

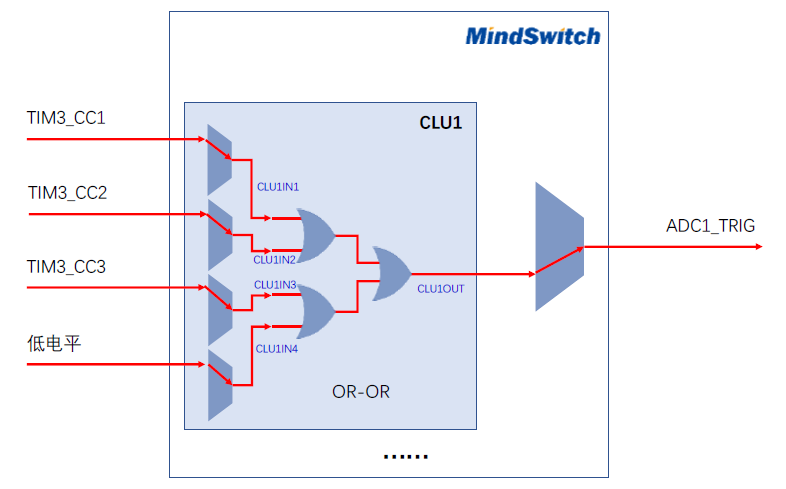

而MM32F5270 采用 MindSwitch 可实现单 PWM 周期内任意时刻的 4 次 ADC 触发。 还是以上述应用场景为例,依然用 TIM1 的通道1、2、3 来驱动电机,但 ADC 触发部分可以有以下两种优化方法: 方法1 用 TIM1 的通道 4、5 触发(CC4/CC5)加上 TIM1 的 TRGO 信号做触发源,这三个信号通过 OR-OR 逻辑组合,再送到 ADC 做触发。可实现每个 PWM 周期触发 3 次 ADC 采样。 方法2 用 TIM3(或其它通用 4 通道定时器)的通道 1、2、3 (CC1/CC2/CC3)来做触发,这三个信号通过 OR-OR 逻辑组合,再送到 ADC 做触发。可实现每个 PWM 周期触发 3 次 ADC 采样。

注:方法2 需要确保 TIM1 和 TIM3 是严格同步的。

方法 1 的优点是仅通过 TIM1 搞定一路电机的驱动和采样。但如果定时器资源还有富余,则可以采用方法2。如果将 TIM3 的 CC4 或者 TRGO 信号也利用起来,则方法 2 能轻松实现每个 PWM 周期触发 4 次 ADC 采样。 方法1 的内部连接示意如下:

方法2 的内部连接示意如下:

方法1 的整个步骤和定时器计数和触发波形如下图所示。读者可以试着自己推导 方法 2 的定时器波形和 CLU 逻辑表达式。

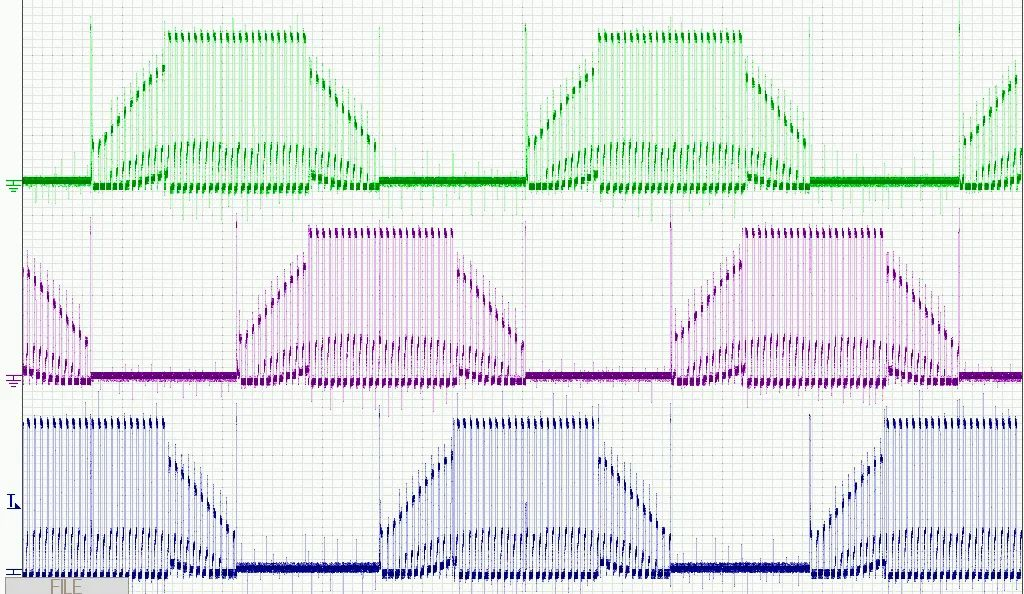

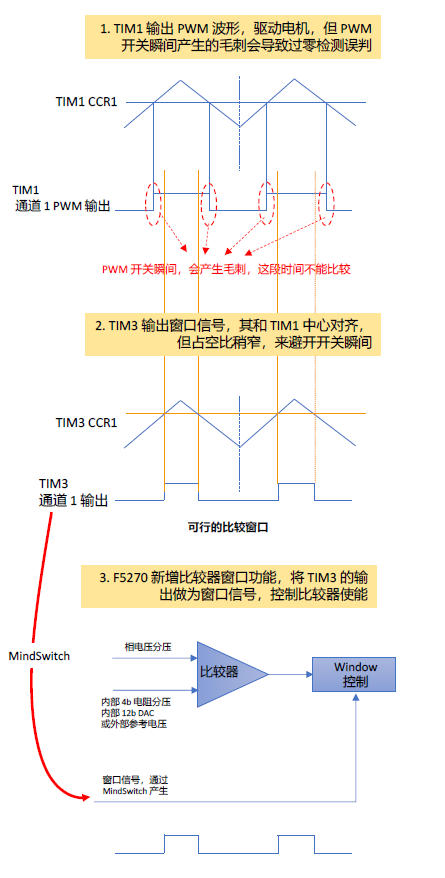

在 Sensorless BLDC 电机控制中,往往通过检测反电动势来判断电机当前所处的位置,而其中的关键在于对反电动势过零点的判断。这里,一种比较快速的方法是通过芯片内置的高速比较器来判断。 MM32F5270 中就包含了 3 路高速模拟比较器(COMP),可分别检测三相反电动势的过零点。 但真实情况下,MOS 管在导通和关断的瞬间会在反电动势上产生较大的毛刺,如下图所示。这个毛刺会导致比较器误判,因此,需要通过某种方法让比较器在 PWM 开关瞬间不工作。 传统的方法往往需要通过复杂的软件干预,如通过中断去定期使能和关闭比较器等。但这种方法会额外占用 CPU 带宽,特别是对转速要求较高的场景有较大限制。

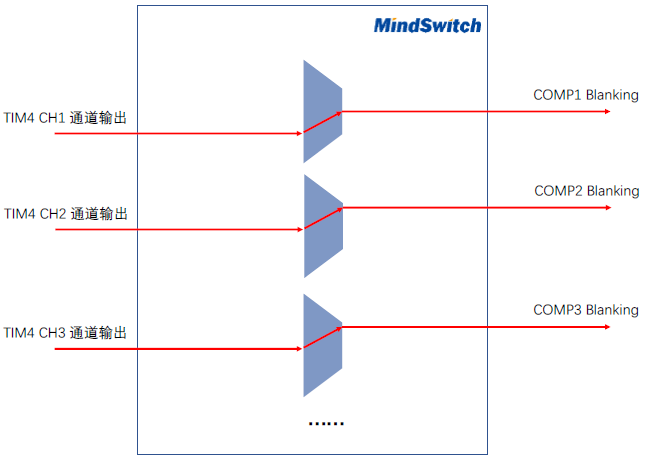

而MM32F5270 通过 MindSwitch 和比较器的窗口功能可实现全硬件过零检测。 首先,MM32F5270 在模拟比较器中新增了窗口使能控制,仅在窗口信号有效时,比较器的输出结果才有效。 同时,可以采用某个定时器的输出通过 MindSwitch 连接到比较器的窗口信号上。 如果仅采用单个 TIM 通道输出,则不需要 CLU 的参与;如果需要多路信号逻辑组合后来产生一个更复杂的窗口信号,则可加入 CLU 运算。

整个步骤和定时器计数和触发波形如下图所示:

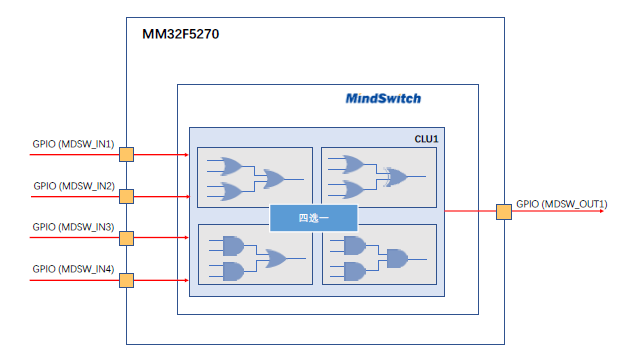

替代外部逻辑器件

在很多应用中,用户可能需要对某些信号进行逻辑组合,常见的逻辑运算包括与运算、或运算、非运算(取反)等基础单元以及更复杂真值表的组合逻辑运算。一般情况下,用户需要额外购买逻辑芯片(如 74 系列)来实现上述功能。 MM32F5270 通过 CLU 可以覆盖简单的逻辑芯片,从而帮助用户节省 BOM 成本。 这里,用户可以把需要进行逻辑组合的信号从 GPIO 输入,进入 CLU 进行逻辑组合,并将 CLU输出通过 GPIO交回给板级电路。此时的 MindSwitch 内部连接如下图所示:

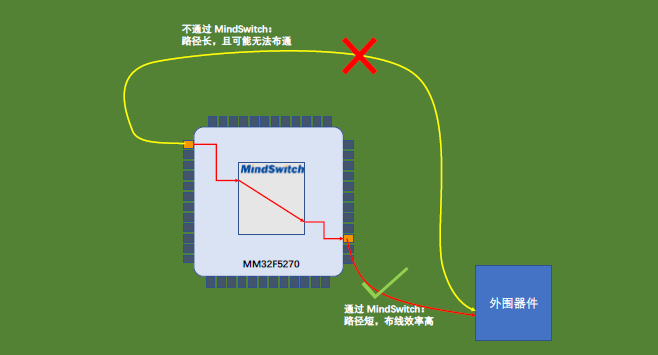

更灵活的 PCB 布线

在实际应用中,用户可能会遇到下面这种情况: 在芯片的引脚分布上,某个引脚的脚位和其相关外围电路的距离较远,从而导致无法通过单层布通。此时,如果功能引脚的脚位是可调的,就能很好的解决这个问题。 MM32F5270 也将这个功能集成到了 MindSwitch 中,可通过 MindSwitch 实现灵活的 PCB 布局布线。 如下图所示。假设 TIMER 输出的引脚是分布在芯片的左上角(橘黄色高亮),而其对应的外围电路位于 PCB 的右下角(蓝色方框)。可以看到,如果没有 MindSwitch,TIMER 输出需要很长的路径才能绕线到 PCB 右侧的外围器件上(如图中黄色路径)。这个路径是比较长的,且当布线层数较少时,可能无法成功布通,此时用户需要调整其原有的布局,PCB 布线的难度提高。 而通过 MindSwitch,用户可以将 TIMER 的输出连接到 MindSwitch 输入,并通过 MindSwitch 将其连接到芯片右下角的 GPIO 上 (橘黄色高亮),再以较短的路径连接到外围器件。通过 MindSwitch 给用户的布局布线提供了更高的灵活度。

除了上述提到的 4 种典型应用场景,MindSwitch 和 CLU 还可以用于支持以下场景: 方便用户调试 – 用户可以将内部信号通过 MindSwitch 引出到片外通过示波器等观测。 灵活的波形组合 – 在一些复杂的应用中,需要用到非常规的控制波形,这样的波形可以通过多个定时器的输出波形进行逻辑组合产生。 需要强调的是,MindSwitch 和 CLU 的最大优势就是可以任意编程、任意重组。 笔者相信,我们的用户一定还可以将它们扩展到更多、更有趣的应用场景,让我们拭目以待吧。

小结 & NEXT

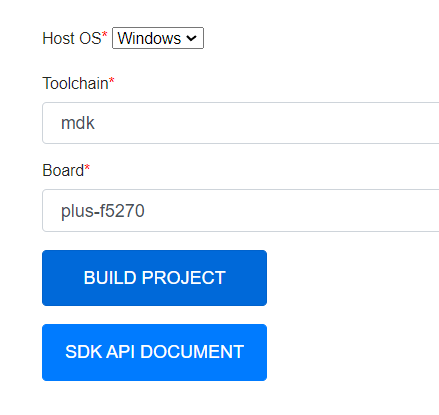

本文介绍了MM32F5270 中引入的全新外设间互联矩阵 MindSwitch 和组合逻辑单元 CLU 的功能和原理,并通过一些实例说明了 MindSwitch 和 CLU 对应用所带来的帮助。 未完待续!本文是 MM32F5 漫谈系列的第三篇,后续将为大家持续更新,旨在分享 MM32F5 系列中所包含的那些有趣的技术,敬请期待! 关于灵动 灵动成立于 2011 年,是中国本土领先的通用 32 位 MCU 产品及解决方案供应商。公司基于 Arm Cortex-M 系列内核开发的 MM32 MCU 产品拥有 F/L/SPIN/W 四大系列,目前已量产 200 多款型号,累计出货数亿颗,每年都有近亿台配备了灵动 MM32MCU 的优秀产品交付到客户手中,在本土通用 32 位 MCU 公司中位居前列。

灵动客户涵盖智能工业、汽车电子、通信基建、医疗健康、智慧家电、物联网、个人设备、手机和电脑等应用领域。灵动微电子是中国为数不多的同时获得了 Arm-KEIL、IAR、SEGGER 官方支持的本土 MCU 公司,并建立了独立、完整的通用 MCU 生态体系,可以为客户提供从硬件芯片到软件算法、从参考方案到系统设计的全方位支持。

审核编辑 :李倩

电子发烧友App

电子发烧友App

评论