MCS-51是Intel公司生产的一个单片机系列名称,该系列生产工艺有HMOS和CHMOS这两种,CHMOS是CMOS和HMOS的结合,既保持了HMOS的高密度和高速度,还具有CMOS低功耗的特点。

在产品型号中,带有字母C的即为CHMOS芯片,如80C51,该类型芯片的电平既与TTL兼容,又与CMOS电平兼容。

在片内程序存储器的配置上,该系列单片机有3种形式,即掩模ROM、EPROM或Flash和ROM Less(无片内程序存储器)。

80C51是MCS-51系列中采用CHMOS工艺的一个典型品种,各厂商以80C51为基核(内核)开发出的CHMOS工艺单片机产品统称为80C51系列。

当前常用的80C51系列单片机主要产品有:

1)Intel产品:80C31、80C51、87C51、80C32、80C52、87C52等;

2)Ateml产品:89C51、89C52、89C2051等;

3)Philips,华邦,Siemens等公司以80C51为基核的许多产品。

80C51按总线结构可分为总线型和非总线型。

如常见到的89C51单片机就是总线结构,89C51单片机内部有数据总线,地址总线和控制总线。

但单片机由于芯片引脚数量的限制,数据总线和地址总线经常采用复用方式,且许多引脚还要与并行I/O口引脚复用。

20引脚的89S2051单片机就是一种非总线型的。其外部引脚很少,可使成本大大降低。

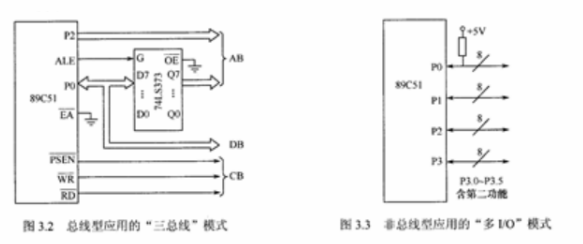

总线型单片机应用模式

1)如下左图为总线型单片机的总线应用模式,可以方便地将单片机配置成典型的三总线结构。

这种应用模式在扩展外围器件比较多的时候接线会比较复杂,系统的可靠性会降低。因此,在设计系统时,应尽量减少扩展器件的数量。

2)如下右图为总线型单片机的非总线应用模式,适用于大量I/O口需求的应用系统。

非总线型单片机应用模式

该模式已经将外部总线扩展用的I/O口线和控制功能线去掉,从而使单片机的引脚数减少,体积减少。对于不需进行并行外围扩展,装置体积要求苛刻且程序量不大的系统及其适用。

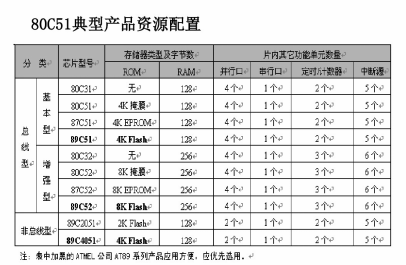

80C51典型成品的资源配置和引脚

由上表可见增强型与基本型有以下不同:

1)片内ROM字节数从4KB增加到8KB;

2)片内RAM字节数从128B增加到256B;

3)定时/计数器从2个增加到3个;

4)中断源由5个增加到6个。

下图为80C51系列单片机引脚图和逻辑符号,为标准的40脚DIP封装。

这些引脚的功能描述如下:

1)电源引脚Vcc和VssVcc

是电源端,接+5V;Vss接地端。通常在Vcc和Vss引脚之间接0.1uF高频滤波电容。

2)时钟电路引脚XTAL1和XTAL2

XTAL1:接外部晶振和微调电容的一端,在片内它是振荡器倒相放大器的输入,若使用外部TTL时钟,则该引脚必须接地。

XTAL2:接外部晶振和微调电容的一端,在片内它是振荡器倒相放大器的输出,若使用外部TTL时钟,则该引脚为外部时钟的输入。

3)地址锁存允许ALE

在系统扩展时,ALE用于控制地址锁存器锁存P0口输出的低8位地址,从而实现数据与低位地址的复用。

当单片机上电正常工作以后,ALE端通常以时钟频率的1/6的固定频率向外输出正脉冲信号,ALE的负载能力为8个LS TTL器件。

ale(address lock enable)作用是在访问外部存储器时,p0口做为地址/数据复用口,ale信号用于锁存低8位地址。当ale信号为高电平时,p0口上的信息为低8位地址,在ale信号的下降沿时将p0口上的低8位地址送到地址锁存器锁存起来。 在ale为低电平期间p0口上的信息为指令或数据信息。在ale为低电平期间p0口上的信息为指令或数据信息,以实现低位地址与数据的分离。ale是自动运行的。

4)外部程序存储器读选通信号 ~PSEN

是读外部程序存储器的选通信号,低电平有效。CPU从外部存储器取指令时,它在每个机器周期中两次有效。因此,在一个机器周期内,CPU可以从程序存储器中读取两个字节的指令码。

5)程序存储器地址允许输入端 ~EA

当该引脚为高电平时,CPU执行片内程序存储器指令,但当PC中的值超过0FFFH时,将自动转向执行片外程序存储器指令。

当该引脚为低电平时,CPU只执行片外程序存储器指令。对于8031,由于其无片内ROM,故该引脚必须接低电平。

6)复位信号RST

该信号高电平有效,在输入端保持两个机器周期的高电平后,就可以完成复位操作。

此外,该引脚还有掉电保护功能,若在该引脚接+5V备用电源,在使用中若Vcc掉电,可保护片内RAM中信息不丢失。

7)输入/输出口引脚P0、P1、P2和P3

P0口(P0.0~P0.7):该端口为漏极开路的8位准双向口,内部没有上拉电阻,该口在做I/O口使用时务必要外接上拉电阻,驱动能力为8个LS TTL负载,它是低8位地址线和8位数据线的复用端口。

P1口(P1.0~P1.7):它是一个内部带上拉电阻的8位准双向I/O口,P1的驱动能力为4个LS TTL负载。

P2口(P2.0~P2.7):它是一个内部带上拉电阻的8位准双向I/O口,P1的驱动能力为4个LS TTL负载。在访问外部程序存储器时,它作为存储器的高8位地址线。

P3口(P3.0~P3.7):它是一个内部带上拉电阻的8位准双向I/O口,P3口除了作为一般的I/O口外,还具有特殊功能。

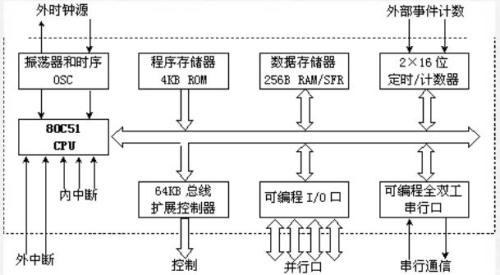

80C51单片机的逻辑结构

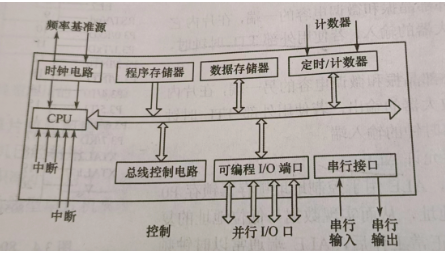

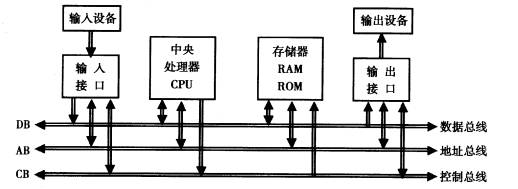

80C51单片机采用的是冯·诺依曼提出的经典计算机体系结构框架,即一台计算机由运算器,控制器,存储器,输入设备和输出设备5个基本部分组成。

80C51单片机在一块芯片上集成了CPU,RAM,ROM,定时/计数器和多功能I/O口等。80C51单片机的系统结构框图如下所示。

由上图可以看出,单片机内部主要包含下列几个部件:

1)一个8位CPU

2)一个时钟电路

3)4KB程序存储器

4)128B数据存储器

5)两个16位定时/计数器

6)4个8位并行I/O端口

8)5个中断源,其中包括两个优先级嵌套中断

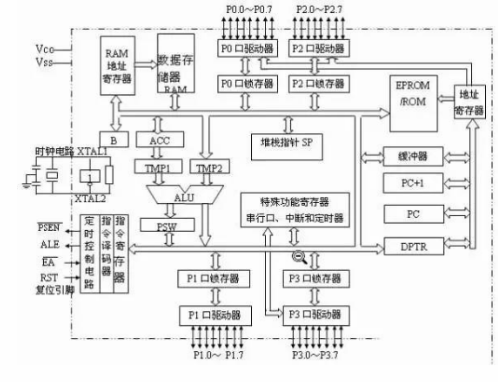

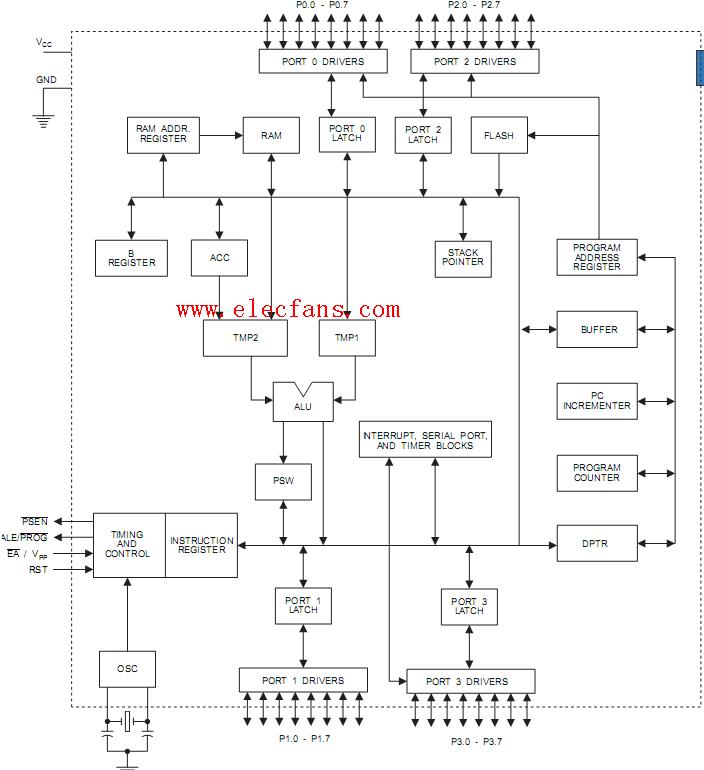

80C51单片机的内部结构

80C51单片机的内部结构框图如下所示。

1.CPU

CPU即中央处理器的简称,是单片机的核心部件,它完成各种运算和控制操作,CPU由运算器和控制器两部分电路组成。

1)运算器电路

运算器电路包括ALU算术逻辑单元,ACC累加器,B寄存器,状态寄存器,暂存器1和暂存器2等部件。

运算器的功能是进行算术运算,逻辑运算,位变量处理和数据传送。

运算电路以ALU为核心单元,可以完成半字节、单字节及多字节数据的运算操作,其中包括加减乘除,十进制调整等算术运算以及与,或,异或,求补和循环等逻辑操作,同时还具有一般微处理器所不具备的位处理功能,运算结果的状态由状态寄存器保存。

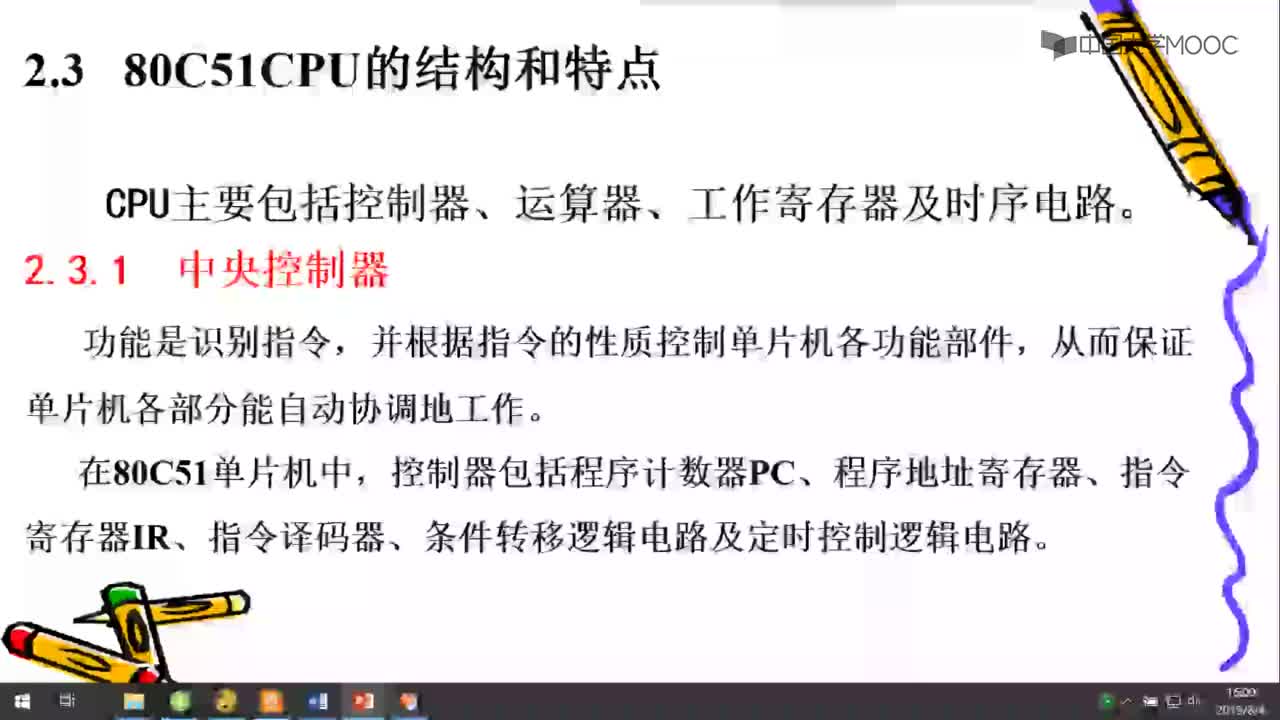

2)控制器电路

控制器电路包括程序计数器PC,PC加1寄存器,指令寄存器,指令译码器,数据指针DPTR,堆栈指针SP,缓冲器以及定时与控制电路等。控制电路完成指挥控制工作,协调单片机各部分正常工作。

程序计数器PC用来存放即将要执行的指令地址。数据指针DPTR为16位数据指针,它可以对外部数据存储器和I/O口进行寻址,它的低8位为DPL(地址为82H),高8位为DPH(地址为83H),堆栈指针SP随时跟踪栈顶地址,按先进后出的原则存取数据。

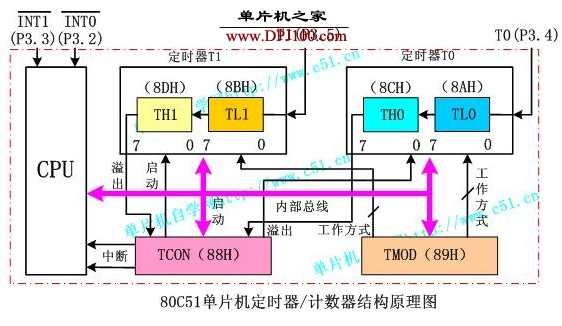

2.定时/计数器

80C51单片机片内有两个16位的定时/计数器,可以用于定时控制,延时以及对外部事件的计数和检测等。

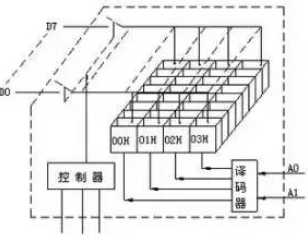

3.存储器

80C51系列单片机的存储器包括数据存储器和程序存储器,程序存储器和数据存储器的地址空间是相互独立的,物理结构也不相同。

4.并行I/O口

80C51单片机共有4个8位的I/O口,每条I/O线都能独立地用作输入或输出。

5.串行I/O口

80C51单片机有一个采用通用异步工作方式的全双工串行通信接口。

6.中断控制系统

80C51共有5个中断源,分为高级和低级两个中断优先级。

7.时钟电路

80C51芯片内部有时钟电路,但晶体振荡器和微调电容必须外接。时钟电路为单片机产生时钟脉冲序列。

8.总线

以上所有组成部分都是通过总线连接起来的,系统的地址信号,数据信号和控制信号都是通过总线传送的,总线结构减少了单片机的连线和引脚,提高了集成度和可靠性。

电子发烧友App

电子发烧友App

评论