DVP简介

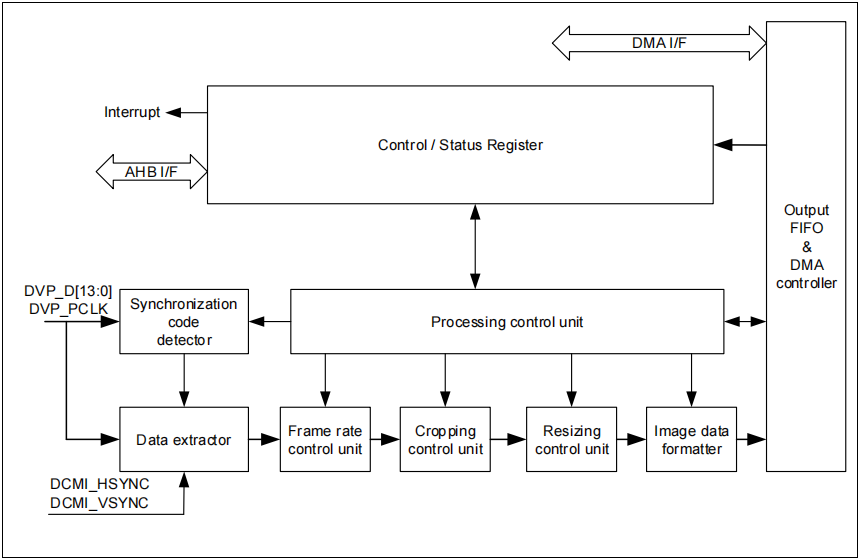

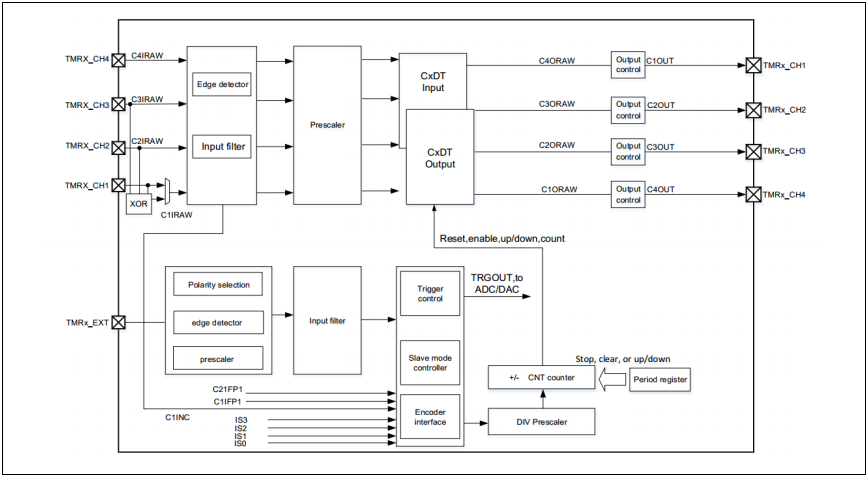

数字摄像头并行接口(DVP)用于捕获CMOS影像摄像机所输出的并行数据。依据摄像机输出,可选择以硬件同步模式或内嵌码同步模式进行帧同步与行同步。依使用需求,可透过帧率控制,调节每秒捕获的帧数。剪裁窗口功能可以保留兴趣区域数据,舍弃其他部分。使用图像尺寸调整功能,可依据比例对图像进行像素数或行数缩减。直接存储器访问的使用,可在不耗用CPU资源的状态下,将捕获数据传输至储存单元。使用者仅须透过状态中断与错误中断,监控数据接收状态即可。DVP系统框图

图1. DVP系统框图

周边配置

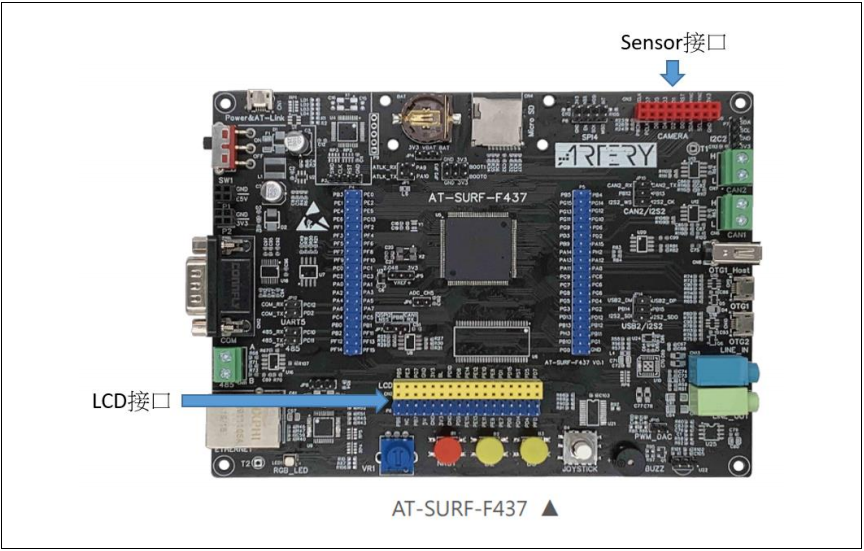

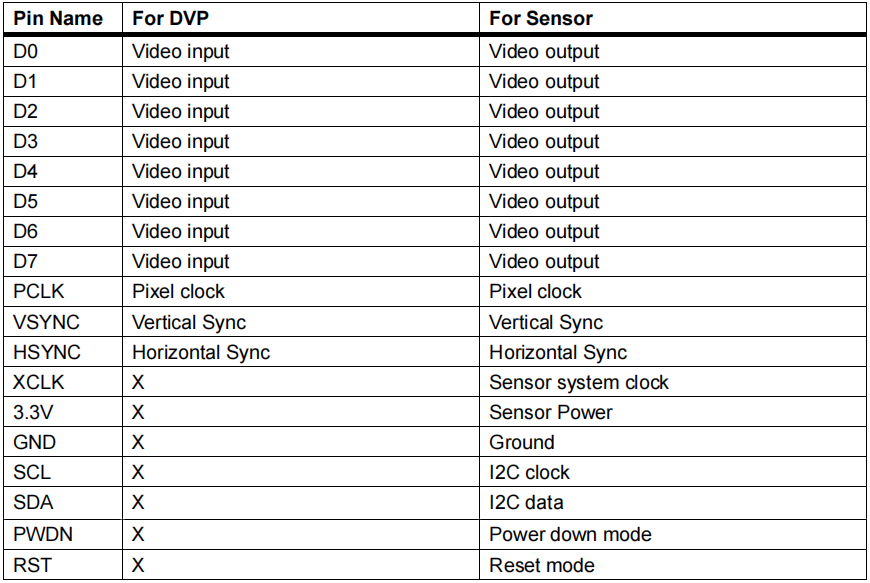

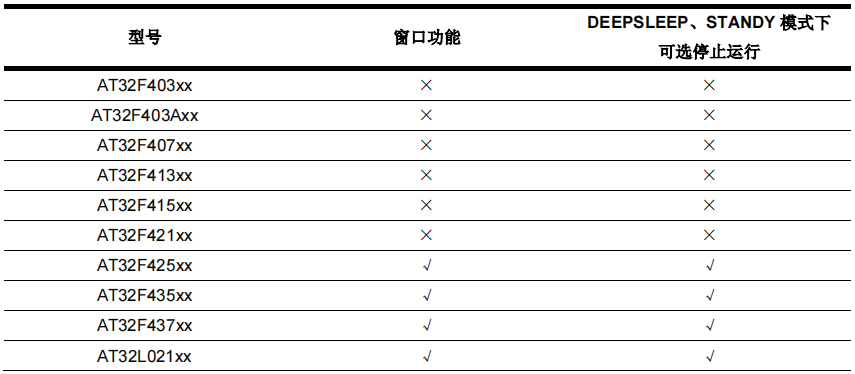

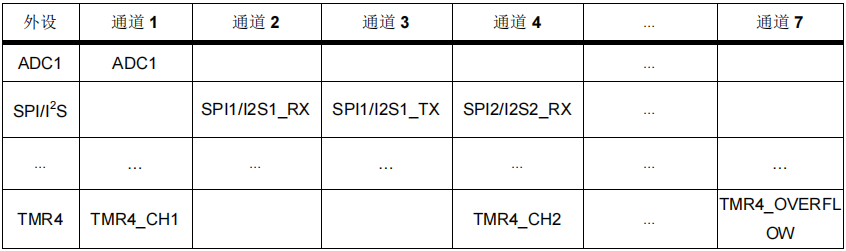

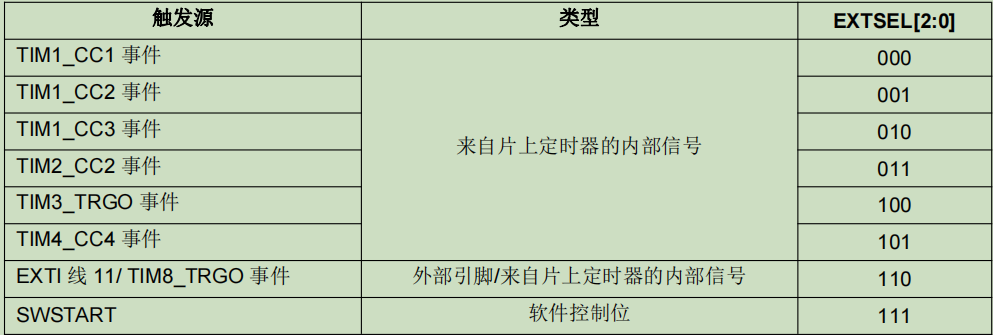

SURF板图2. AT-SURF-F437 DVP & Sensor pin表1. DVP接口表

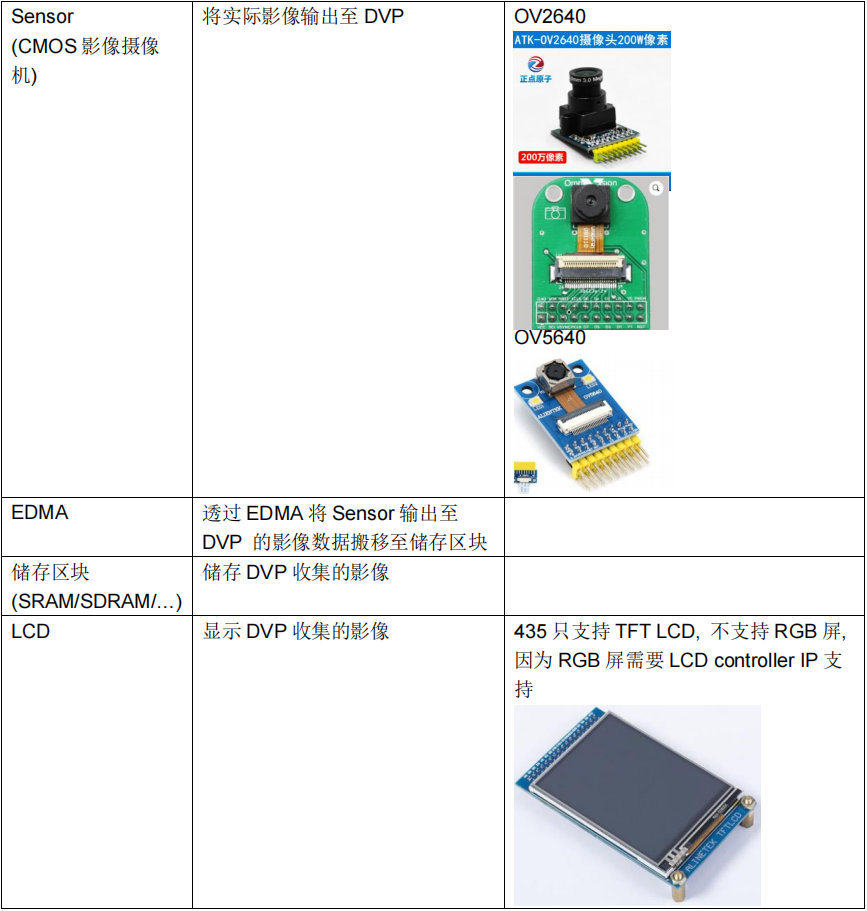

DVP & Sensor pin表1. DVP接口表 DVP基本环境介绍表2. DVP环境介绍

DVP基本环境介绍表2. DVP环境介绍

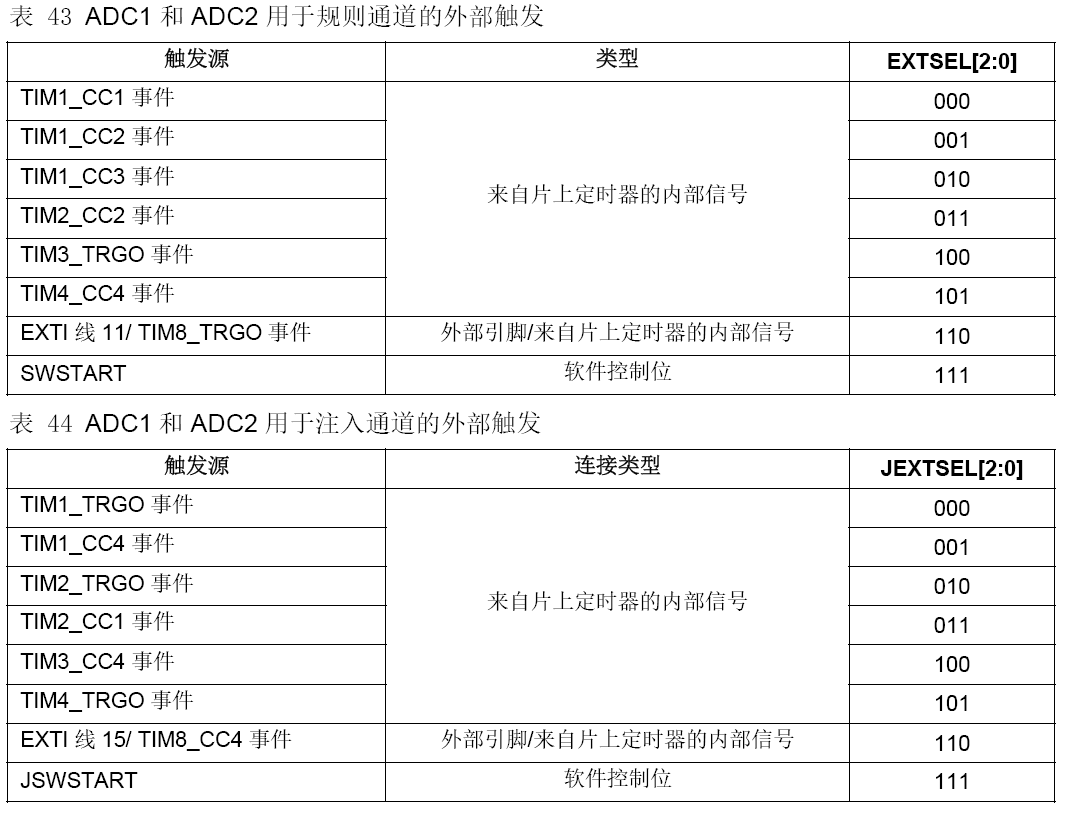

DVP功能

数据长度

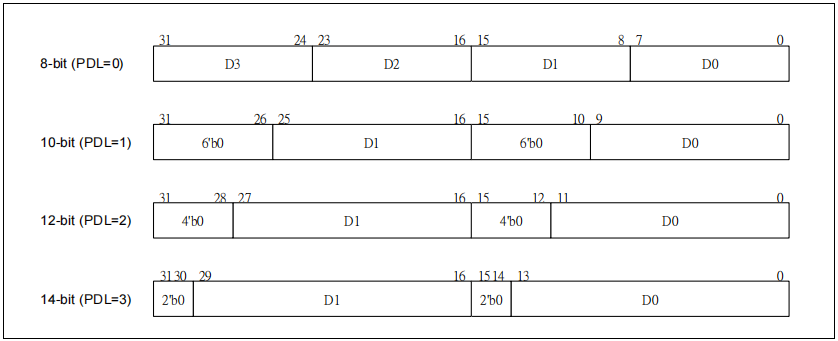

数字摄像头并行接口(DVP)将捕获的数据,包装成字(32位)数据,供直接存储器访问从寄存器DVP_DT取得。包装方式依DVP_CTRL寄存器PDL的配置而异。详见下图。8位并行数据(PDL=0)配置PDL为0,DVP在每个DVP像数时钟(DVP_PCLK)捕获一个8位数据,并以四个数据包装成一组字数据。最先捕获者放置于最低8位,最后捕获者放置于最高8位,依此类推。10位并行数据(PDL=1)配置PDL为1,DVP在每个DVP像数时钟(DVP_PCLK)捕获一个10位数据,并以二个数据包装成一组字数据。包装将字数据分成两组半字进行。先捕获者放置于低位半字的最低10位,最捕获者放置于高位半字的最低10位,余者清零。12位并行数据(PDL=2)配置PDL为2,DVP在每个DVP像数时钟(DVP_PCLK)捕获一个12位数据,并以二个数据包装成一组字数据。包装将字数据分成两组半字进行。先捕获者放置于低位半字的最低12位,最捕获者放置于高位半字的最低12位,余者清零。14位并行数据(PDL=3)配置PDL为3,DVP在每个DVP像数时钟(DVP_PCLK)捕获一个14位数据,并以二个数据包装成一组字数据。包装将字数据分成两组半字进行。先捕获者放置于低位半字的最低14位,最捕获者放置于高位半字的最低14位,余者清零。图3. PDL配置与输出包装之关系

同步模式

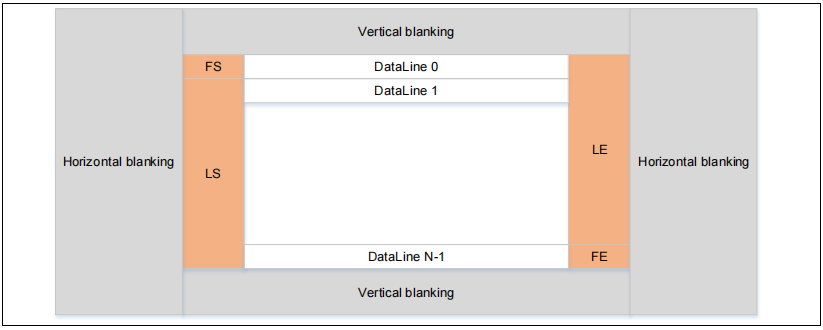

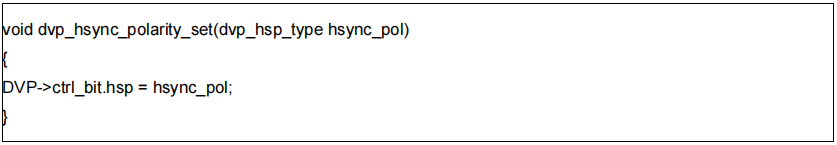

数字摄像头并行接口(DVP)以DVP像素时钟(DVP_PCLK)来捕获CMOS影像摄像机所输出的像素并行数据(DVP_D),DVP_PCLK是由CMOS影像摄像机提供。透过配置DVP_CTRL的寄存器CKP,DVP可选择使用DVP_PCLK的上升缘或下降缘进行捕获。捕获的数据可以区分为有效像素数据与消隐区间数据,用户仅只关心有效像素数据的部分。CMOS影像摄像机可提供一种或数种模式的同步信息,供接收端进行帧分割,并提取有效像素数据。数字摄像头并行接口(DVP)支持两种同步模式,硬件同步模式与内嵌码同步模式,可透过配置DVP_CTRL的寄存器SM来选择。 硬件同步模式相关寄存器:-SM(Synchronization mode)=0-DVP_CTRL HSP-DVP_CTRL VSPCMOS影像摄像机可提供水平同步讯号与垂直同步信号,供接收端进行同步。配置DVP_CTRL的寄存器SM为0,DVP可以此同步模式进行接收。水平同步讯号用于区分有效像素与消隐区间,DVP由DVP水平同步讯号引脚(DVP_HSYNC)导入此讯号,依据此讯号进行行分割,并提取有效像素数据。需配置DVP_CTRL的寄存器HSP来调整该讯号极性,使其与数字摄像头之输出一致。垂直同步信号用于帧之间的分隔,DVP由DVP垂直同步信号引脚(DVP_VSYNC)导入此讯号,依此讯号进行帧分割。 内嵌码同步模式相关寄存器:-SM(Synchronization mode)=1-DVP_SCR-DVP_SUR为了节省引脚使用,部分厂商的CMOS影像摄像机,可在有效像素数据与消隐区间数据之间嵌入同步码作为同步信息,取代水平同步讯号与垂直同步信号之使用。配置DVP_CTRL的寄存器SM为1,DVP可以此同步模式进行接收。同步码由四笔数据构成,前三笔数据内容固定,第一笔为全1数据,之后接续两笔全0数据。第四笔数据则依同步信息而异,需依摄像机厂商所使用的同步码型式与内容,配置DVP_SCR寄存器。1. FS/FE/LS/LE型式欲接收FS/FE/LS/LE型式,需配置DVP_SCR寄存器如下。FMSC:配置成影像摄像机使用的FS第四笔数据最高八比特位。LNSC:配置成影像摄像机使用的LS第四笔数据最高八比特位。LNEC:配置成影像摄像机使用的LE第四笔数据最高八比特位。FMEC:配置成影像摄像机使用的FE第四笔数据最高八比特位。图4. FS/FE/LS/LE型式下的帧组成 2. SAV/EAV型式欲接收SAV/EAV型式,需配置DVP_SCR寄存器如下:FMSC:配置成0xff。(配置为无帧开始同步码之内嵌码同步模式)LNSC:配置成影像摄像机使用的Active SAV第四笔数据最高八比特位。LNEC:配置成影像摄像机使用的Active EAV第四笔数据最高八比特位。FMEC:配置成0xff。(配置为任意帧结束同步码之内嵌码同步模式)图5. SAV/EAV型式下的帧组成

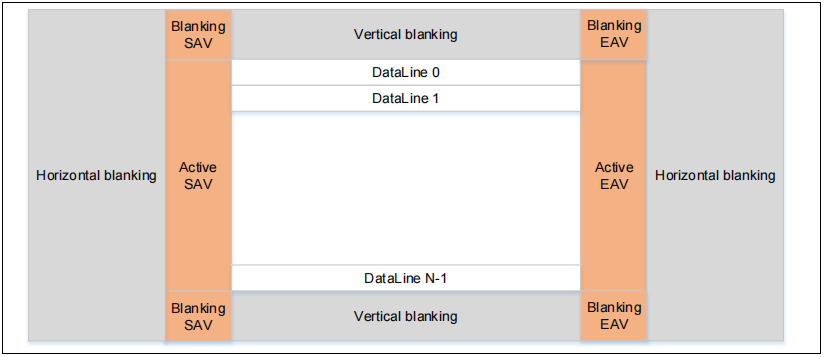

2. SAV/EAV型式欲接收SAV/EAV型式,需配置DVP_SCR寄存器如下:FMSC:配置成0xff。(配置为无帧开始同步码之内嵌码同步模式)LNSC:配置成影像摄像机使用的Active SAV第四笔数据最高八比特位。LNEC:配置成影像摄像机使用的Active EAV第四笔数据最高八比特位。FMEC:配置成0xff。(配置为任意帧结束同步码之内嵌码同步模式)图5. SAV/EAV型式下的帧组成

捕获模式

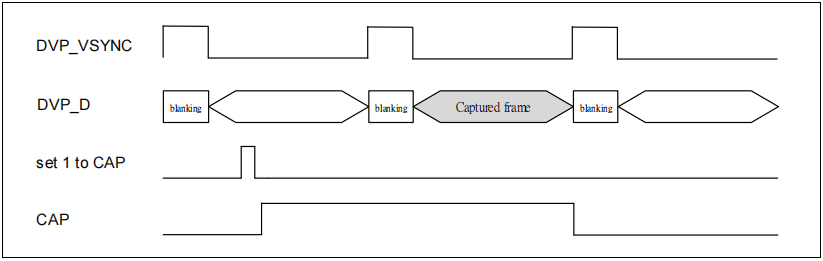

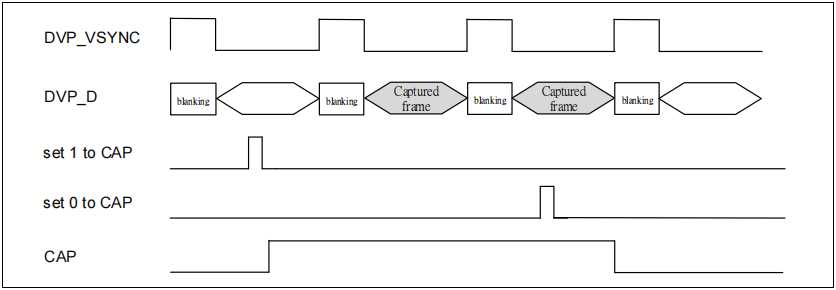

单帧捕获模式相关寄存器:-DVP_CTRL CFM=1此模式下,用户置起DVP_CTRL的寄存器CAP后,DVP会根据接收到的同步信息,于次帧开始后,进行数据捕获。于该帧结束之时,DVP会自动重置寄存器CAP,并停止数据捕获。图6. 单帧捕获模式示意图 连续捕获模式相关寄存器:-DVP_CTRL CFM=0此模式下,用户置起DVP_CTRL的寄存器CAP后,DVP会根据接收到的同步信息,于次帧开始后进行数据捕获,此捕获行为会持续进行。当使用者对寄存器CAP置0时,DVP会维持CAP的置起状态并持续捕获数据,直到同步信息反应当帧结束。此时DVP会重置寄存器 CAP,并停止数据捕获。图7. 连续捕获模式示意图

连续捕获模式相关寄存器:-DVP_CTRL CFM=0此模式下,用户置起DVP_CTRL的寄存器CAP后,DVP会根据接收到的同步信息,于次帧开始后进行数据捕获,此捕获行为会持续进行。当使用者对寄存器CAP置0时,DVP会维持CAP的置起状态并持续捕获数据,直到同步信息反应当帧结束。此时DVP会重置寄存器 CAP,并停止数据捕获。图7. 连续捕获模式示意图

帧率控制功能

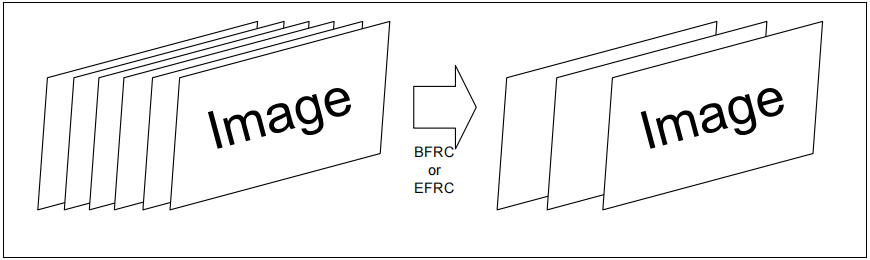

相关寄存器:DVP_CTRL CFM=0数字摄像头并行接口(DVP)可透过帧率控制,调节每秒捕获的帧数。帧率控制仅当DVP配置于连续捕获模式(CFM=0)下,方可作用。帧率控制单元可区分成基本型帧率控制与进阶型帧率控制两种。图8. 帧率控制功能示意图 基本型帧率控制相关寄存器:图9. DVP_CTRL BFRC

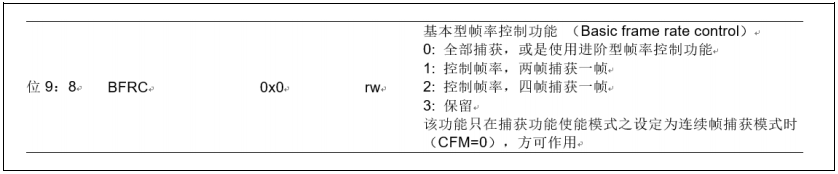

基本型帧率控制相关寄存器:图9. DVP_CTRL BFRC 配置DVP_CTRL的寄存器BFRC,可选择让DVP每两帧捕获一帧,或是每四帧捕获一帧。

进阶型帧率控制相关寄存器:图10. DVP_ACTRL EFRCE

配置DVP_CTRL的寄存器BFRC,可选择让DVP每两帧捕获一帧,或是每四帧捕获一帧。

进阶型帧率控制相关寄存器:图10. DVP_ACTRL EFRCE 图11. DVP_FRF EFRCTF/EFRCSF

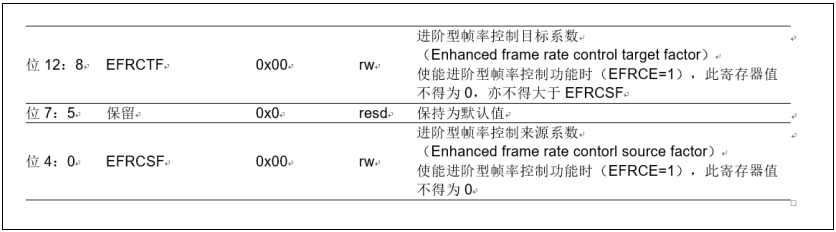

图11. DVP_FRF EFRCTF/EFRCSF 如需更精细的帧数调节,可使用进阶型帧率控制。使用时须禁止基本型帧率控制(BFRC=0),并置起DVP_ACTRL的寄存器EFRCE,DVP会依据DVP_FRF的寄存器EFRCSF与EFRCTF之配置来调整帧数,调整公式如下:目标帧率=(EFRCTF/EFRCSF)×原始帧率请注意,当使用进阶型帧率控制功能时,寄存器EFRCSF与EFRCTF值不得为0,且EFRCTF不得大于EFRCSF。

如需更精细的帧数调节,可使用进阶型帧率控制。使用时须禁止基本型帧率控制(BFRC=0),并置起DVP_ACTRL的寄存器EFRCE,DVP会依据DVP_FRF的寄存器EFRCSF与EFRCTF之配置来调整帧数,调整公式如下:目标帧率=(EFRCTF/EFRCSF)×原始帧率请注意,当使用进阶型帧率控制功能时,寄存器EFRCSF与EFRCTF值不得为0,且EFRCTF不得大于EFRCSF。

剪裁窗口功能

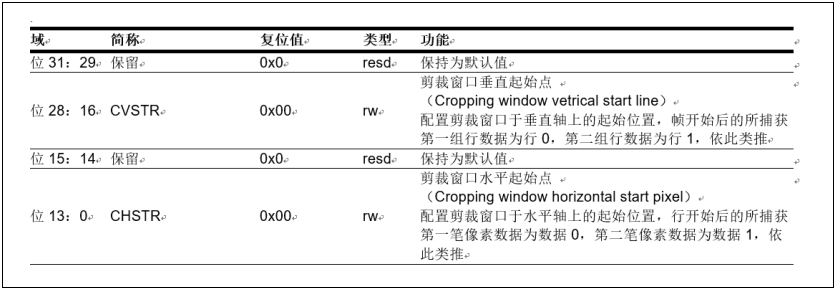

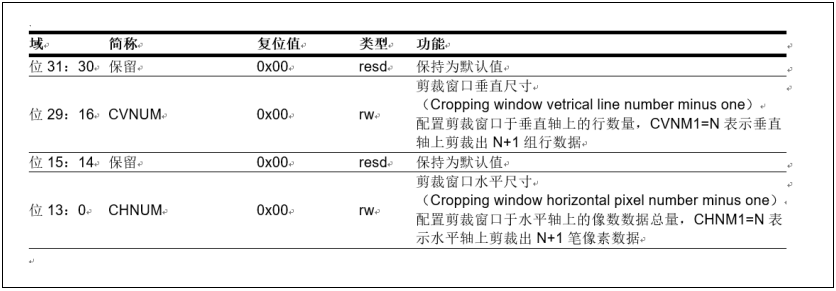

相关寄存器:图12. DVP_CWST CVSTR/CHSTR

图13. DVP_CWSZ CVNUM/CHNUM

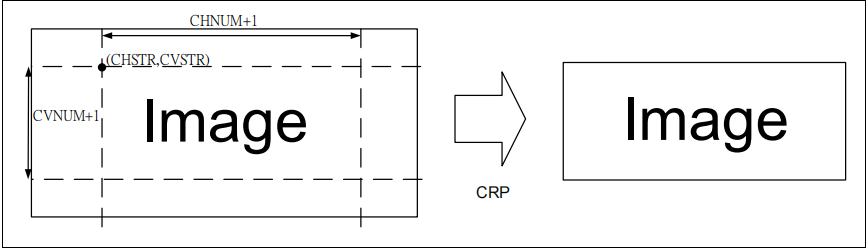

剪裁窗口功能可以供用户保留兴趣区域数据,舍弃其他部分。置起DVP_CTRL的寄存器CRP,DVP会依据DVP_CWST与DVP_CWSZ之寄存器配置进行剪裁,如下图所示意。

图14. 剪裁窗口功能示意图

请注意,由于DVP会将捕获的数据,包装成字(32位)数据,供直接存储器访问提取。故使用剪裁窗口功能时,CHNUM有下述限制:8位并行数据(PDL=0)时,CHNUM+1须为4的倍数。10或12或14位并行数据(PDLǂ0),CHNUM+1须为2的倍数。

图像尺寸调整功能

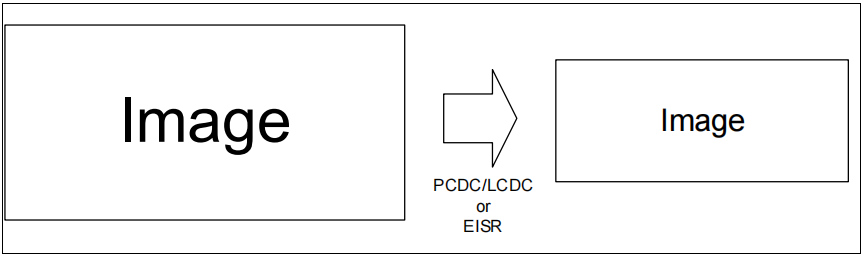

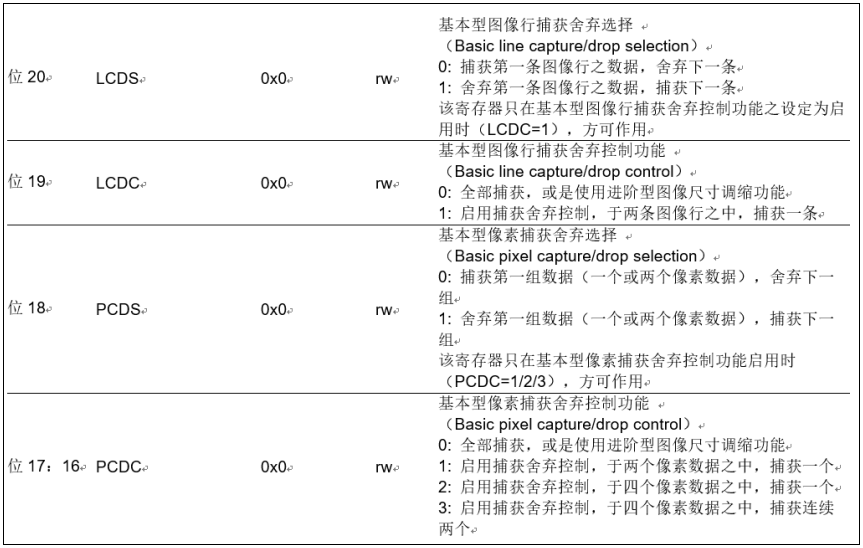

使用图像尺寸调整功能,可依据比例对图像进行像素数或行数缩减。图像尺寸调整功能单元可区分成基本型图像捕获舍弃控制与进阶型图像尺寸调缩功能两种。图15. 图像尺寸调整功能示意图 基本型图像捕获舍弃控制相关寄存器:图16. DVP_CTRL

基本型图像捕获舍弃控制相关寄存器:图16. DVP_CTRL

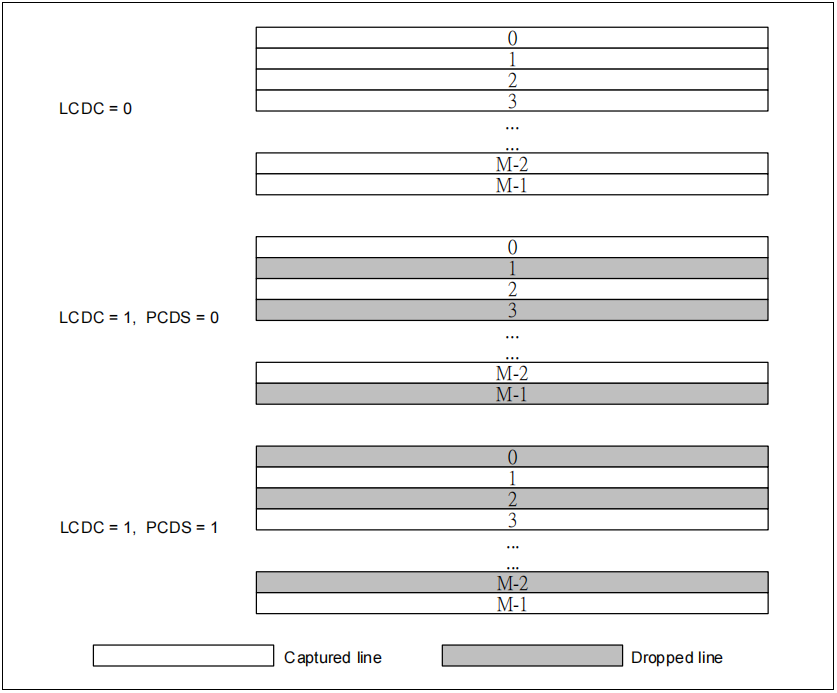

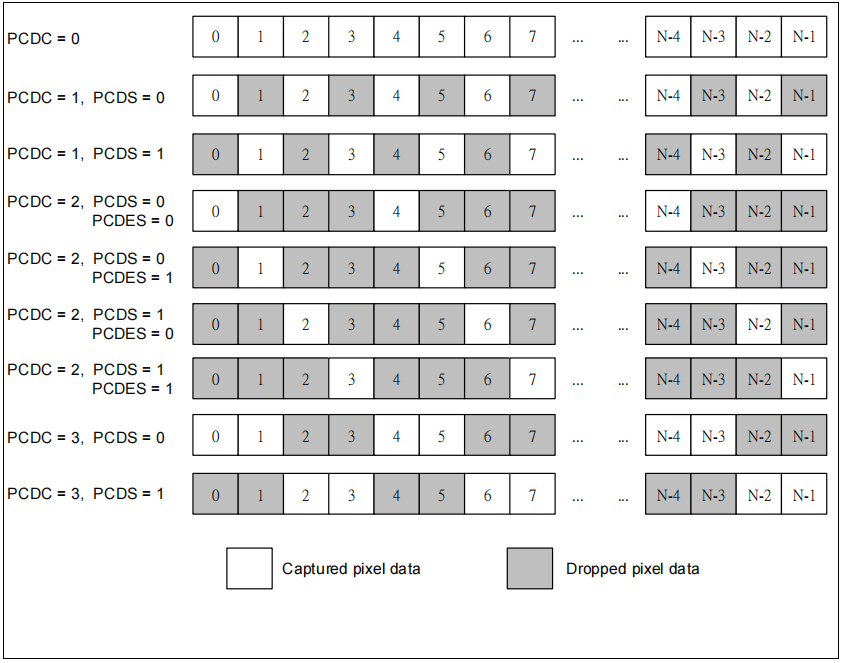

配置DVP_CTRL的寄存器PCDC或LCDC,可启用基本型图像捕获舍弃控制功能。将LCDC置1后,可在每两条捕获的图像行中舍弃一条,将图像的垂直轴尺寸减半。配置LCDS可以选择捕获前一条并舍弃下一条,或是反向为之。寄存器PCDC可以调整图像的水平轴尺寸,由PCDS与PCDES决定捕获何者。如下图所示。

图17. LCDC/LCDS与帧组成

图18. PCDC/PCDS与行组成

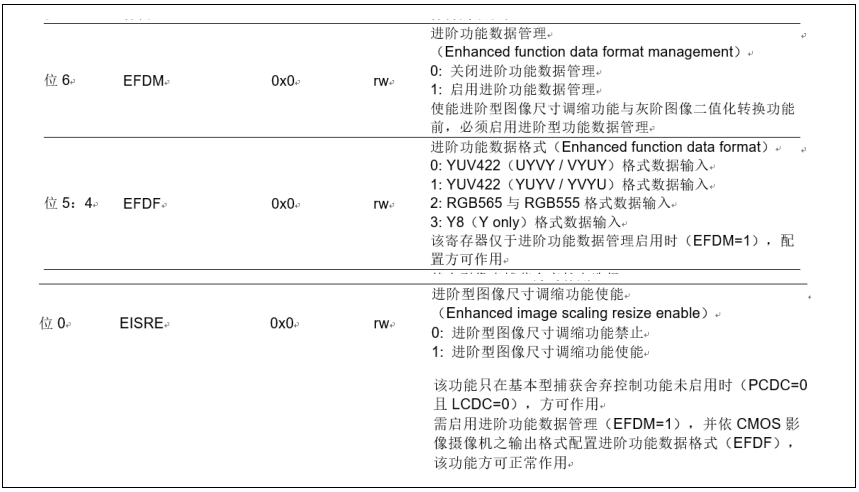

进阶型图像尺寸调缩功能相关寄存器:图19. DVP_ACTRL

进阶型图像尺寸调缩功能相关寄存器:图19. DVP_ACTRL

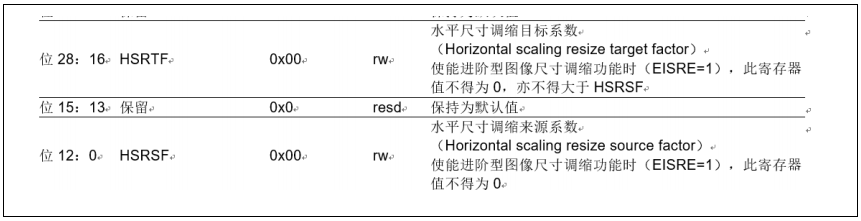

图20. DVP_HSCF

图21. DVP_VSCF

如需更精细的图像调缩,可使用进阶型进阶型图像调缩功能。使用此功能需启用进阶功能数据管理(EFDM=1),并依CMOS影像摄像机之输出格式配置进阶功能数据格式(EFDF)。使用进阶型进阶型图像调缩功能时,须禁止图像捕获舍弃控制功能(PCDC=0且LCDC=0),并置起DVP_ACTRL的寄存器EISRE,DVP会依据DVP_HSCF的寄存器HSRSF与HSRTF之配置来调缩图像的水平轴尺寸,并依据DVP_VSCF的寄存器VSRSF与VSRTF之配置来调缩图像的垂直轴尺寸,调整公式如下:

目标水平轴尺寸=(HSRTF/HSRSF)×原始水平轴尺寸目标垂直轴尺寸=(VSRTF/VSRSF)×原始垂直轴尺寸请注意,当使用进阶型进阶型图像调缩功能时,寄存器HSRSF、HSRTF、VSRSF、VSRTF值不得为0,且HSRTF不得大于HSRSF,并VSRTF不得大于VSRSF。此外,计算所得的目标水平轴尺寸与目标垂直轴尺寸必须为整数,且目标水平轴尺寸需为4的倍数,否则此单元可能会产生不预期之结果。

灰阶图像二值化转换

相关寄存器:图22. DVP_ACTRL MIBE

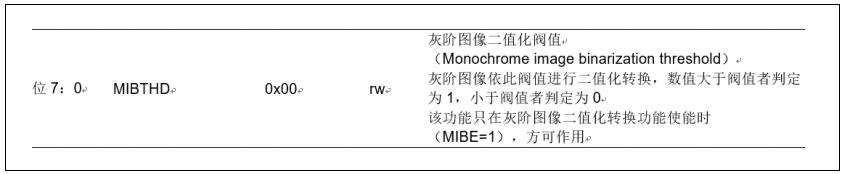

图23. DVP_BTH

灰阶图像二值化转换单元提供将图像亮度转换成一比特位表示之格式。使用此功能需启用进阶功能数据管理(EFDM=1),并依CMOS影像摄像机之输出格式配置进阶功能数据格式(EFDF),设定方式请参考錯誤!找不到參照來源。置起DVP_ACTRL的寄存器MIBE可使能灰阶图像二值化转换功能。

灰阶图像依DVP_BTH之寄存器MIBTHD配置进行二值化转换,数值大于阀值者判定为1,小于阀值者判定为0。图像数据若为无法直接取出图像亮度的格式,则无法使用该功能。

中断与中断控制

相关寄存器:图24. DVP_STS

图25. DVP_ESTS

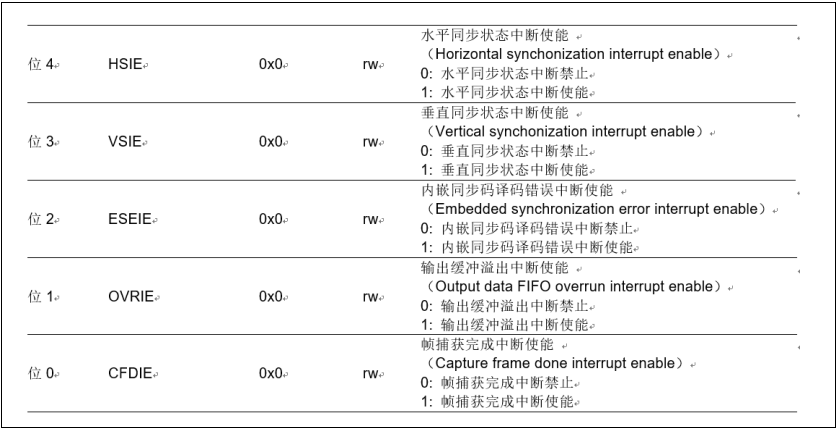

图26. DVP_IENA

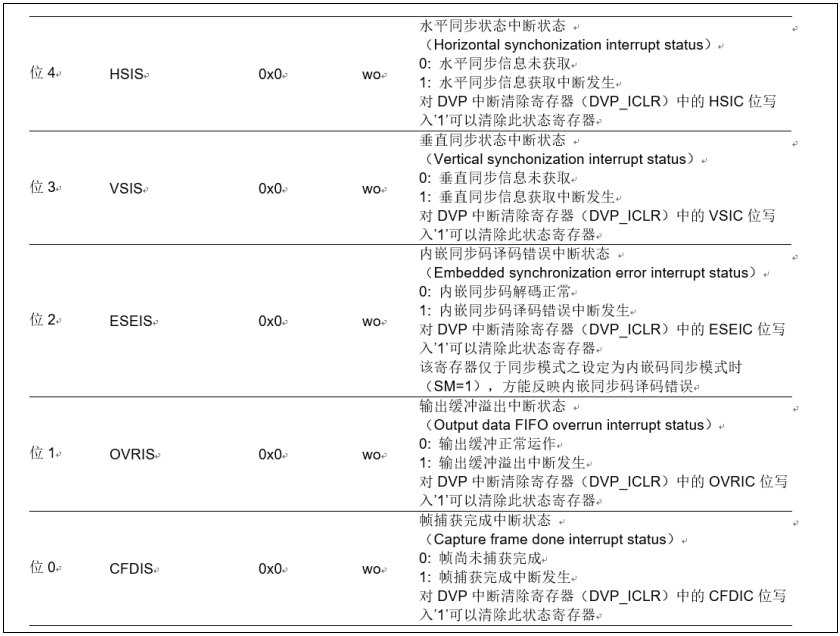

图27. DVP_ISTS

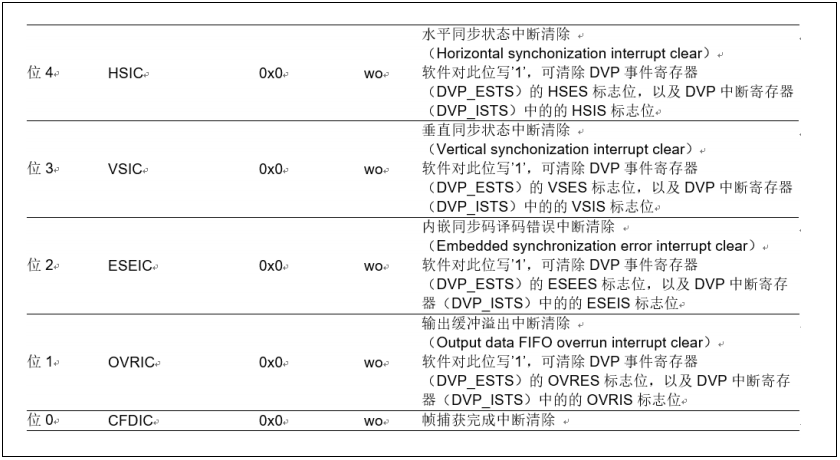

图28. DVP_ICLR

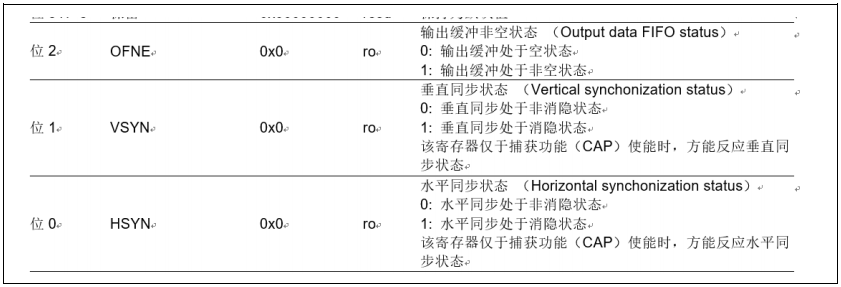

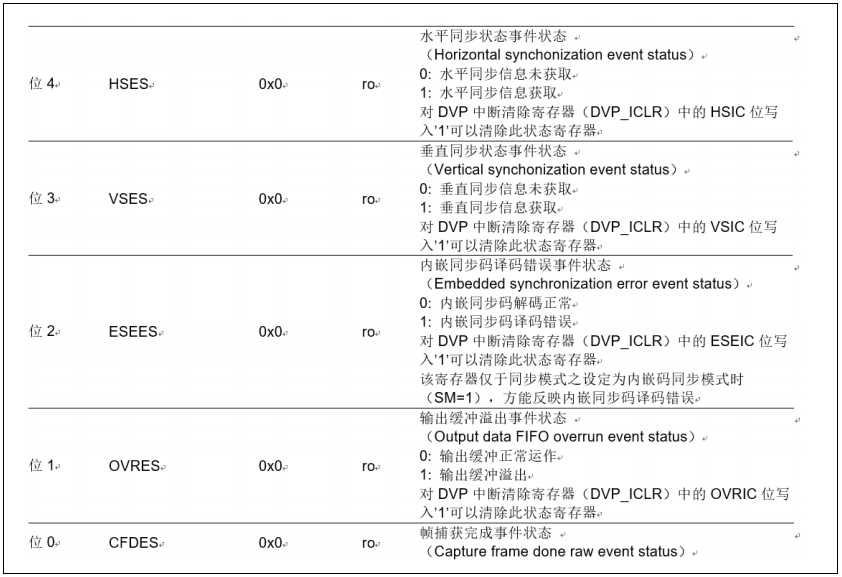

数字摄像头并行接口(DVP)的中断控制,由四组寄存器所构成。DVP_ESTS是只读寄存器,用于纪录捕获过程中所发生的同步状态或错误事件。DVP_IENA用于控制中断讯号之使能,配置该寄存器可以使能对应位的同步状态或错误中断,并以送至CPU。使能后所产生的中断会被记录在只读寄存器DVP_ISTS中,由于DVP是以全局中断连接CPU的NVIC,使用者需于此寄存器确认中断信息。纪录于DVP_ESTS与DVP_ISTS的状态,透过对DVP_ICLR的对应位上置1可清除之。

DVP_ICLR是唯写寄存器,无须置0解除。

DVP支持三组同步状态中断,描述如下:帧捕获完成(Capture frame done)CFDES与CFDIS于捕获功能(CAP)使能时,表现当前帧捕获已完成。根据同步讯号,帧捕获完成讯息会于获取帧结束讯号时发生。若剪裁窗口功能(CRP)始能时,帧捕获完成讯息会提前至剪裁窗口完成时产生。若捕获功能(CAP)未使能,CFDES与CFDIS不作用。 垂直同步状态(Vertical synchronization)VSES与VSIS用于表现垂直同步信息已获取。垂直同步信息可被定义为帧开始或帧结束,配置DVP_ACTRL的寄存器VSEID可以调整其定义。 水平同步状态(Horizontal synchronization)HSES与HSIS用于表现水平同步信息已获取。水平同步信息可被定义为行开始或行结束,配置DVP_ACTRL的寄存器HSEID可以调整其定义。 DVP支持两组错误中断,描述如下:输出缓冲溢出(Output data FIFO overrun)OVRES与OVRIS于捕获功能(CAP)使能时,表现输出缓冲溢出的错误状态。若直接存储器访问无法及时将捕获数据传输至储存单元,而导致输出缓冲全部蓄满数据,此时DVP所捕获的数据将会被舍弃,并产生输出缓冲溢出错误讯息。若捕获功能(CAP)未使能,OVRES与OVRIS不作用。 内嵌同步码译码错误(Embedded synchronization error)ESEES与ESEIS于捕获功能(CAP)使能,且使用时内嵌码同步模式时时(SM=1),表现内嵌同步码译码错误的错误状态。若译码器解译出非预期之同步码,译码器会舍弃当前的同步状态,并重新对后续的数据进行解译。此时DVP将会停止数据捕获,并产生内嵌同步码译码错误讯息。若捕获功能(CAP)未使能,或是使用硬件同步模式时(SM=0),ESEES与ESEIS不作用。DVP应用

Sensor常见影像数据格式

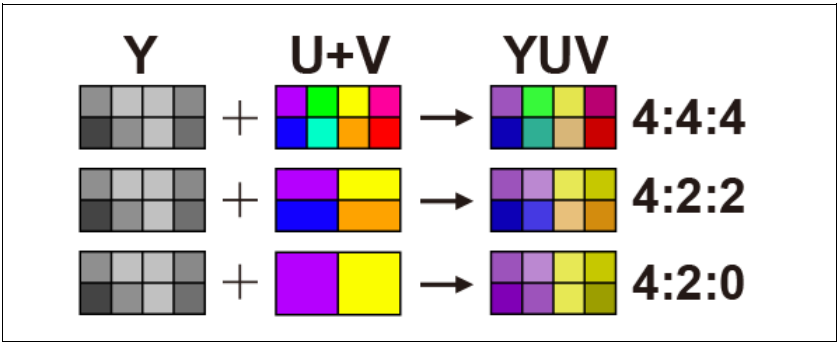

依厂商不同,CMOS影像摄像机可提供的图像输出格式极多,本章节仅针对常见格式进行简单描述。 RGB与YUV格式RGB:每一个像素由RGB三原色组成,“R”代表红色,“G”代表绿色,“B”代表蓝色。主要应用在计算机屏幕上,每一个像素色彩表现较丰富, 但无法将 RGB 三种值分开。常见格式有RGB565、RGB555…。YUV:每一个像素由YUV字段组成,“Y”表示明亮度(Luma),“UV”表示的是色度(Chroma)。主要应用在电视屏幕上,特点在于可以只储存Luma(黑白画面),或是压缩UV的储存空间,方便压缩影像数据。UV代表RGB三原色。常见格式有YUV444、YUV422、YUV420…。

图29. YUV Format

44、42与4:20是YUV的取样方法。YUV44即是无通道压缩的全像传送;YUV42即是把后面两个信道的讯号抽掉一半,所以只需要YUV44的三分之二带宽。

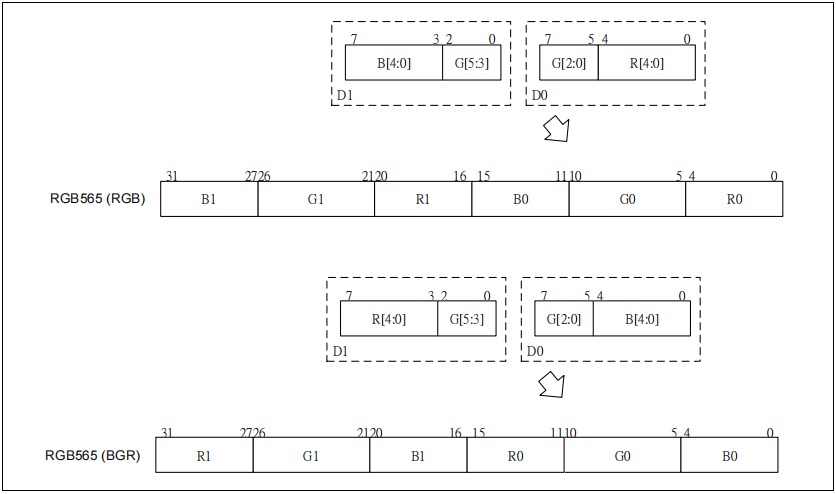

YUV与RGB有算法可以互相转换。 RGB565此格式下,CMOS影像摄像机每两个像素时钟输出一个半字(16位)数据的像素。每组半字数据包含三种像素分量,红色R、绿色G和蓝色B,分别以5位、6位和5位进行数据编码。第一个像素时钟输出R分量与G分量的低位部分,第二个像素时钟则输出G分量的高位部分与B分量。或是在第一个像素时钟输出B分量与G分量的低位部分,第二个像素时钟输出G分量的高位部分与R分量。錯誤!找不到參照來源。示意在RGB565格式下,DVP数据捕获与包装方式。图30. RGB565格式数据捕获与包装 RGB555此格式下,CMOS影像摄像机每两个像素时钟输出一个半字(16位)数据的像素。每组半字数据包含三种像素分量,红色R、绿色G和蓝色B,皆以5位进行数据编码。第一个像素时钟输出R分量与G分量的低位部分,第二个像素时钟输出G分量的高位部分与B分量。或是在第一个像素时钟输出B分量与G分量的低位部分,第二个像素时钟输出G分量的高位部分与R分量。因有效数据一共只有15位,故第二个像素时钟的最高位数据并不使用,CMOS影像摄像机会通常直接输出低电平。錯誤!找不到參照來源。示意RGB555格式下,DVP数据捕获与包装方式。图31. RGB555格式数据捕获与包装

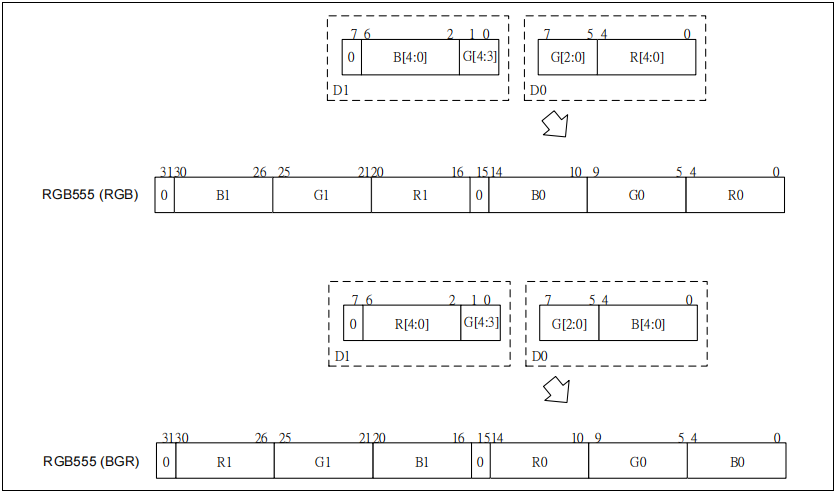

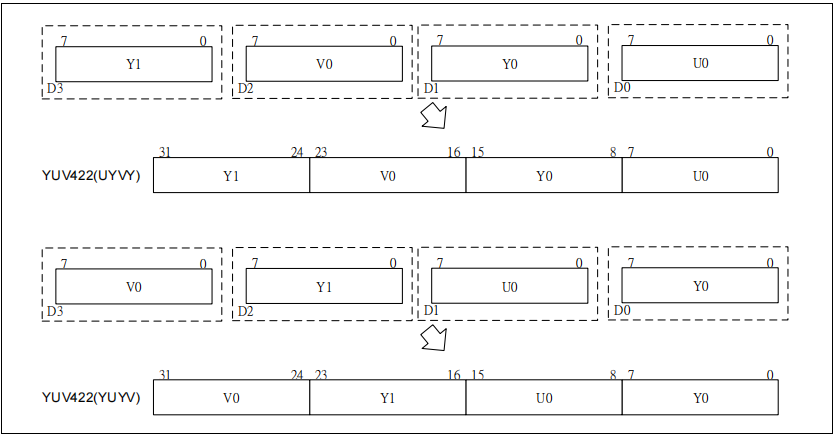

RGB555此格式下,CMOS影像摄像机每两个像素时钟输出一个半字(16位)数据的像素。每组半字数据包含三种像素分量,红色R、绿色G和蓝色B,皆以5位进行数据编码。第一个像素时钟输出R分量与G分量的低位部分,第二个像素时钟输出G分量的高位部分与B分量。或是在第一个像素时钟输出B分量与G分量的低位部分,第二个像素时钟输出G分量的高位部分与R分量。因有效数据一共只有15位,故第二个像素时钟的最高位数据并不使用,CMOS影像摄像机会通常直接输出低电平。錯誤!找不到參照來源。示意RGB555格式下,DVP数据捕获与包装方式。图31. RGB555格式数据捕获与包装 YUV422此格式下,CMOS影像摄像机每两个像素时钟输出一个半字(16位)数据的像素。每组半字数据包含一个亮度像素分量Y,与一个色度像素分量U或V,皆以8位进行数据编码。色度分量U与V会在各像素间交替,相邻两像素使用不同色度分量。摄像机于每个像素时钟输出一组像素分量,第一个像素时钟输出Y分量,第二个像素时钟则输出U分量或V分量。或是在第一个像素时钟输出U分量或V分量,第二个像素时钟输出Y分量。錯誤!找不到參照來源。示意在YUV422格式下,DVP数据捕获与包装方式,色度像素分量U与V顺序可互换。图32. YUV422格式数据捕获与包装

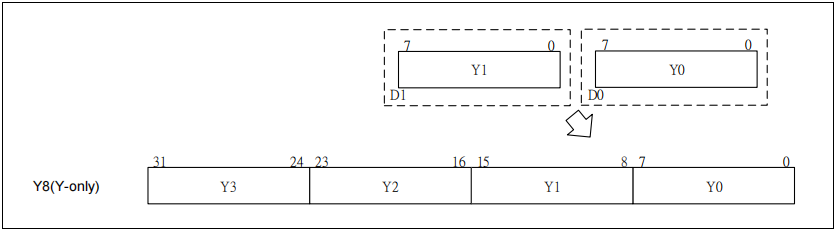

YUV422此格式下,CMOS影像摄像机每两个像素时钟输出一个半字(16位)数据的像素。每组半字数据包含一个亮度像素分量Y,与一个色度像素分量U或V,皆以8位进行数据编码。色度分量U与V会在各像素间交替,相邻两像素使用不同色度分量。摄像机于每个像素时钟输出一组像素分量,第一个像素时钟输出Y分量,第二个像素时钟则输出U分量或V分量。或是在第一个像素时钟输出U分量或V分量,第二个像素时钟输出Y分量。錯誤!找不到參照來源。示意在YUV422格式下,DVP数据捕获与包装方式,色度像素分量U与V顺序可互换。图32. YUV422格式数据捕获与包装 Y8Y8(Y-only)格式此格式下,CMOS影像摄像机每一个像素时钟输出一个字节(8位)数据的像素表示亮度Y,以8位进行数据编码。于此格式下,CMOS影像摄像机不输出色度信息。錯誤! 找不到參照來源。示意在Y8(Y-only)格式下,DVP数据捕获与包装方式。图33. Y8(Y-only)格式数据捕获与包装

Y8Y8(Y-only)格式此格式下,CMOS影像摄像机每一个像素时钟输出一个字节(8位)数据的像素表示亮度Y,以8位进行数据编码。于此格式下,CMOS影像摄像机不输出色度信息。錯誤! 找不到參照來源。示意在Y8(Y-only)格式下,DVP数据捕获与包装方式。图33. Y8(Y-only)格式数据捕获与包装

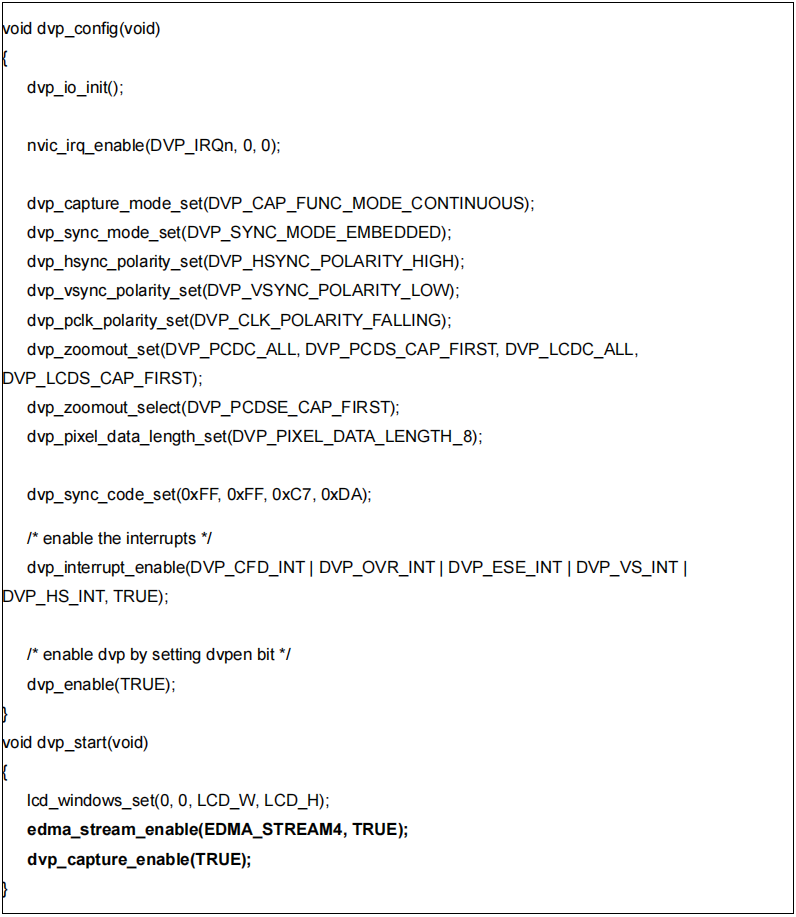

DVP Lib

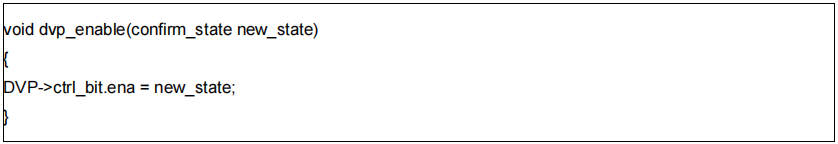

DVP功能开启/关闭DVP各功能在设定上没有先后顺序,只有dvp_capture_enable开启后马上会有影像输出,所以必须在完整设定(包含I2C/EDMA/…)后再启动- dvp_enable

开启后 DVP 各功能活化,但不会有影像输出

开启后 DVP 各功能活化,但不会有影像输出- dvp_capture_enable

开启后DVP就会马上会有影像输出, 所以必须在完整设定(包含I2C/EDMA/…)后再启动

同步模式-硬件同步

开启后DVP就会马上会有影像输出, 所以必须在完整设定(包含I2C/EDMA/…)后再启动

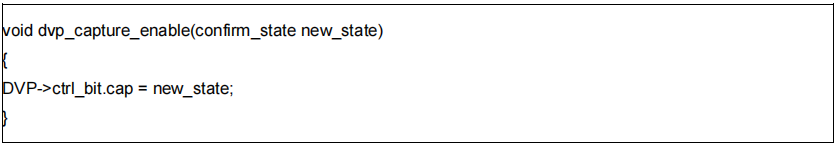

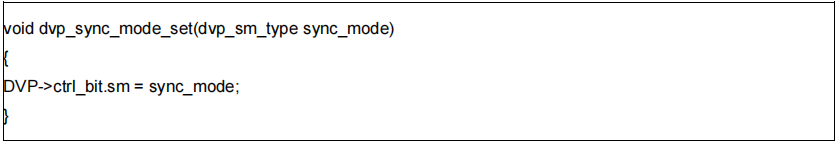

同步模式-硬件同步- dvp_sync_mode_set(DVP_SYNC_MODE_HARDWARE)

- dvp_hsync_polarity_set

视sensor而定,不同的sensor设定值可能不同

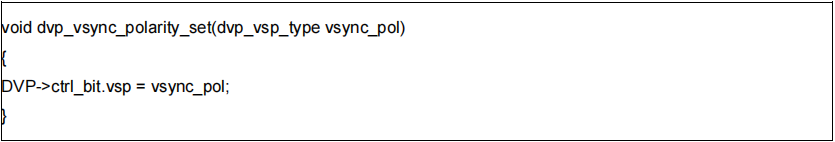

视sensor而定,不同的sensor设定值可能不同- dvp_vsync_polarity_set

视sensor而定,不同的sensor设定值可能不同

同步模式-内嵌码同步

视sensor而定,不同的sensor设定值可能不同

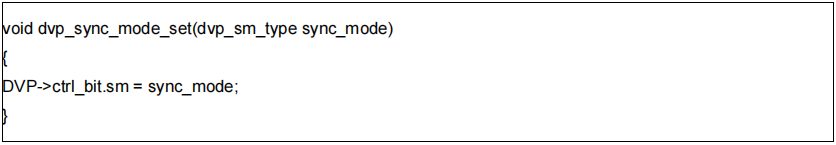

同步模式-内嵌码同步- dvp_sync_mode_set(DVP_SYNC_MODE_EMBEDDED)

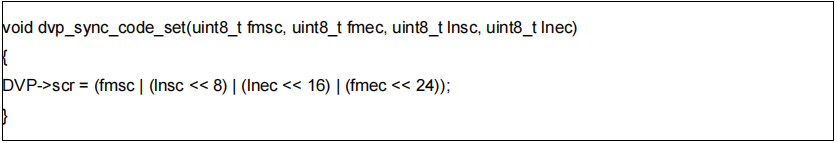

- dvp_sync_code_set

dvp_sync_code_set(0xFF, 0xFF, 0xC7, 0xDA)

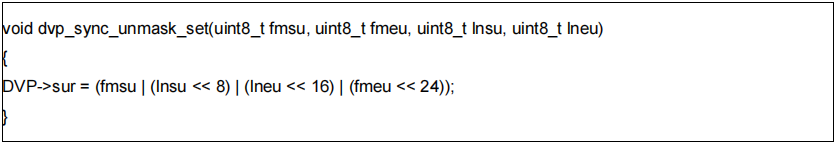

dvp_sync_code_set(0xFF, 0xFF, 0xC7, 0xDA)- dvp_sync_unmask_set

dvp_sync_unmask_set(0, 0, 0, 0)

捕获模式

dvp_sync_unmask_set(0, 0, 0, 0)

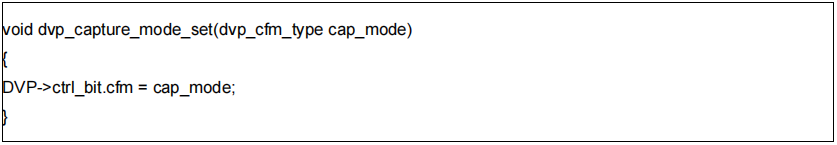

捕获模式- dvp_capture_mode_set

单帧捕获模式dvp_capture_mode_set(DVP_CAP_FUNC_MODE_SINGLE)连续捕获模式dvp_capture_mode_set(DVP_CAP_FUNC_MODE_CONTINUOUS)

帧率控制-基本型

单帧捕获模式dvp_capture_mode_set(DVP_CAP_FUNC_MODE_SINGLE)连续捕获模式dvp_capture_mode_set(DVP_CAP_FUNC_MODE_CONTINUOUS)

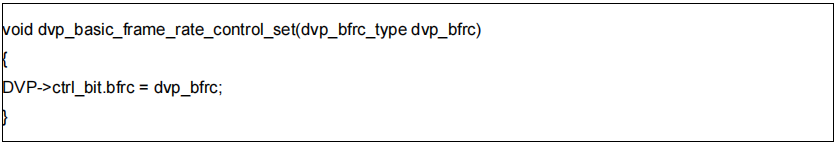

帧率控制-基本型 需搭配连续捕获模式dvp_capture_mode_set(DVP_CAP_FUNC_MODE_CONTINUOUS);可以将sensor的帧率再往下调整-不改变sensor帧率dvp_basic_frame_rate_control_set(DVP_BFRC_ALL)-将sensor帧率降低为两帧取一帧dvp_basic_frame_rate_control_set(DVP_BFRC_HALF)-将sensor帧率降低为四帧取一帧dvp_basic_frame_rate_control_set(DVP_BFRC_QUARTER)

帧率控制-进阶型

需搭配连续捕获模式dvp_capture_mode_set(DVP_CAP_FUNC_MODE_CONTINUOUS);可以将sensor的帧率再往下调整-不改变sensor帧率dvp_basic_frame_rate_control_set(DVP_BFRC_ALL)-将sensor帧率降低为两帧取一帧dvp_basic_frame_rate_control_set(DVP_BFRC_HALF)-将sensor帧率降低为四帧取一帧dvp_basic_frame_rate_control_set(DVP_BFRC_QUARTER)

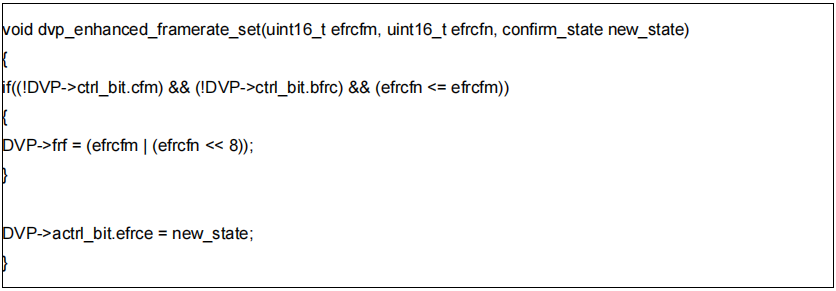

帧率控制-进阶型- dvp_enhanced_framerate_set

需搭配连续捕获模式dvp_enhanced_framerate_set(M, N, TRUE)M>=N

剪裁窗口

需搭配连续捕获模式dvp_enhanced_framerate_set(M, N, TRUE)M>=N

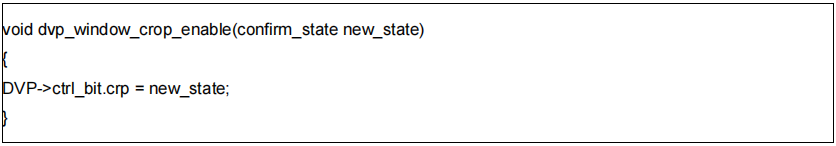

剪裁窗口- dvp_enhanced_framerate_set

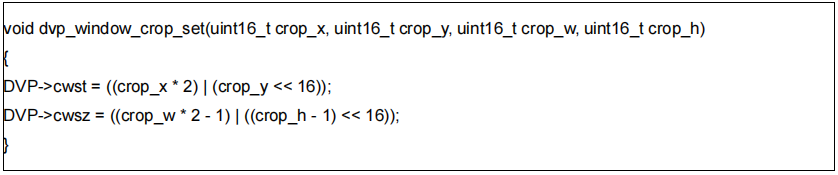

- void dvp_window_crop_set

dvp_window_crop_enable(TRUE)dvp_window_crop_set(crop_x, crop_y, crop_w, crop_h)crop_x / crop_y / crop_w / crop_h单位为pixelcrop_x(0x0000~0x3FFF): cropping window horizontal start pixelcrop_y(0x0000~0x1FFF): cropping window vertical start pixelcrop_w(0x0001~0x3FFF): cropping window horizontal pixel numbercrop_h(0x0001~0x3FFF): cropping window vertical pixel numbercrop_x+crop_w>=sensor输出到dvp的影像宽度(pixel)crop_y+crop_h>=sensor输出到dvp的影像高度(pixel)

图像尺寸调整-基本型

dvp_window_crop_enable(TRUE)dvp_window_crop_set(crop_x, crop_y, crop_w, crop_h)crop_x / crop_y / crop_w / crop_h单位为pixelcrop_x(0x0000~0x3FFF): cropping window horizontal start pixelcrop_y(0x0000~0x1FFF): cropping window vertical start pixelcrop_w(0x0001~0x3FFF): cropping window horizontal pixel numbercrop_h(0x0001~0x3FFF): cropping window vertical pixel numbercrop_x+crop_w>=sensor输出到dvp的影像宽度(pixel)crop_y+crop_h>=sensor输出到dvp的影像高度(pixel)

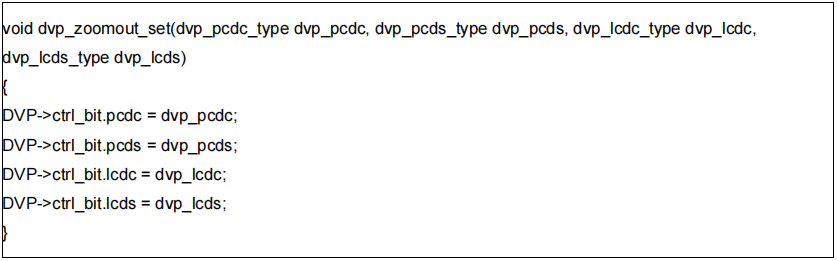

图像尺寸调整-基本型- dvp_zoomout_set

dvp_zoomout_set(dvp_pcdc, dvp_pcds, dvp_lcdc, dvp_lcds);

dvp_pcdc:-DVP_PCDC_ALL, 全部捕获,或是使用进阶型图像尺寸调缩功能-DVP_PCDC_ONE_IN_TWO, 启用捕获舍弃控制,于两个像素数据之中,捕获一个-DVP_PCDC_ONE_IN_FOUR, 启用捕获舍弃控制,于四个像素数据之中,捕获一个-DVP_PCDC_TWO_IN_FOUR, 于四个像素数据之中,捕获连续两个dvp_pcds:

-DVP_PCDS_CAP_FIRST, 捕获第一组数据(一个或两个像素数据),舍弃下一组-DVP_PCDS_DROP_FIRST, 舍弃第一组数据(一个或两个像素数据),捕获下一组dvp_lcdc:

-DVP_LCDC_ALL, 全部捕获,或是使用进阶型图像尺寸调缩功能-DVP_LCDC_ONE_IN_TWO, 启用捕获舍弃控制,于两条图像行之中,捕获一条dvp_lcds:

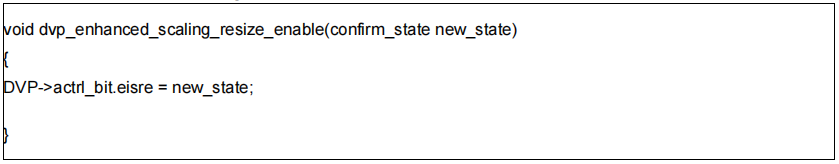

-DVP_LCDS_CAP_FIRST, 捕获第一条图像行之数据,舍弃下一条-DVP_LCDS_DROP_FIRST, 舍弃第一条图像行之数据,捕获下一条 图像尺寸调整-进阶型- dvp_enhanced_scaling_resize_enable

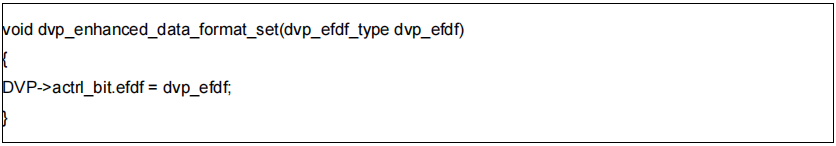

- dvp_enhanced_data_format_set

dvp_enhanced_scaling_resize_enable(TRUE)dvp_enhanced_data_format_set(dvp_efdf)dvp_efdf:-DVP_EFDF_YUV422_UYVY, YUV422(UYVY / VYUY)格式数据输入-DVP_EFDF_YUV422_YUYV, YUV422(YUYV / YVYU)格式数据输入-DVP_EFDF_YUV444, YUV444格式数据输入-DVP_EFDF_Y8, Y8(Y only)格式数据输入dvp_enhanced_scaling_resize_set(src_w, des_w, src_h, des_h)需搭配连续基本型全部捕获src_w: 水平尺寸调缩来源系数,使能进阶型图像尺寸调缩功能时(EISRE=1),此寄存器值不得为0des_w: 水平尺寸调缩目标系数,使能进阶型图像尺寸调缩功能时(EISRE=1),此寄存器值不得为0,亦不得大于src_wsrc_h: 垂直尺寸调缩来源系数,使能进阶型图像尺寸调缩功能时(EISRE=1),此寄存器值不得为0des_h: 垂直尺寸调缩目标系数,使能进阶型图像尺寸调缩功能时(EISRE=1),此寄存器值不得为0,亦不得大于src_h

灰阶图像二值化转换

dvp_enhanced_scaling_resize_enable(TRUE)dvp_enhanced_data_format_set(dvp_efdf)dvp_efdf:-DVP_EFDF_YUV422_UYVY, YUV422(UYVY / VYUY)格式数据输入-DVP_EFDF_YUV422_YUYV, YUV422(YUYV / YVYU)格式数据输入-DVP_EFDF_YUV444, YUV444格式数据输入-DVP_EFDF_Y8, Y8(Y only)格式数据输入dvp_enhanced_scaling_resize_set(src_w, des_w, src_h, des_h)需搭配连续基本型全部捕获src_w: 水平尺寸调缩来源系数,使能进阶型图像尺寸调缩功能时(EISRE=1),此寄存器值不得为0des_w: 水平尺寸调缩目标系数,使能进阶型图像尺寸调缩功能时(EISRE=1),此寄存器值不得为0,亦不得大于src_wsrc_h: 垂直尺寸调缩来源系数,使能进阶型图像尺寸调缩功能时(EISRE=1),此寄存器值不得为0des_h: 垂直尺寸调缩目标系数,使能进阶型图像尺寸调缩功能时(EISRE=1),此寄存器值不得为0,亦不得大于src_h

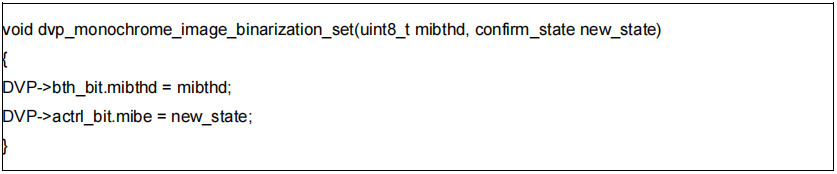

灰阶图像二值化转换- dvp_monochrome_image_binarization_set

dvp_monochrome_image_binarization_set(mibthd, TRUE)mibthd: 灰阶图像二值化阀值,灰阶图像依此阀值进行二值化转换,数值大于阀值者判定为1,小于阀值者判定为0

dvp_monochrome_image_binarization_set(mibthd, TRUE)mibthd: 灰阶图像二值化阀值,灰阶图像依此阀值进行二值化转换,数值大于阀值者判定为1,小于阀值者判定为0

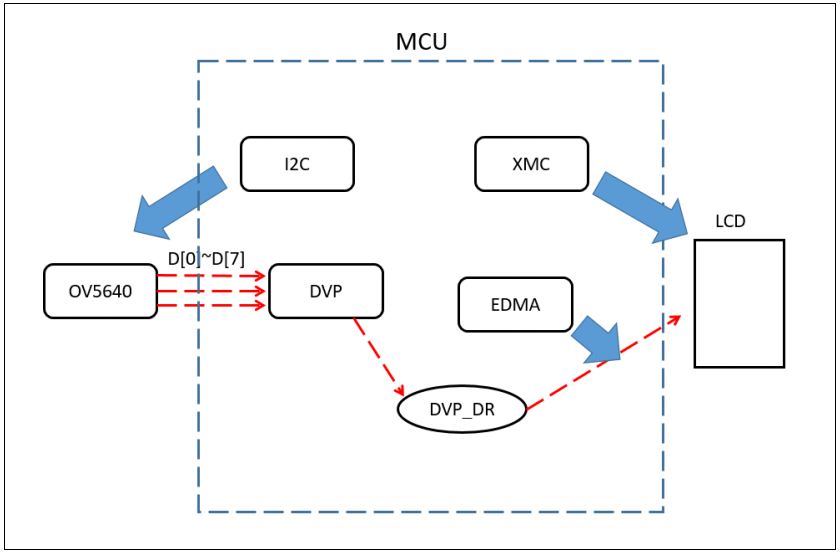

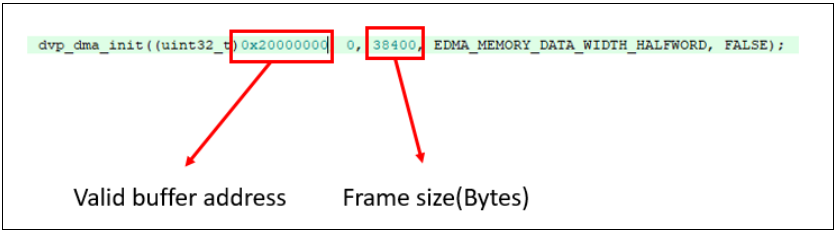

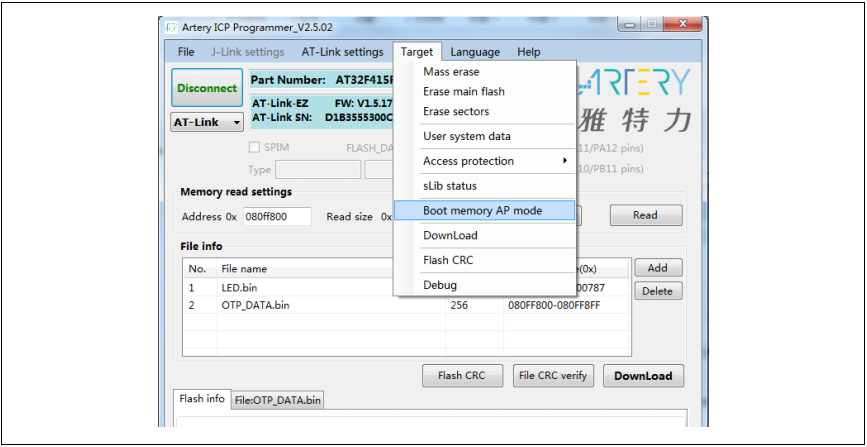

Sensor-DVP-LCD

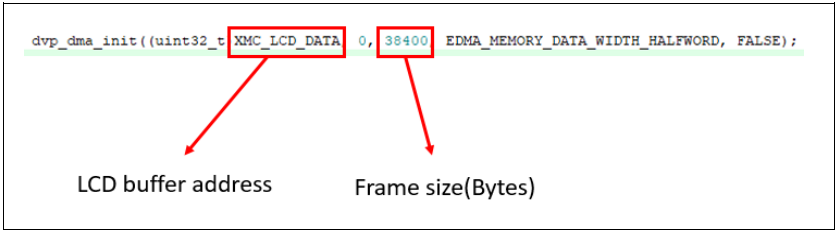

图34. Sensor–DVP-LCD Step1: Initiate sensor OV5640 (By I2C) and LCD (By XMC)Step2: Configure DVPStep3: Configure EDMA图35. dvp_dma_init

Step1: Initiate sensor OV5640 (By I2C) and LCD (By XMC)Step2: Configure DVPStep3: Configure EDMA图35. dvp_dma_init Step4: Enable DVPStep1~3无顺序相依性,但Step4一定要最后执行可从LCD上直接显示实际影像

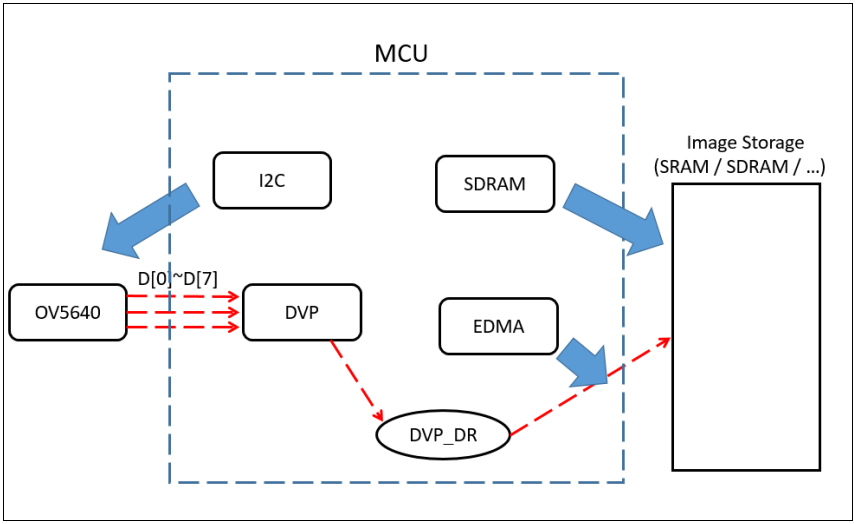

图36. Sensor–DVP–SRAM(or SDRAM)

Step4: Enable DVPStep1~3无顺序相依性,但Step4一定要最后执行可从LCD上直接显示实际影像

图36. Sensor–DVP–SRAM(or SDRAM) Step1: Initiate sensor OV5640 (By I2C) and SRAM/SDRAMStep2: Configure DVPStep3: Configure EDMA

Step1: Initiate sensor OV5640 (By I2C) and SRAM/SDRAMStep2: Configure DVPStep3: Configure EDMA图37. dvp_dma_init

Step4: Enable DVPStep1~3无顺序相依性,但Step4一定要最后执行可以循以下方式输出影像(影像传输完毕后须关闭DMA以及DVP防止影像被覆盖):1. 使用J-Link或其他软件撷取出影像buffer内容,再用可看指定影像格式的软件观看2. 使用UART或其他方式将影像buffer内容传输至PC,再用可看指定影像格式的软件观看

Step4: Enable DVPStep1~3无顺序相依性,但Step4一定要最后执行可以循以下方式输出影像(影像传输完毕后须关闭DMA以及DVP防止影像被覆盖):1. 使用J-Link或其他软件撷取出影像buffer内容,再用可看指定影像格式的软件观看2. 使用UART或其他方式将影像buffer内容传输至PC,再用可看指定影像格式的软件观看图38. PC View

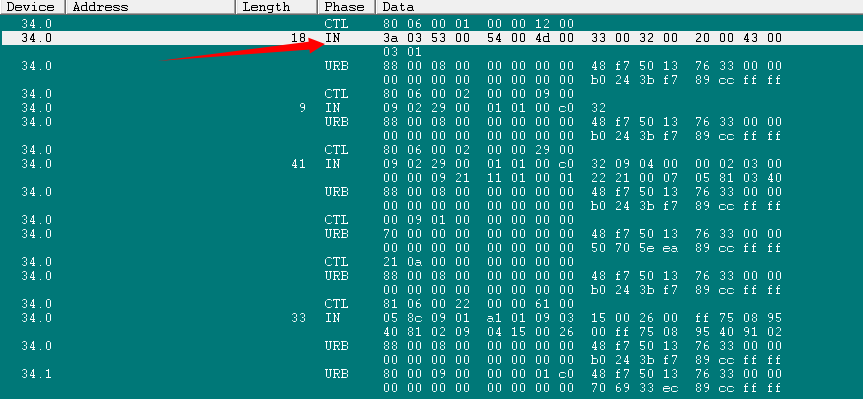

EDMA link list mode

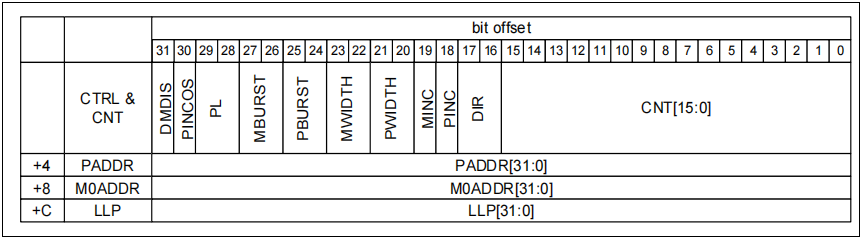

如果应用上不会改变DVP输出影像的大小,就可以考虑用EDMA的link list mode来提高DMA的效率。经由链接列表传输机制,用户可以将几种不同的传输链接在一起,以提高DMA应用程序的系统吞吐量。每个传输信息都可以通过软件存储在描述符中,并且DMA从主存储器加载描述符。

Link list机制为:

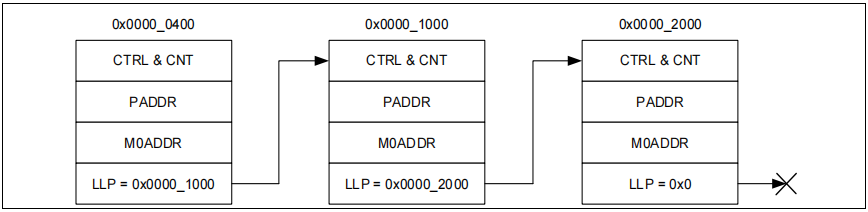

1. 预先规划一块buffer存放link list table,内容格式如下,详细内容请参考EDMA章节图39. 描述符格式

图40. 链接列表指针的用法

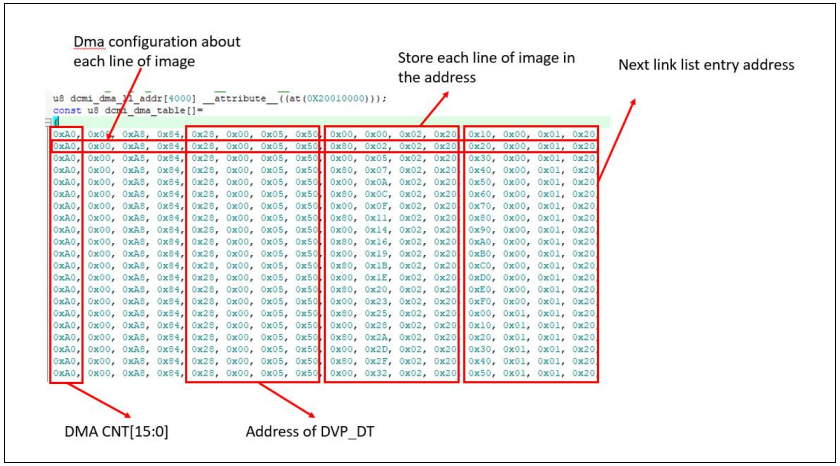

2. 建立link list table(需预先规划存放影像的地址)

Example:图41. link list table (1) 假定影像输出的大小为320x240格式为YUV422/RGB565单张图像文件案大小为320x240x2=153600 bytes单张影像有240条vertical line每一条line有320 pixel=640 bytes(2) 规划一块固定的Buffer存放link list table(假定位于0x20010000, 大小为4000 bytes)(3) 假定影像输出的地址为0x20020000(4) 建立link list table每一条vertical line都需要填以下信息CNT[15:0]=0xA0(DMA长度为word 4 bytes, 所以DMA CNT填640/4=0xA0)PADDR[31:0]=DVP_DT, 固定为0x5005_0028M0ADDR[31:0]=每条vertical line存放的地址(存放影像的起始地址*0x280*vertical line index)LLP[31:0]=下一笔link list entry所在地址(link list的起始地址*0x10*(vertical line index+1)), 最后一笔LLP为0代表影像结束,如要重新传输影像则填link list的起始地址

(1) 假定影像输出的大小为320x240格式为YUV422/RGB565单张图像文件案大小为320x240x2=153600 bytes单张影像有240条vertical line每一条line有320 pixel=640 bytes(2) 规划一块固定的Buffer存放link list table(假定位于0x20010000, 大小为4000 bytes)(3) 假定影像输出的地址为0x20020000(4) 建立link list table每一条vertical line都需要填以下信息CNT[15:0]=0xA0(DMA长度为word 4 bytes, 所以DMA CNT填640/4=0xA0)PADDR[31:0]=DVP_DT, 固定为0x5005_0028M0ADDR[31:0]=每条vertical line存放的地址(存放影像的起始地址*0x280*vertical line index)LLP[31:0]=下一笔link list entry所在地址(link list的起始地址*0x10*(vertical line index+1)), 最后一笔LLP为0代表影像结束,如要重新传输影像则填link list的起始地址

案例 OV5640 Capture

功能简介

实现将影像从 Sensor OV5640 输入到 DVP, 再透过 EDMA 搬移至 LCD 显示资源准备

1) 硬件环境:对应产品型号的AT-START BOARD2) 软件环境

projectat_start_f4xxexamplesdvpov5640_capture软件设计

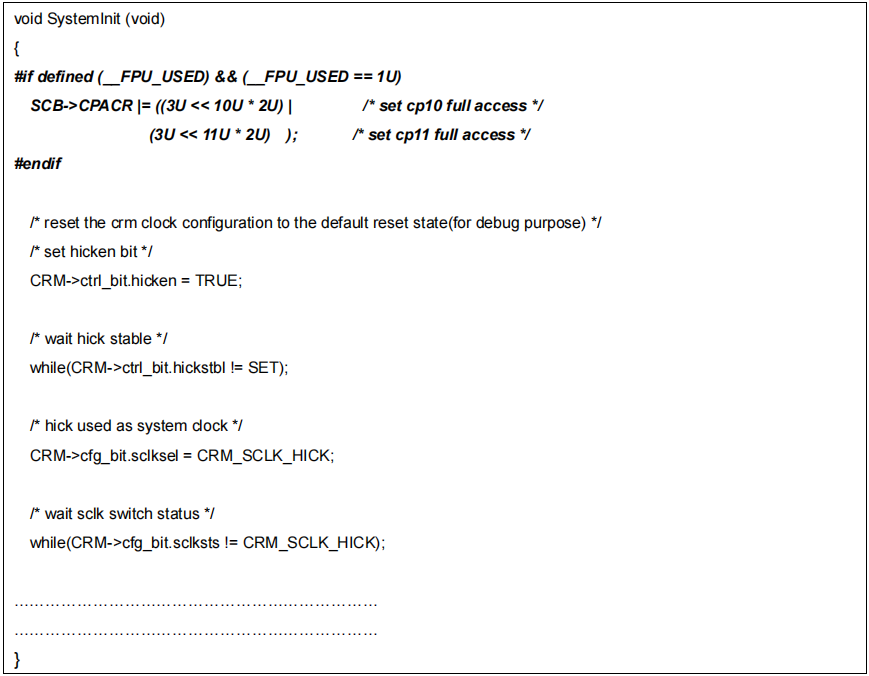

1) 配置流程- 开启DVP、EDMA、I2C、XMC时钟

- 配置LCD、OV5640、DVP

- 配置EDMA数据流

- 开启DVP、EDMA相关中断

- 开启DVP、EDMA数据流

- 确认LCD显示是否正确

2) 代码介绍

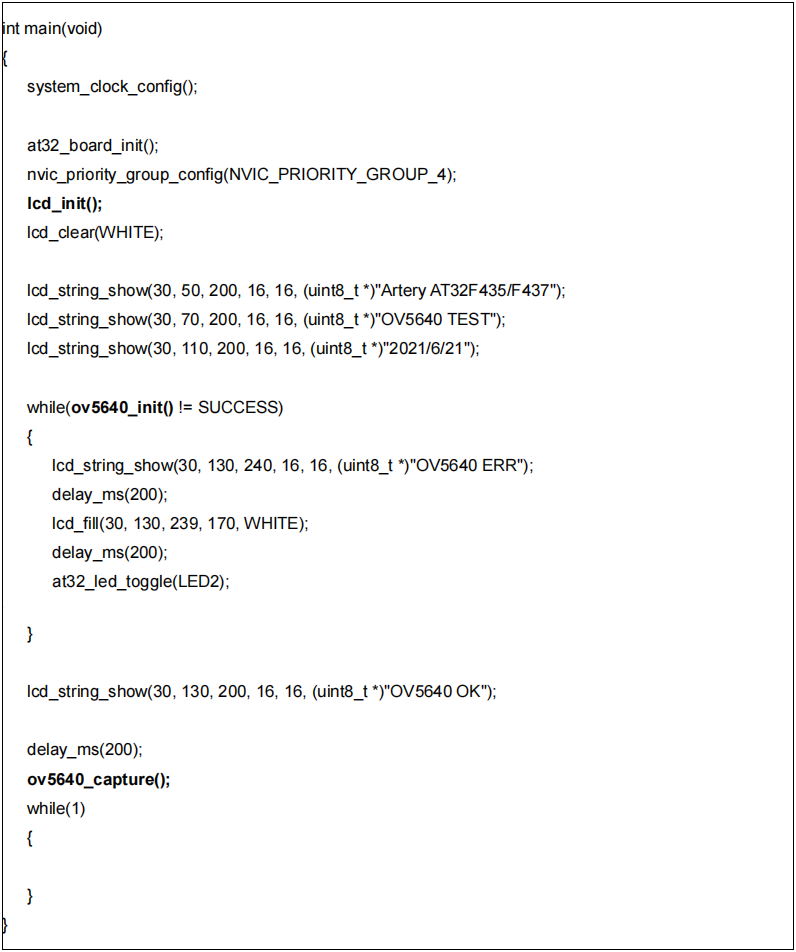

- main函数代码描述

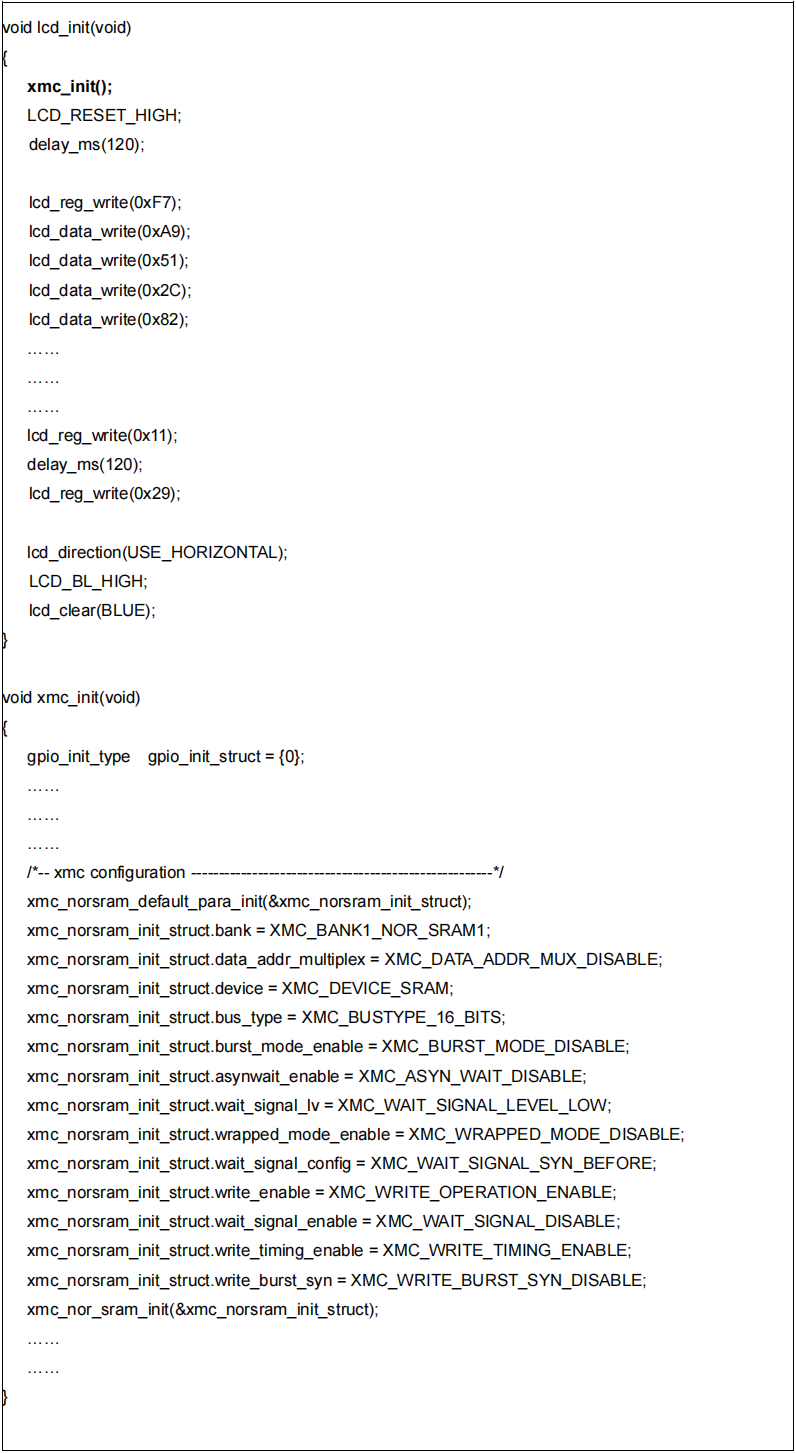

- LCD函数代码描述

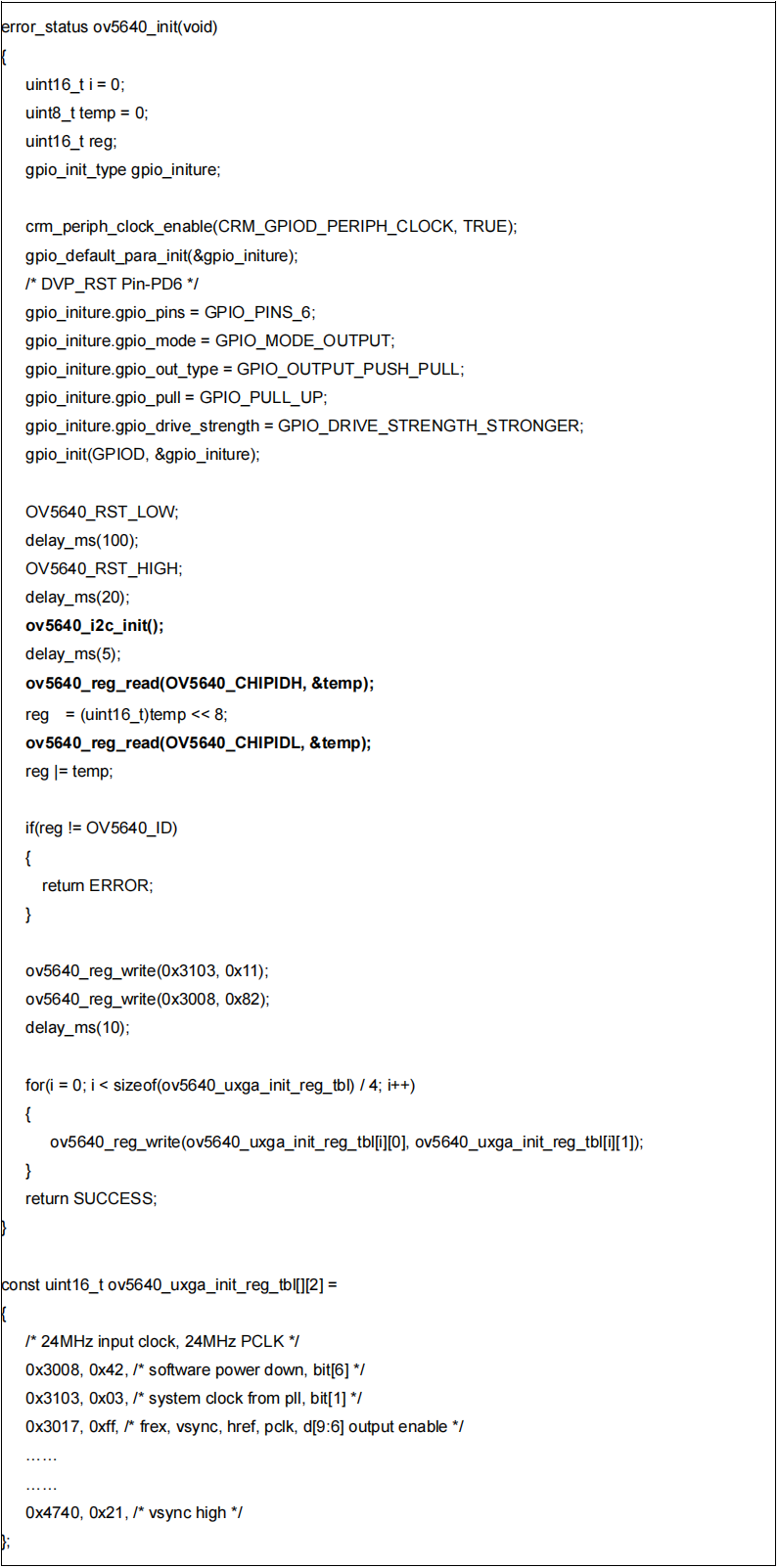

- OV5640函数代码描述

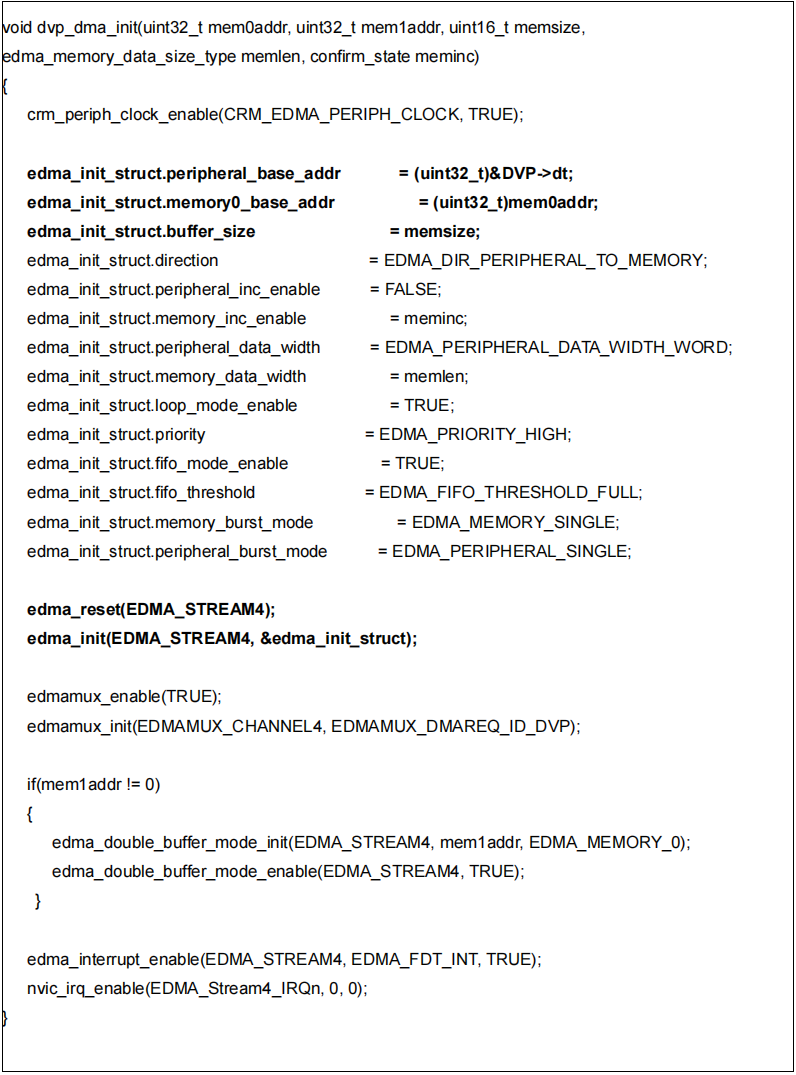

- EDMA函数代码描述

- DVP函数代码描述

实验结果

图42. LCD View 审核编辑:汤梓红

审核编辑:汤梓红 电子发烧友App

电子发烧友App

评论