SDF文件是在VCS/NC-Verilog后仿真运行时将STD/IO/Macro门级verilog中specify的延迟信息替换为QRC/Star-RC抽取的实际物理延时信息。如果SDF文件的条件信息在verilog的specify中没有的话,就会报SDFCOM_INF的warning,意思是IOPATH not found。

本文解析SDF的Header Section信息、Cell Entries信息,尤其重点讲解Cell Entries的Delay Entries信息。

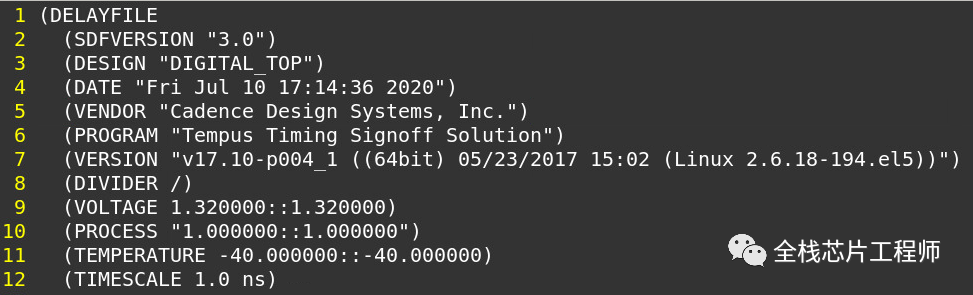

下文先讲SDF文件的第一部分Header Section

1. SDF Version Entry,包括1.0、2.1、3.0,SDF3.0是1995年release。 2. Design Name Entry,设计顶层名 3. Date Entry,SDF生成日期,PT或Tempus产生 4. Vendor Entry,Vendor信息,如下图

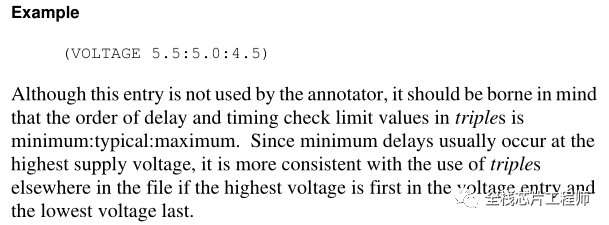

5. Program Version Entry 6. Hierarchy Divider Entry 7. Voltage Entry,SDF3.0官方解释如下

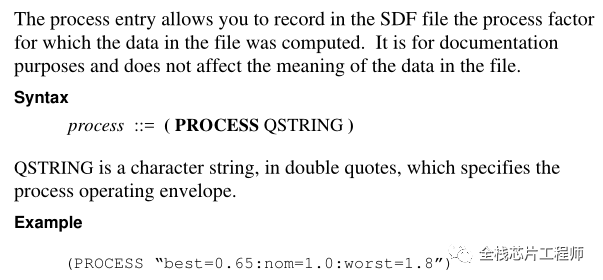

8. Process Entry,SDF3.0官方解释如下

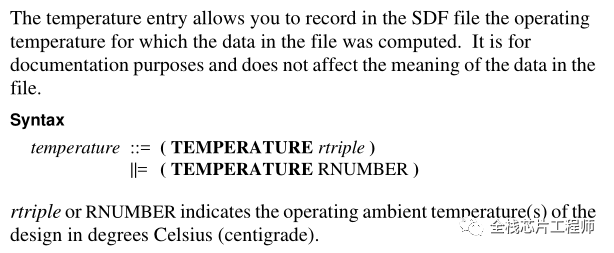

9. Temperature Entry,SDF3.0官方解释如下

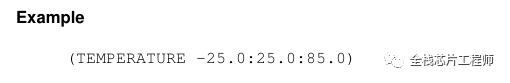

10. Timescale Entry,SDF3.0官方解释如下

下文继续讲解SDF文件的第二部分Cell Entries:

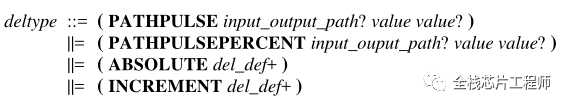

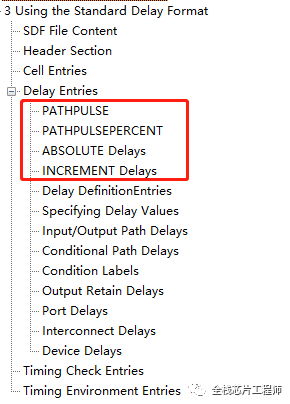

完整的Delay Entries信息格式如下:

PATHPULSE

PATHPULSEPERCENT

ABSOLUTE Delays

INCREMENT Delays

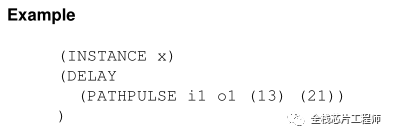

1. PATHPULSE 举例说明:

当从i1到o1输出的低电平脉冲小于13ns时,该低电平脉冲直接被忽略;

当从i1到o1输出的低电平脉冲介于13ns~21ns时,输出为X态;

当从i1到o1输出的低电平脉冲大于21ns时,正常输出低电平;

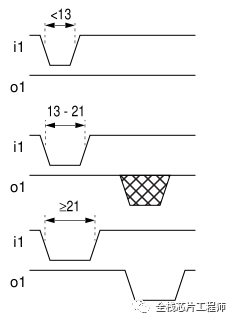

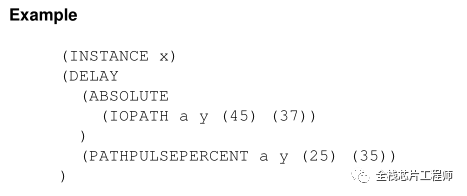

2. PATHPULSEPERCENT 本质上和PATHPULSE是一回事,只不过是按照path延时比例来计算什么时候丢弃输入脉冲宽度不足的信号(pulse rejection limit),什么时候将输入脉冲宽度不足的信号显示为X态(X limit)。比如:

以上图为例,the high-to-low delay is 37, 因此,the pulse

rejection limit is 25% of 37 and the X limit is 35% of 37.

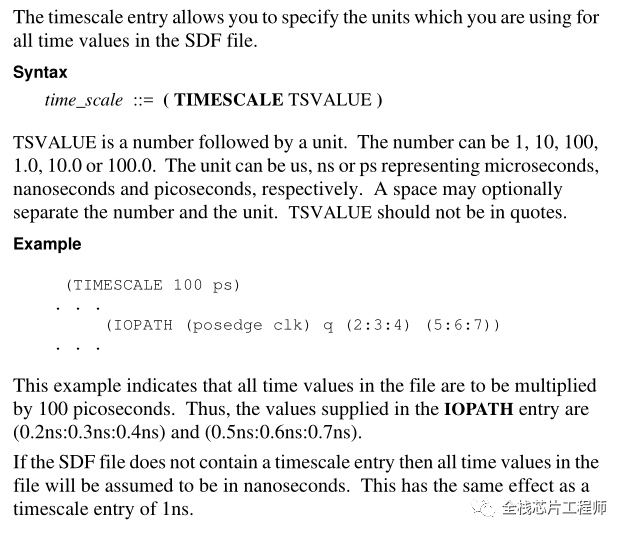

3. ABSOLUTE Delays

ABSOLUTE Delays中的物理延时数据就是用来替换verilog specify中的延时数据的。

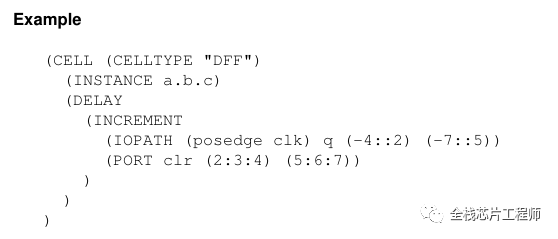

4. INCREMENT Delays

用来叠加在verilog specify中的延时数据上的,INCREMENT Delays是存在负数的情况的,叠加后的延时若是负数的话,某些EDA工具可能不支持或直接强制延时为0。

上面介绍了SDF3.0的Header Section以及Cell Entries的Delay Entries部分内容,下面继续解析Delay Entries剩下的部分。

5. Delay Definition Entries

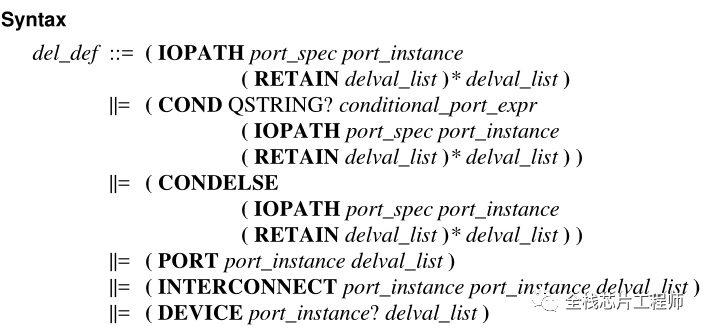

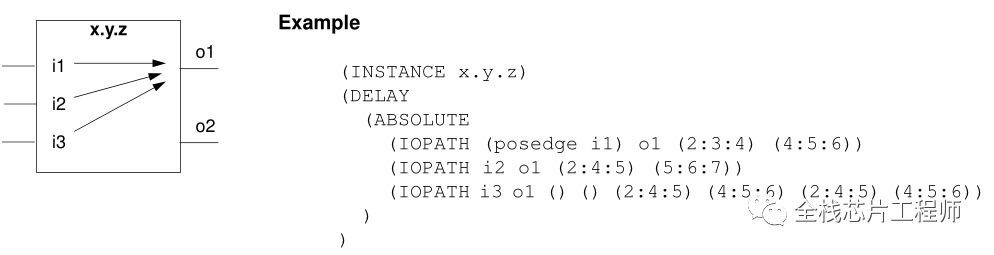

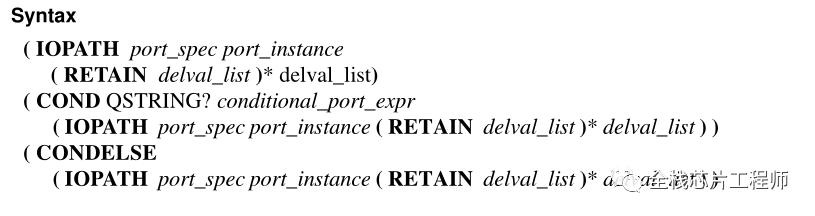

ABSOLUTE and INCREMENT delays都采用同样的Delay Definition结构,其结构语法如下:

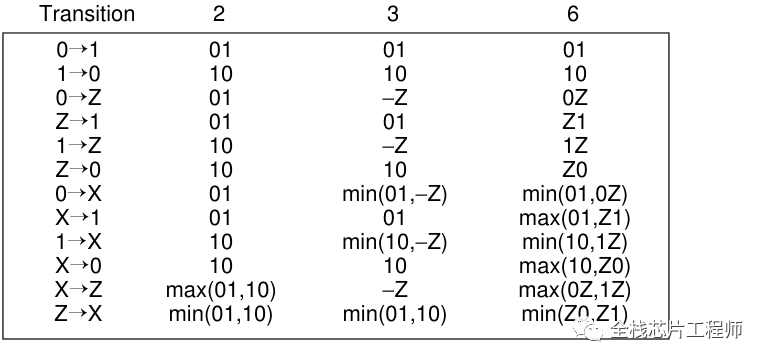

6. Specifying Delay Values Delay Values在delval_list里面指定,最多一共有12个小括号,每个小括号里面有3个值,用":"隔开,分别代表minimum、typical、maximum的延时值;在delval_list里面包含如下情况:

若12个delval值都指定了,那么每一个delval分别代表:  若2个delval值被指定,第一个delval代表01("rising")延时值,第二个delval代表10("falling")延时值; 若3个delval值被指定,第一个delval代表01("rising")延时值,第二个delval代表10("falling")延时值,第三个delval代表-Z("Z transition")延时值; 若6个delval值被指定,那么它们分别代表01、10、0Z、Z1、1Z、Z0; 举例说明,如下,IO PATH有6个delval值被指定:

若2个delval值被指定,第一个delval代表01("rising")延时值,第二个delval代表10("falling")延时值; 若3个delval值被指定,第一个delval代表01("rising")延时值,第二个delval代表10("falling")延时值,第三个delval代表-Z("Z transition")延时值; 若6个delval值被指定,那么它们分别代表01、10、0Z、Z1、1Z、Z0; 举例说明,如下,IO PATH有6个delval值被指定:

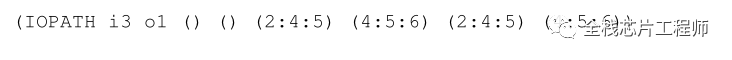

但0-1, 1-0的延迟都缺省,后面四个括号分别对应0Z、Z1、1Z、Z0,这种语法SDF3.0是支持的,annotator工具反标的时候就不会替换verilog specify的0-1, 1-0转换延迟值。 7. Input/Output Path Delays 如下,port_spec是输入/双向IO,可以有edge identifier。 port_instance是输出/双向IO,不能有edge identifier。

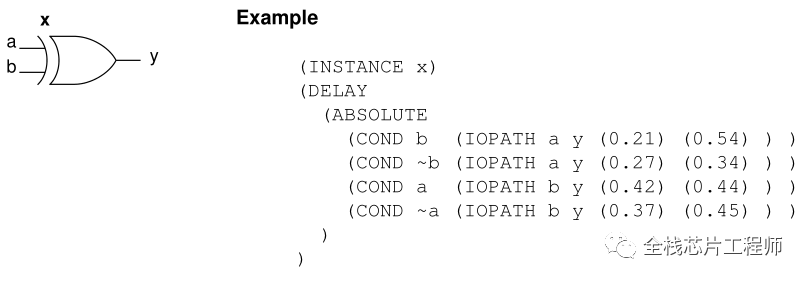

8. Conditional Path Delays 语法如下,QSTRING作为Condition Labels是可选的。

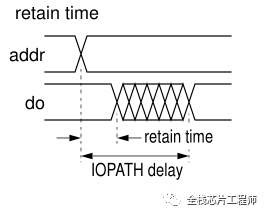

特别需要注意的是,在none of the conditions specified for the path in the model are TRUE but a signal must still be propagated over the path,因此,CONDELSE可以用来指定条件脱靶的情况: CONDELSE ( IOPATH port_spec port_instance delval_list ) 9. Condition Labels QSTRING作为Condition Labels是可选的,有些EDA工具反标的时候可能会用Condition Labels Name进行占位。 10. Output Retain Delays 输出端口output/bidirectional port的数据在输入发生变化后保持的时间,通常发生在memory/register file的数据选择端/地址端到数据输出端的路径。

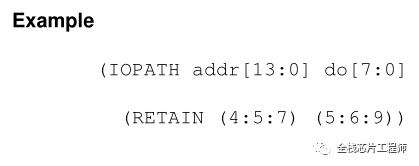

第一个delval(4,5,7)是rising trigger情况下的do,从0到X的延时; 第二个delval(5,6,9)是falling trigger情况下的do,从1到X的延时; 11. Port Delays

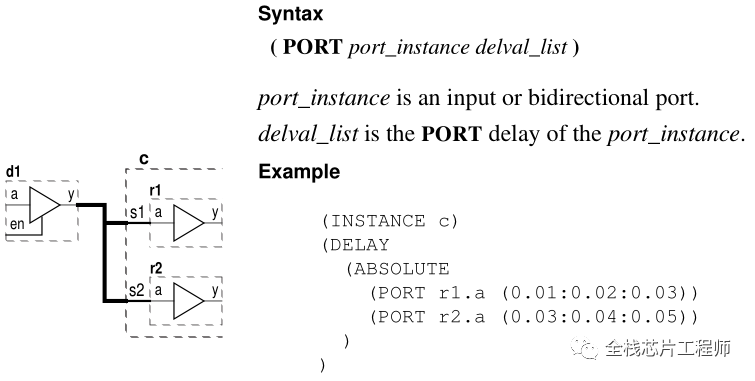

12. Interconnect Delays

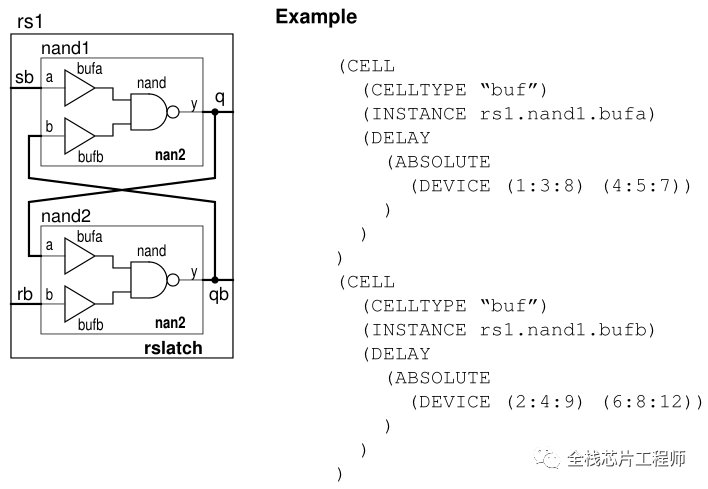

13. Device Delays

下文继续讲解SDF文件的Timing Checks Entries、Timing Environment Entries两个部分

(一)SDF3.0 Timing Checks主要分以下两种:

VCS/NC-Verilog后仿真在timing violation时报出warning;

Timing Sign-Off工具报出timing check violations;

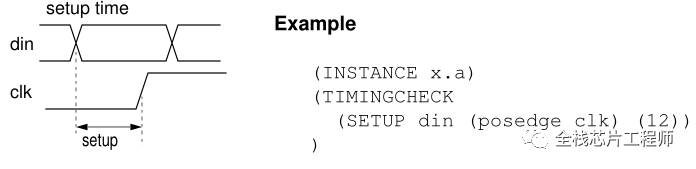

以时序分析工具Sign-Off为主,后仿为辅,SDF3.0 Timing Checks具体的类型如下: 1. Setup Timing Check

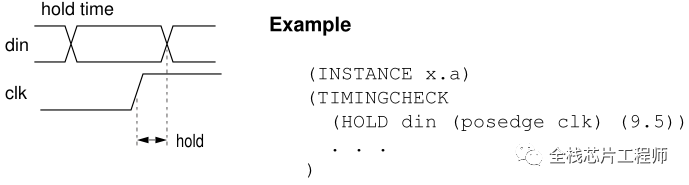

2. Hold Timing Check

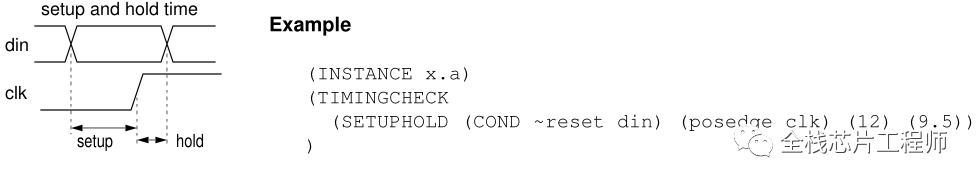

3. SetupHold Timing Check 注意,示例中~reset必须为真(Ture),timing check才会进行,此外,12是建立时间要求,9.5是保持时间要求。

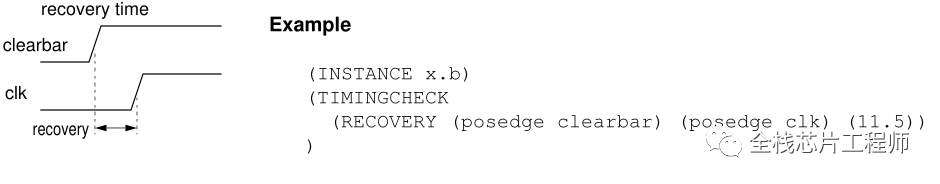

4. Recovery Timing Check

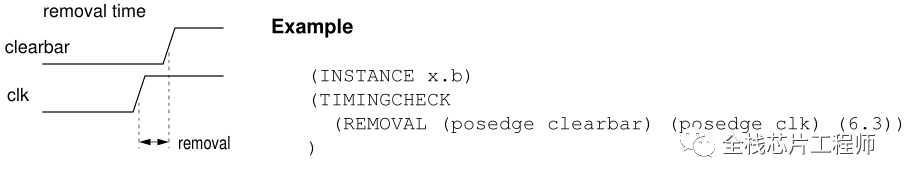

5. Removal Timing Check

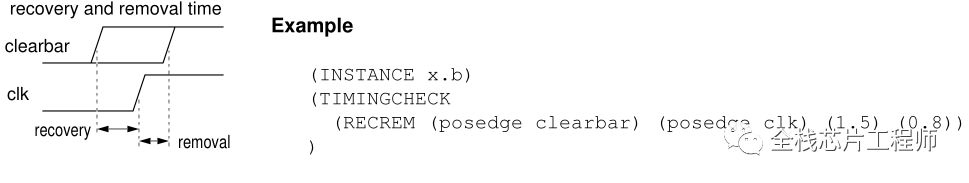

6. Recovery/Removal Timing Check 示例中,recovery time为1.5个time unit,removal time为0.8个time unit。

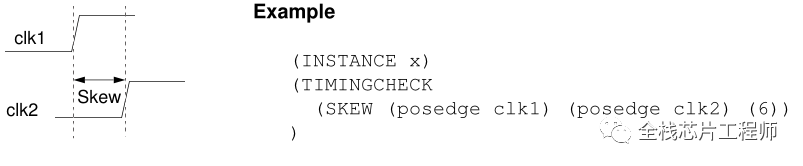

7. Skew Timing Check

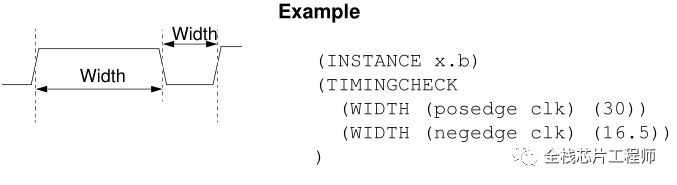

8. Width Timing Check 示例中,第一个minimum pulse width检查是posedge clock驱动的high phase;第二个minimum pulse width检查是negedge clock驱动的low phase;

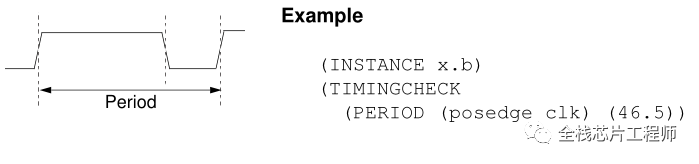

9. Period Timing Check 示例中,两个连续上升沿之间或两个连续下降沿之间的最小Cycle时间。

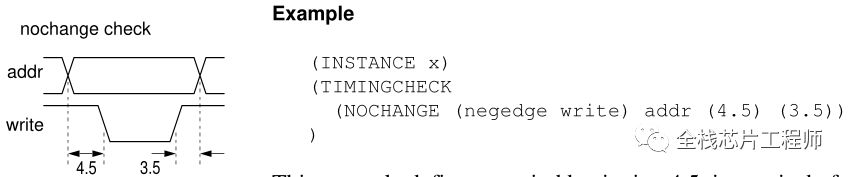

10. No Change Timing Check 示例中,addr提前write下降沿4.5个time unit, addr晚于write上升沿3.5个time unit。

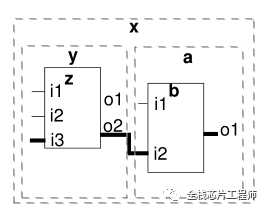

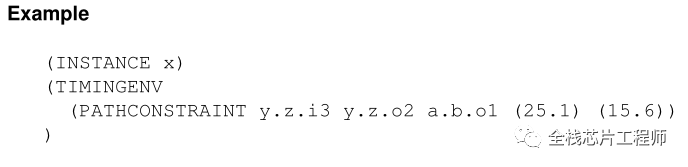

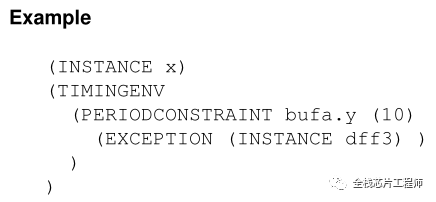

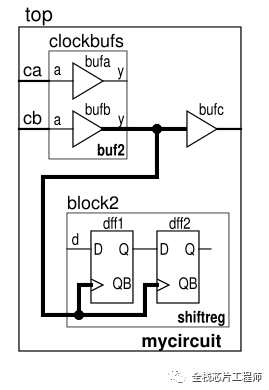

(二)SDF3.0 Timing Environment Entries SDF3.0 Timing Environment Entries分成Constraints与Timing Environment两个部分,首先解析Constraints。 1.Constraints 首先,SDF3.0 Timing Environment包括以下几类constraints: a)Path Constraint 针对timing analysis中发现的关键路径添加的约束,PR工具可以利用这些约束优化physical design,该约束指定路径的最大延时; 如下图, y.z.i3是path起点,a.b.o1是path终点,25.1是起点和终点之间的maximum rise delay,15.6是起点和终点之间的maximum fall delay。

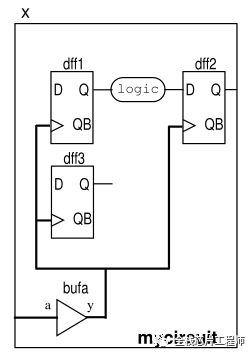

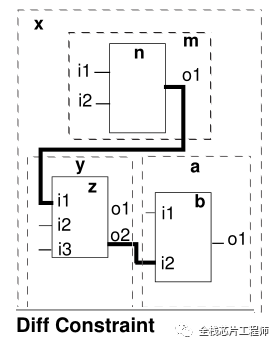

b)Period Constraint 时钟树上common clock到其驱动的leaf cell的路径的最大延迟约束。

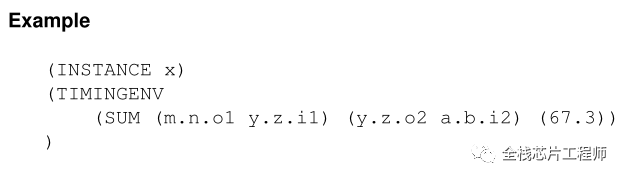

c)Sum Constraint 顾名思义,指的是几条路径的延时之和。示例中,约束两条net的延时之和小于67.3个time unit。

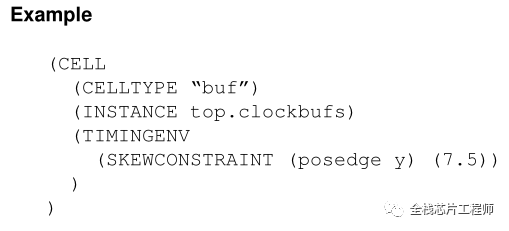

d)Skew Constraint

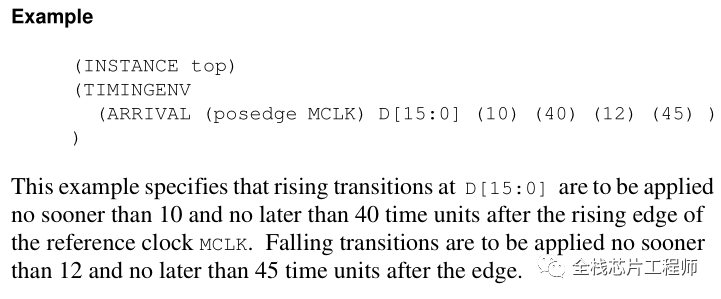

2.Timing Environment SDF3.0 Timing Environment Entries分成Constraints与Timing Environment两个部分,上文解析了Constraints,现在解析Timing Environment。Timing Environment包含以下4点约束 a)Arrival Time

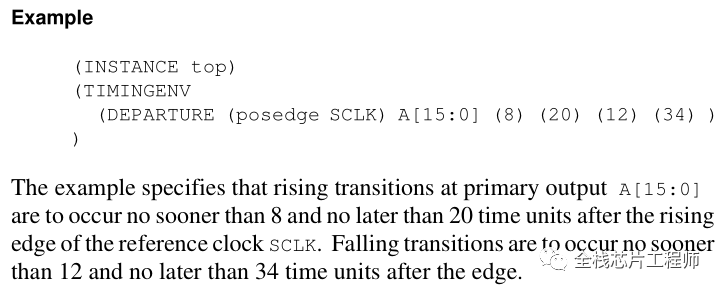

b)Departure Time

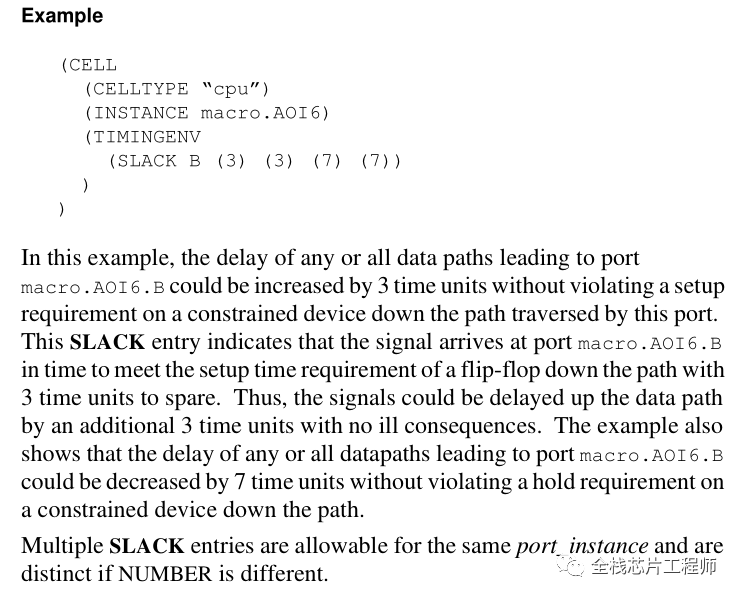

c)Slack Time

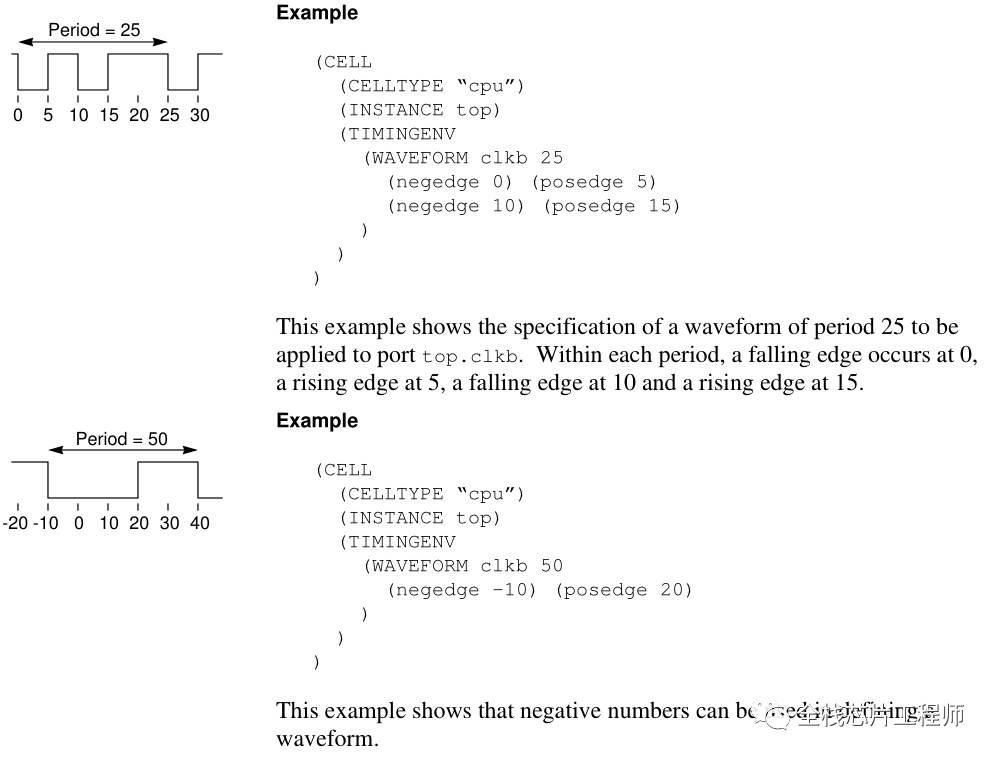

d)Waveform Specification

实战ISP图像算法效果

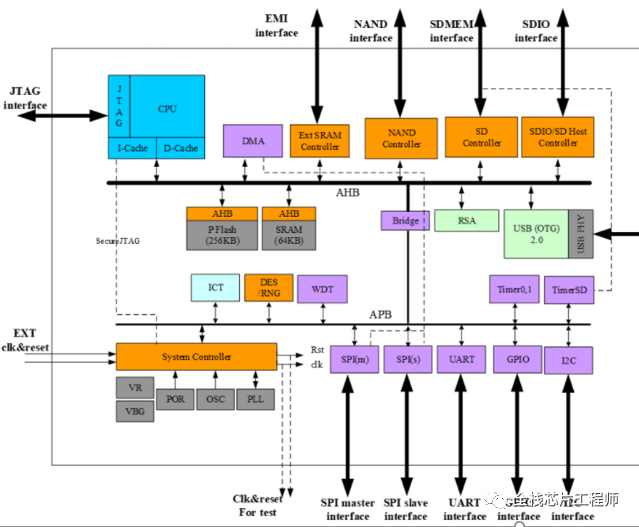

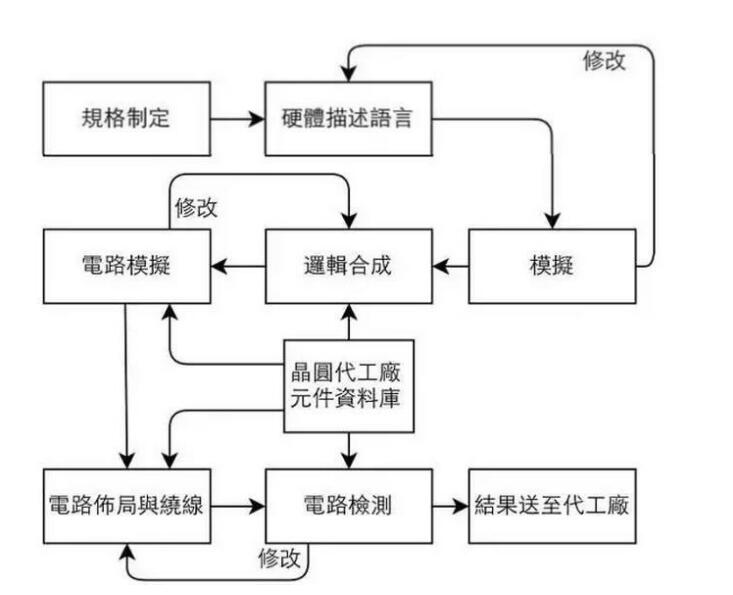

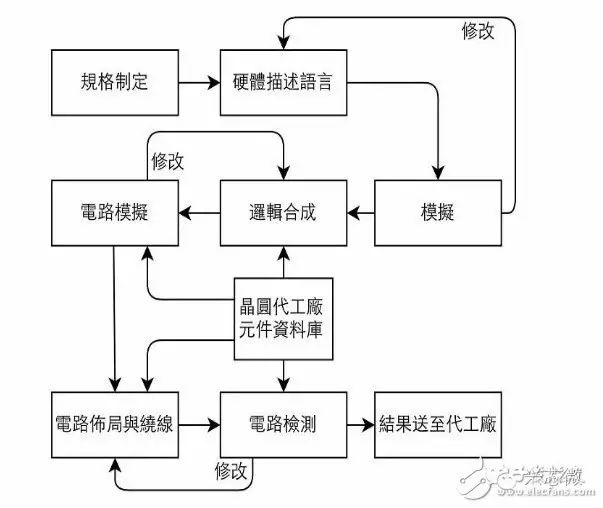

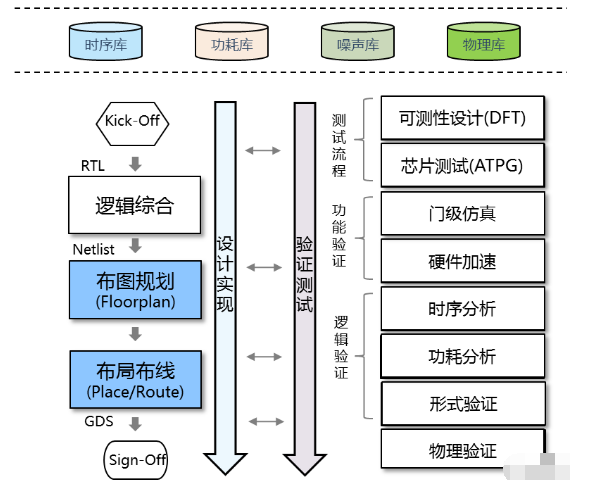

知识星球发起MCU项目启动,大家一起参与MCU项目规格启动讨论,我把设计、验证、DFT、后端的知识点全部罗列出来,大家一起来完善。

以项目驱动的方式介绍MCU芯片全流程设计的方法;提炼相关的检查列表、signoff checklist的样本;让星球成员熟悉SoC架构、设计流程、开发进度、项目管理;

编辑:黄飞

电子发烧友App

电子发烧友App

评论