CHR-O2湿敏电阻工作原理及结构图

〓原理〓阻抗

2009-11-30 09:54:21 3146

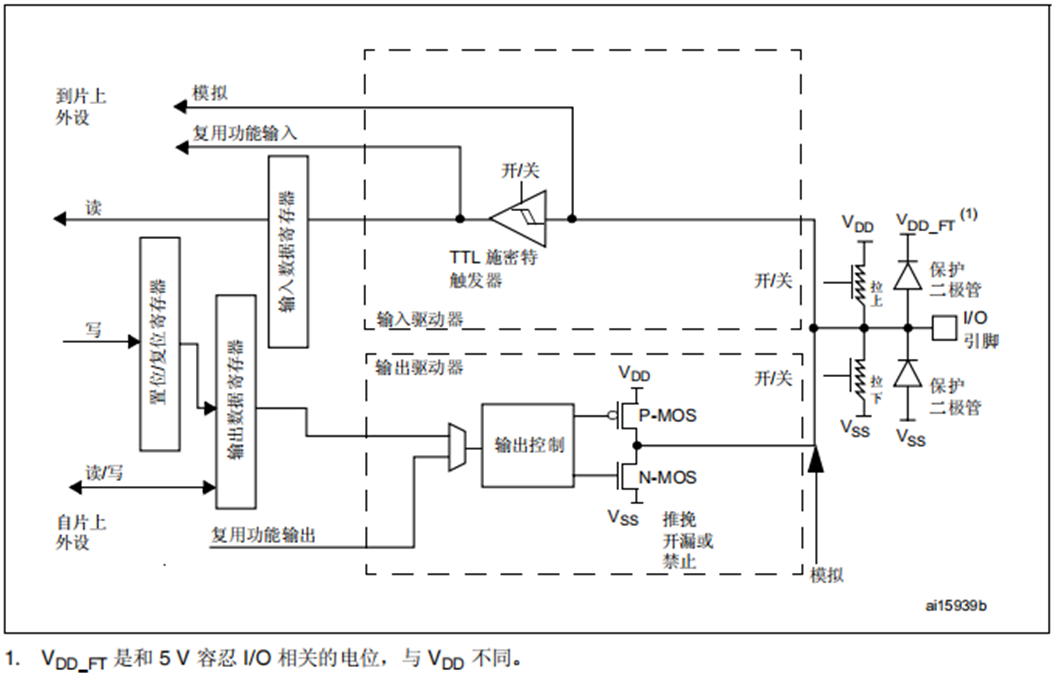

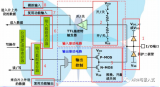

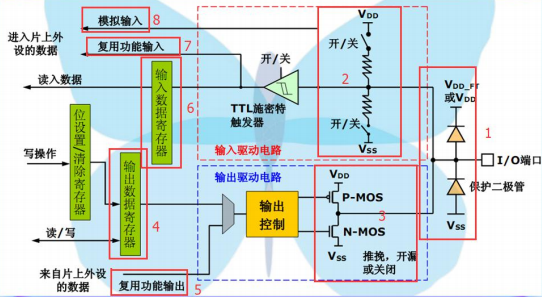

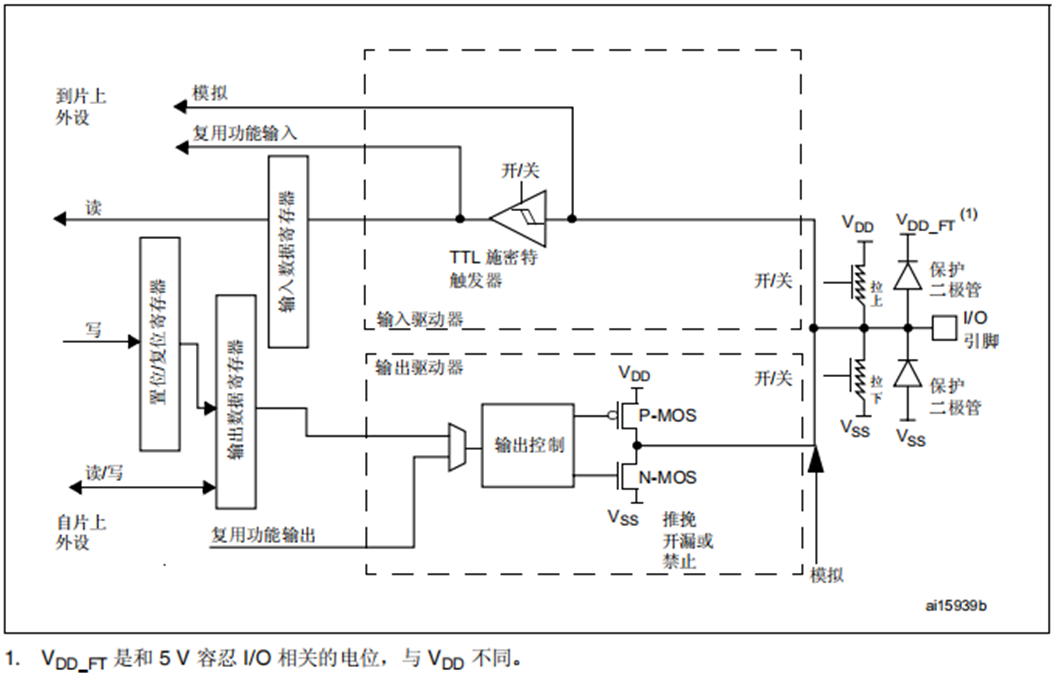

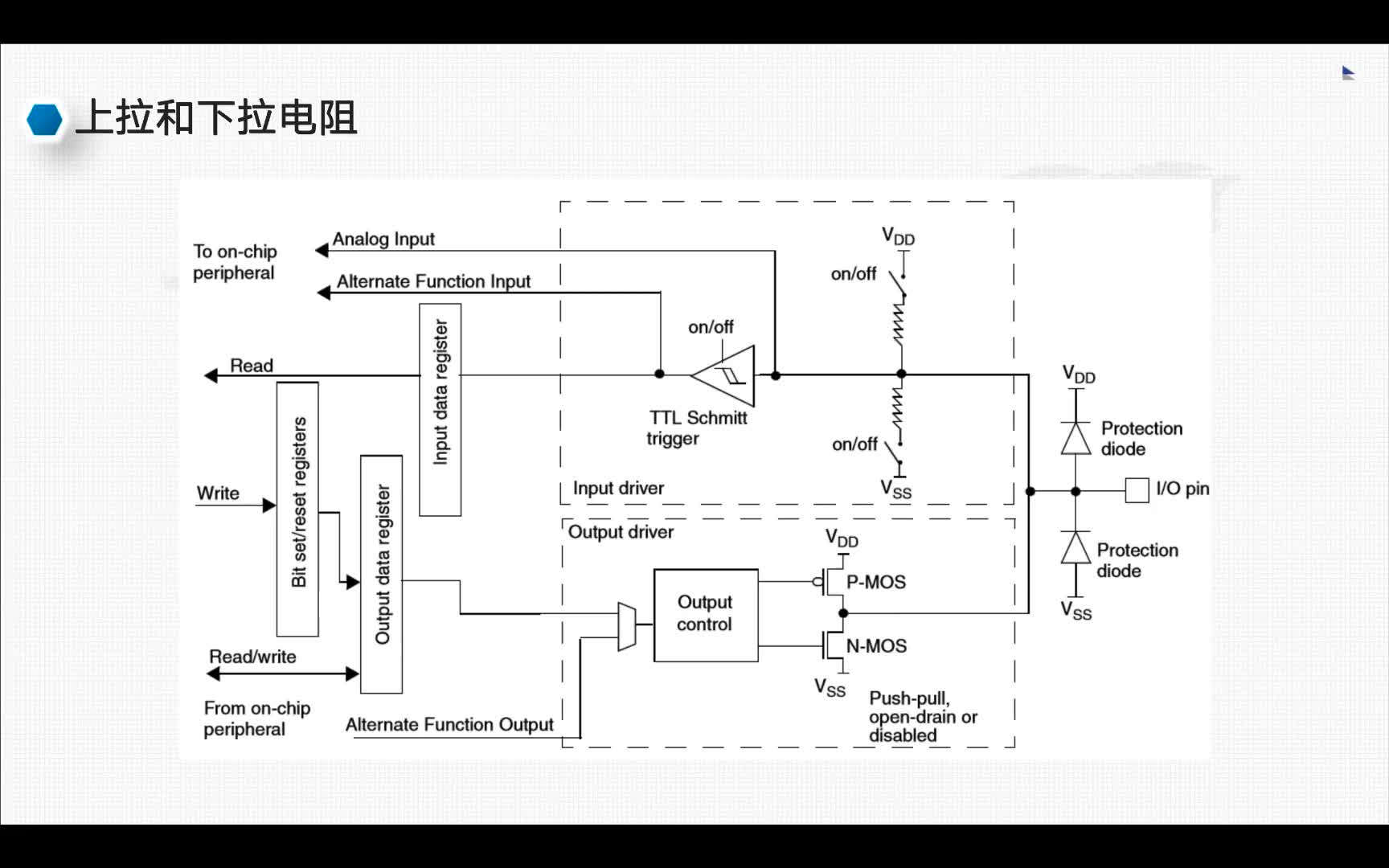

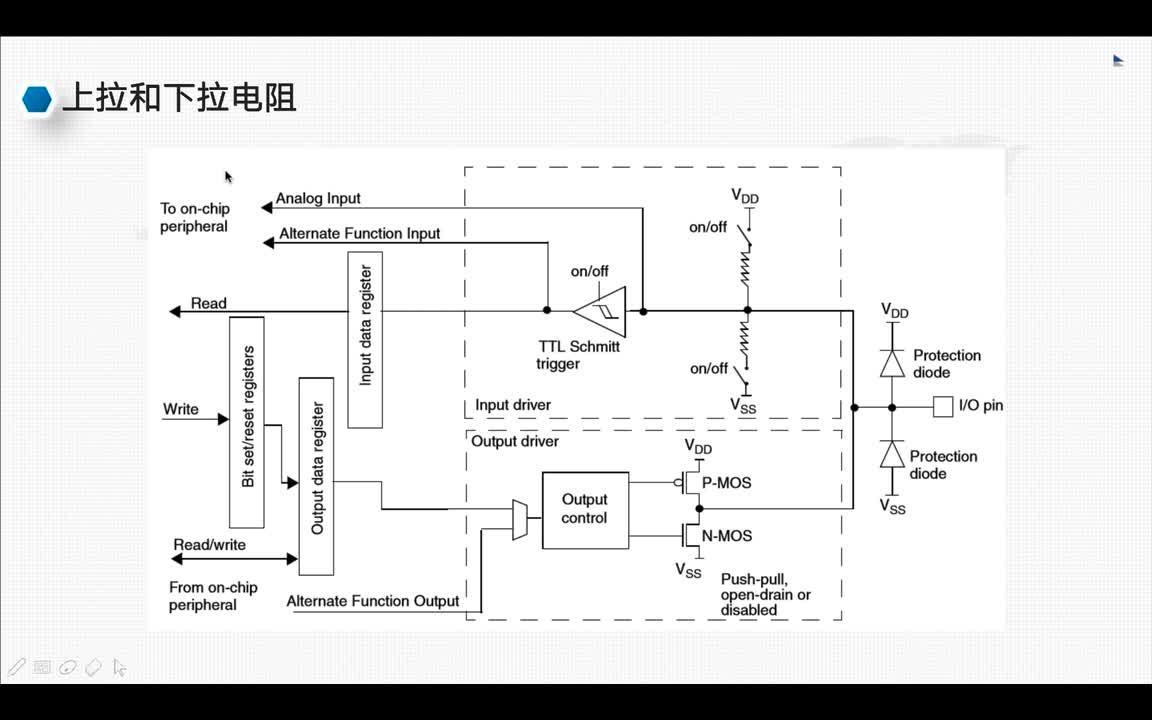

3146 在之前围绕STM32的GPIO的基本结构进行了介绍,图1为STM32的5V容忍的GPIO口内部基本结构图,图2为GPIO的基本结构中各个模块部分的概述。

2023-04-14 10:40:14 1297

1297

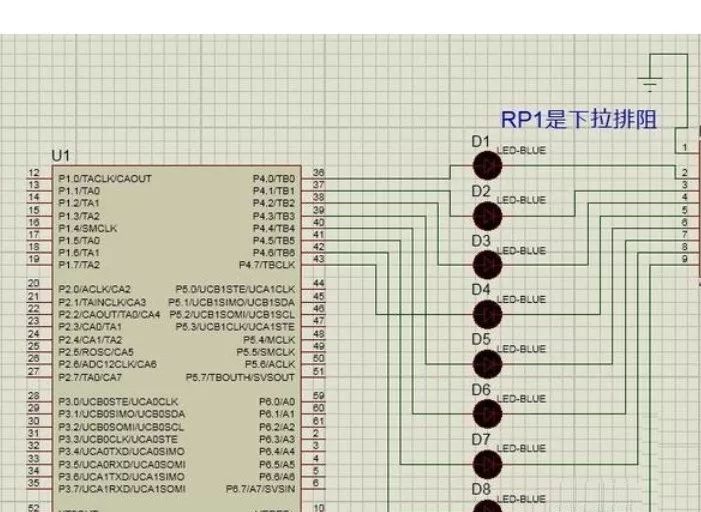

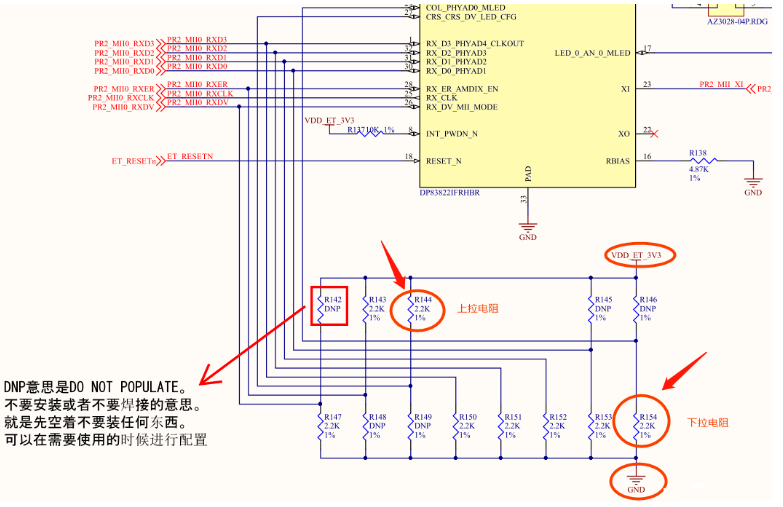

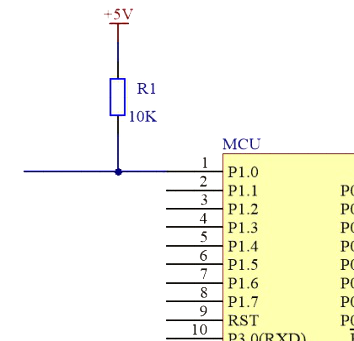

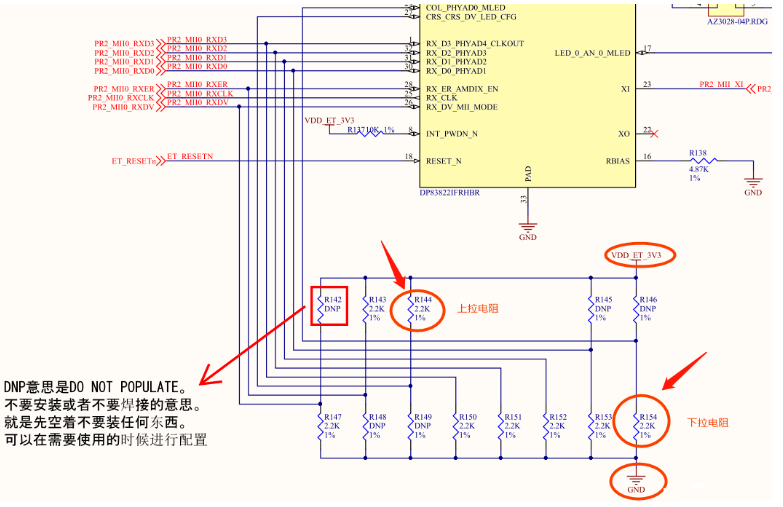

一、上下拉电阻介绍 上拉电阻:将一个不确定的信号,通过一个电阻与电源VCC相连,固定在高电平。作用:上拉是对器件注入电流;灌电流;当一个接有上拉电阻的IO端口设置为输入状态时,它的常态为高电平

2023-04-21 09:49:34 6887

6887 什么是上拉电阻?上拉电阻和下拉电阻都是电阻元器件,所谓上拉电阻就是接电源正极,下拉的就是接负极或地。上拉就是将不确定的信号通过一个电阻钳位在高电平,电阻同时起限流作用。下拉同理,也是将不确定的信号通过一个电阻钳位在低电平。那么,上拉电阻和下拉电阻的用处和区别分别又是什么呢?

2023-05-26 10:16:01 1912

1912

电阻在电路中起限制电流的作用,而上拉电阻和下拉电阻是经常提到也是经常用到的电阻。在每个系统的设计中都用到了大量的上拉电阻和下拉电阻,这两者统称为“拉电阻”,最基本的作用是:将状态不确定的信号线通过

2023-06-07 15:20:05 1174

1174

0电阻 上拉电阻 下拉电阻

2012-08-06 13:38:12

上拉和下拉是指GPIO输出高电位(上拉)还是低电位(下拉)。上拉就是输入高电平,然后接一个上拉电阻(起保护作用),知道上拉就表示该端口在默认情况下输入为高电平。下拉就相反了,指输入低电平,然后接一个

2019-05-21 06:21:09

GPIO上有上拉电阻吗?

如果不是,那么当您释放按钮时,GPIO 基本上只是浮动的,可以是任何值。

要么从 GPIO 上拉 10K 到 3.3V,要么将 pinMode 更改为 INPUT_PULLUP。后者将使用大约 36K 的内部上拉电阻,只要到按钮的引线相当短就可以了

2023-05-22 06:54:06

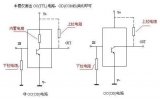

”经常弄不清什么是开漏什么是推挽、IO输入输出电路原理。本文的目地是让大家清楚GPIO的几种配置,GPIO内部结构通常是什么样,上拉、下拉电阻的作用,拉电流、灌电流是什么有助于遇到问题时进行硬件分析,而

2022-01-25 06:25:34

按下时,由于干扰,可能高也可能是低信号输入。根据实际需要,为保证WK_UP不被按下时,STM32能够确定检测到IO口是低电平,所以设置接入下拉电阻。2、上拉电阻和下拉电阻上拉电阻...

2021-08-18 06:27:20

STM32F4中GPIO_PuPd寄存器设置上拉与下拉问题首先 上下拉 是给IO一个默认的状态 比如控制EN的话,那么高有效的我们就下拉,低有效的话我们就上拉而 很多IO 由于CMOS工艺问题会出

2021-08-23 07:51:17

GPIO结构图理解好,那么关于GPIO的各种应用模式将非常清楚。图中最右端I/O端口就是STM32芯片的引脚,其它部分都在STM32芯片内部。上图中我们将每部分都用红色数字标号了,按照顺序我们逐一讲解

2017-11-17 14:09:40

一、STM32外部中断1、STM32外部中断结构图 如上图所示:主要包括四个环节,GPIO、AFIO、EXTI、NVIC。以STM32F103VE(100脚)为例说明硬件模块的数量:GPIO

2021-08-17 08:44:23

结构图的上半部分为输入模式结构。 接下来就遇到了两个开关和电阻,与 VDD相连的为上拉电阻,与VSS相连的为下拉电阻。再连接到施密特触发器就把电压信号转化为 0、1的数字信号存储在输入数据寄存器

2019-05-21 08:16:16

(internal)本身包含了对应的上拉电阻的话,此时会去关闭或打开对应的上拉电阻。如果GPIO硬件IC内部没有对应的上拉电阻的话,那么你的硬件电路中,必须自己提供对应的外部(external)的上拉电阻

2018-04-16 13:23:47

引脚也必须接上拉 (对于低电平有效)或下拉 (对于于高电平有效)防化误中断。3,上拉就是通过一个电阻接到高电平:下拉就是通过一个电阻接到参考地(低电平)。在数字电路中不用的输入脚都要接固定电平,迎过

2017-11-16 17:14:38

引脚也必须接上拉 (对于低电平有效)或下拉 (对于于高电平有效)防化误中断。3,上拉就是通过一个电阻接到高电平:下拉就是通过一个电阻接到参考地(低电平)。在数字电路中不用的输入脚都要接固定电平,迎过1k

2017-08-28 09:27:18

同时起限流作用!下拉同理! l 上拉是对器件注入电流,下拉是输出电流 l 弱强只是上拉电阻的阻值不同,没有什么严格区分 l 对于非集电极(或漏极)开路输出型电路(如普通门电路)提升电流和电压的能力

2011-09-19 08:55:51

(上拉下拉电阻)所谓上拉电阻就是:将一个不确定信号(高或低电平),通过一个电阻与电源VCC相连,固定在高电平;同理下拉电阻就是:将一个不确定信号(高或低电平),通过一个电阻与地GND相连,固定

2022-01-14 08:44:01

上拉电阻与下拉电阻上拉(Pull Up )或下拉(Pull Down)电阻(两者统称为“拉电阻”)最基本的作用是:将状态不确定的信号线通过一个电阻将其箝位至高电平(上拉)或低电平(下拉),无论它

2021-12-13 07:08:22

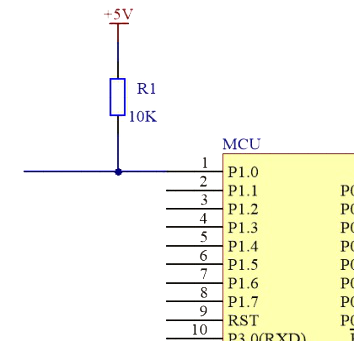

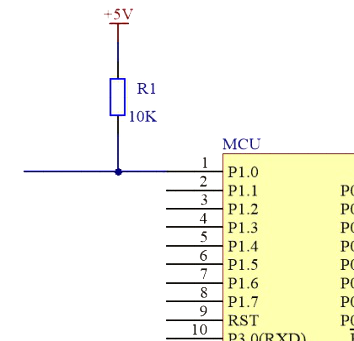

上拉电阻与下拉电阻用在什么场合? 答:用在数字电路中,存在高低电平的场合。 上拉电阻与下拉电阻怎么接线? 上拉电阻:电阻一端接VCC,一端接逻辑电平接入引脚(如单片机引脚) 下拉电阻:电阻一端接GND,一端接逻辑电平接入引脚(如单片机引脚)

2019-05-20 13:48:41

概述:上拉电阻:将一个不确定的信号(高或低电平),通过一个电阻与电源VCC相连,固定在高电平。下拉电阻:将一个不确定的信号(高或低电平),通过一个电阻与地GND相连,固定在低电平。上、下拉电阻的作用

2021-12-13 06:05:27

上拉电阻与下拉电阻是如何定义的?拉电阻的作用有哪些?上拉电阻的应用原则有哪些?

2021-10-14 07:20:37

一句话:上拉电阻的目的是为了保证GPIO无信号输入时输入端的电平为高电平,相反的,下拉电阻是为了保证GPIO无信号输入时输入端的电平为低电平。不懂的具体可以看下面一、概念上拉电阻就是:将一个不确定

2022-01-14 09:16:39

上拉电阻就是把不确空的信号通过一个电阻箝位在高电平,此电阻还起到限流的作用。同理下拉电阻是把不确定的信号箝位在低电平。上拉电阻是指器件的输入电流,而下拉电阻指的是输出电流。

2018-09-10 17:43:34

经常看到芯片设计手册时,芯片外围会有上拉或者下拉电阻还有一些无源器件。如何选择正确值的上拉电阻和下拉电阻?上拉电阻和下拉电阻是如何确定?还是在选择此类电阻的时候,有个特定的范围?对上拉电阻和下拉电阻

2021-11-12 07:28:55

上拉电阻和下拉电阻的区别及案列分析上拉电阻在一个信号未过来之前、默认(保证)该电位的电平信号是高电平,在信号过来后如果是高电平、那么保持高电平。如果过来低电平信号、那么输出的信号就会变成低电平。改图

2022-01-14 06:30:35

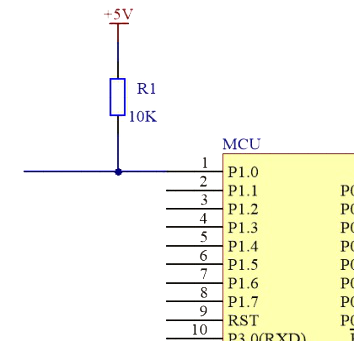

上拉电阻和下拉电阻上拉电阻(Pull-Up)所谓上拉电阻就是用一个电阻将VCC和单片机的IO口直接连接起来,目的是当IO在没有输出一个确定信号时将IO的电位钳在一个高电平上。上拉电阻作用如下:1.当

2022-01-25 07:23:49

都用同一个单片机来驱动,必须设置初始状态.防止直通! 2、定义: l 上拉就是将不确定的信号通过一个电阻嵌位在高电平!电阻同时起限流作用!下拉同理! l 上拉是对器件注入电流,下拉是输出电流 l 弱强

2008-05-22 08:46:35

上、下拉电阻一、定义1、上拉就是将不确定的信号通过一个电阻嵌位在高电平!“电阻同时起限流作用”!下拉同理!2、上拉是对器件注入电流,下拉是输出电流3、弱强只是上拉电阻的阻值不同,没有什么严格区分4

2015-06-24 11:24:37

上拉电阻和下拉电阻

2022-01-14 08:02:00

一、定义: 1、上拉就是将不确定的信号通过一个电阻嵌位在高电平!电阻同时起限流作用!下拉同理 2、上拉是对器件注入电流,下拉是输出电流 3、弱强只是的阻值不同,没有什么严格区分 4、对于

2018-10-19 16:30:19

。 7、长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。 上拉电阻阻值的选择原则包括: 1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。 2

2019-06-27 05:55:08

上拉电阻的作用

2021-01-29 07:18:20

确定的信号通过一个电阻嵌位在高电平!电阻同时起限流作用!下拉同理! * 上拉是对器件注入电流,下拉是输出电流 * 弱强只是上拉电阻的阻值不同,没有什么严格区分 * 对于非集电极(或漏极)开路输出型电路(如普通

2014-05-12 08:24:37

上拉、下拉电阻的作用

2012-08-20 14:53:59

什么是上拉和下拉电路?上拉与下拉电路的实际作用是什么?上/下拉电阻阻值的选择原则是什么?

2021-09-29 07:14:38

电阻在电路中起限制电流的作用。上拉电阻和下拉电阻是经常提到也是经常用到的电阻。在每个系统的设计中都用到了大量的上拉电阻和下拉电阻。在上拉电阻和下拉电阻的电路中,经常有的疑问是:上拉电阻为何能上拉

2021-08-06 08:56:02

一、定义 1、上拉就是将不确定的信号通过一个电阻嵌位在高电平!“电阻同时起限流作用”!下拉同理! 2、上拉是对器件注入电流,下拉是输出电流 3、弱强只是上拉电阻的阻值不同,没有什么严格区分

2020-12-14 17:21:30

输出端,好像往反向器里灌电流一样,因此习惯上称它为“灌电流”输出。 在数字电路中我们经常可以看到上、下拉电阻。一、定义:1、上拉就是将不确定的信号通过一个电阻嵌位在高电平!电阻同时起限流作用!下拉同理

2014-11-17 10:24:15

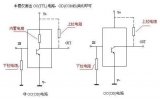

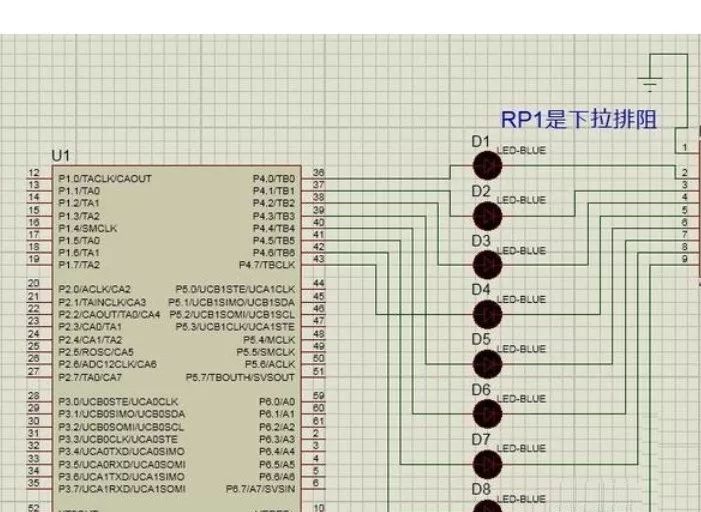

的输出接口就不要接东西了。 举例: 图中上下两个电阻分别为下拉电阻和上拉电阻,上拉就是将A点的电位拉高,下拉就是将A点的电位拉低,图中的12k有些是没有画出来的,或者是没有的. 他们的作用就是在电路驱动器关闭时,给该节点一个固定的电平

2018-06-28 06:21:54

(本博客所有关于32的文章都是基于stm32f103c8t6)GPIO初识——理论讲解GPIO的工作模式四种输入模式上拉输入:若GPIO引脚配置为上拉输入模式,在默认情况下(GPIO引脚无输入

2022-02-24 07:46:28

AT32F4xx系列GPIO各种模式上拉/下拉电阻配置说明AT32F4xx 系列GPIO 的各种模式内部上/下拉电阻配置是否有效?

2023-10-23 06:13:37

芯片数据手册中有说明支持在配置为输入时可以选择内部上拉或者下拉,CNFy 位配置0b10时,配置为带有上下拉的输入模式,那么怎么配置上拉还是下拉? 谢谢。另外从GPIO的功能框图上看,上下拉电阻放在输入驱动模块的内部,这样就必须使用外部上拉电阻才能实现开漏?不是浪费了内置电阻吗

2022-05-18 07:24:33

上、下拉电阻的作用电平兼容板内或板间器件信号电平特性各不相同,出于兼容性的考虑,须加上拉电阻以保证兼容性。当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于COMS电路的最低高电平(一般

2019-07-27 08:38:52

同一个单片机来驱动,必须设置初始状态.防止直通! 2、定义: l 上拉就是将不确定的信号通过一个电阻嵌位在高电平!电阻同时起限流作用!下拉同理! l 上拉是对器件注入电流,下拉是输出电流 l 弱强只是

2016-09-23 17:19:31

如果在IC芯片输入端串联一个电阻R,起到上拉作用,R电阻值越大则电阻电压UR就越大,IC就获得低电平。R电阻值越小则电阻电压UR就越小,IC就获得高电平。这样的接法不就起到上下拉的作用?为什么都说上拉电阻接Vcc端,下拉电阻接地?所谓的上拉是指UR变大还是IC输入电压变大?

2018-04-13 11:19:32

上拉、下拉以及对应上拉电阻和下拉电阻的作用原理一、什么是上拉和下拉电路上拉(Pull Up )或下拉(Pull Down)电阻两者统称为拉电阻上拉就是单片机的IO口串联一个电阻到VDD;下拉就是

2021-07-26 06:46:17

确定的信号通过一个电阻钳位在高电平,电阻同时起限流作用,下拉同理。上拉是对器件注入电流,下拉是输出电流;弱强只是上拉电阻的阻值不同,没有什么严格区分;对于非集电极(或漏极)开路输出型电路(如普通门电路

2023-05-18 17:30:56

什么场合?答:用在数字电路中,存在高低电平的场合。上拉电阻与下拉电阻怎么接线?上拉电阻:电阻一端接VCC,一端接逻辑电平接入引脚(如单片机引脚)下拉电阻:电阻一端接GND,一端接逻辑电平接入引脚(如

2019-03-25 07:00:00

外界的电磁干扰。7、长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。8、在数字电路中不用的输入脚都要接固定电平,通过1k电阻接高电平或接地。四、上拉电阻阻值选择原则

2018-11-30 11:55:14

判断上下拉电阻时,只需要看按键按下之前,两端是高电平还是低电平。例如:R1这个电阻,一端接VCC,在按键按下之前两端是高电平,所以它就是上拉电阻,是为了检测低电平输入。R2这个电阻,一端接GND,在按键按下之前,两端是低电平,所以它就是下拉电阻,是为了检测高电平输入。...

2022-01-14 08:31:27

上拉就是将不确定的信号通过一个电阻钳位在高电平,电阻同时起限流作用。下拉同理,也是将不确定的信号通过一个电阻钳位在低电平。

2020-08-14 06:35:49

大家好,我使用的是DSPIC33 FJ256MC710A DSP。我无法理解如何选择IO引脚上的上拉或下拉电阻。我查阅了数据表,它指出:可选择的开放漏极、上拉和下拉。在输入输出引脚的参考指南中,我

2019-08-07 14:05:23

上拉(Pull Up )或下拉(Pull Down)电阻(两者统称为“拉电阻”)最基本的作用是:将状态不确定的信号线通过一个电阻将其箝位至高电平(上拉)或低电平(下拉),无论它的具体用法如何,这个

2021-12-13 06:10:03

功能的芯片(如单片机、FPGA等)都会集成上拉或下拉电阻,用户可根据需要选择是否打开,STM32单片机GPIO模式即包含上拉或下拉,如下图所示(来自ST数据手册):根据拉电阻的阻值大小,我们还可以分为强

2020-08-19 09:00:00

电阻在电路中起限制电流的作用。上拉电阻和下拉电阻是经常提到也是经常用到的电阻。在每个系统的设计中都用到了大量的上拉电阻和下拉电阻。在上拉电阻和下拉电阻的电路中,经常有的疑问是:上拉电阻为何能上拉

2019-10-11 08:30:00

上拉电阻和下拉电阻上下拉电阻的出发点在正常工作或单一故障状态下,管脚均不应出现不定状态从功耗角度考虑,在长时间的管脚等待状态下,管脚端口的电阻不应消耗太多电流上下拉的选择从抗扰角度出发,信号端口优选

2022-01-14 07:42:58

什么是上拉电阻?上拉就是将不确定的信号通过一个电阻钳位在高电平,电阻同时起限流作用。下拉同理,也是将不确定的信号通过一个电阻钳位在低电平。为什么需要上拉电阻?一般作单键触发使用时,如果IC本身没有内

2021-08-12 13:35:38

引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。8、有些总线协议会将一些信号释放为高阻态,但是实际上电路的状态应该事确定的0 或1,所以上拉电阻可以提供一个确定的状态。9、有时候雷击时候

2014-08-21 09:56:08

STM32F207参考手的中GPIO框图讲解GPIO功能。01、I/O接口电路带FT的是说明可以容忍5V电压的,I/O电路框图1.1、普通输入普通输入模式下,上拉和下拉电阻(微弱)的存在,共分3种模式浮空输入,不使能上拉电阻,不使能下拉电阻上

2021-08-04 06:14:12

模式总结输入模式输出模式M4的IO口基本结构特性输入通道保护二极管: 起到了保护的作用标准3.3V可以容忍5V的输入上拉和下拉电阻 : 在M4框图中上拉和下拉放到了外部,这样输入和输出都可以使用施密特触发器当使用模拟输入时候 施密特触发器处于关闭状态输入值不是模拟量时候,施密特

2022-02-28 06:04:54

前言:在一张原理图中无论时上拉还是下拉都是非常普遍的,转载此文章,可以很快的理解上拉电阻与下拉电阻的原理与作用。如果还没有理解,可以参考上拉与下拉的原理与应用2者共同的作用是:避免电压的“悬浮

2022-01-14 08:28:26

本帖最后由 科炬电子 于 2017-5-22 18:49 编辑

上拉电阻就是把不确空的信号通过一个电阻箝位在高电平,此电阻还起到限流的作用。同理下拉电阻是把不确定的信号箝位在低电平。上拉

2017-05-22 18:49:54

呢?单片机在读准双向口的端口时,先应给端口锁存器赋1,目的是使FET关断,不至于因片内FET导通使端口钳制在低电平。上下拉一般选10k!芯片的上拉/下拉电阻的作用最常见的用途是,假如有一个三态的门带下

2015-06-26 14:26:17

高电平是不可能的,如果想输出一个高电平,则必须在NPN的集电极上面来一个上拉电阻。这时又体现出上拉的一个作用:就是将不确定的信号通过一个电阻嵌位(保持)在一个高电平上,下拉同理。这里对于OC门还有一个

2020-07-30 08:30:00

,CyU3PGpioSetValue,在配置参数里CyU3PGpioSimpleConfig_t的结构里,没有看到此io口是否可以配置内部上拉或下拉电阻。请为cx3的io口没有内部上拉电阻或下拉电阻吗?我们设计电路时必须自己考虑外部上拉下拉来提升驱动能力吗?

2024-02-28 06:25:22

拉,但是对TCK没有特别建议。然而,在STM32F10xxx中JTCK引脚有下拉电阻。 有了嵌入的上拉和下拉电阻,就不需要加外部电阻了可是我看原子的板子是有加的~~~

2019-04-23 19:01:31

stm32普通的I/O接口是否需要接上拉或下拉电阻? 接了会更稳定一些吗?

2019-04-24 01:44:05

什么是上拉电阻,什么是下拉电阻?它们的作用是什么?

上拉电阻一般是一端接电源,一端接芯片管脚的电路中的电阻,下拉电阻一般是指一端接芯片管

2009-06-28 10:13:44 111580

111580

CHR-O1湿敏电阻结构图

2009-11-30 09:52:30 2193

2193 电阻式传感器工作原理及结构图解分析

电阻式传感器种类繁多,应用广泛,其基本原

2009-12-02 09:50:58 30778

30778 上拉电阻、下拉电阻、限流电阻的原理和作用

2016-11-11 18:42:28 55

55 上拉电阻和下拉电阻的作用及选择

2016-12-15 18:39:07 25

25 本文首先介绍了下拉电阻的作用,其次介绍了下拉电阻的原理以及典型电路,最后阐述了下拉电阻的选择。

2018-08-22 17:51:37 63736

63736 下文将根据STM32F207参考手的中GPIO框图讲解GPIO功能。 01I/O接口电路 带FT的是说明可以容忍5V电压的,I/O电路框图 1.1、普通输入 普通输入模式下,上拉和下拉电阻(微弱

2021-02-20 14:23:11 4105

4105

STM32中的GPIO 以STM32中的GPIO为例,如上图是GPIO的结构图。 从上图中标号2处可以看到,上拉和下拉电阻上都有一个开关,通过配置上下拉电阻开关,可以控制引脚的默认电平,这里有三种

2021-11-02 10:11:05 11973

11973

STM32学习(1)-资料查找,STM32简介,STM32选型以及芯片内部结构图

2021-11-26 19:51:05 74

74 然”经常弄不清什么是开漏什么是推挽、IO输入输出电路原理。本文的目地是让大家清楚GPIO的几种配置,GPIO内部结构通常是什么样,上拉、下拉电阻的作用,拉电 流、灌电流是什么有助于遇到问题时进行硬件分析,而不是讲怎么配置寄存器实现引脚功能。先

2021-11-30 21:06:04 12

12 关于STM32 GPIO的配置等问题一、GPIO的基本结构图示二、模式直接上图:图表数据解析:三、配置等问题问题一、GPIO的基本结构图示提示:图片来自STM32中文参考手册P176 STM32

2022-01-13 16:22:07 3

3 目录一、上拉电阻1. 应用场景2. 作用二、下拉电阻1. 应用场景2. 作用三、知乎上的一篇漫画注:下文中所说的0、1电平,并不是真正意义的电平为0、电平为1!0、1电平只代表一种逻辑状态,即低电平

2022-01-14 14:05:35 2

2 STM32的GPIO的输入,输出与开漏,推挽,上拉,下拉的关系

2022-01-14 14:45:43 24

24 电阻在电路中起限制电流的作用。上拉电阻和下拉电阻是经常提到也是经常用到的电阻。在每个系统的设计中都用到了大量的上拉电阻和下拉电阻。

2023-03-17 15:51:07 2538

2538

什么是上拉电阻?上拉电阻和下拉电阻都是电阻元器件,所谓上拉电阻就是接电源正极,下拉的就是接负极或地。上拉就是将不确定的信号通过一个电阻钳位在高电平,电阻同时起限流作用。下拉同理,也是将不确定的信号通过一个电阻钳位在低电平。

2023-05-31 13:57:02 1293

1293

电阻在电路中起限制电流的作用,而上拉电阻和下拉电阻是经常提到也是经常用到的电阻。在每个系统的设计中都用到了大量的上拉电阻和下拉电阻,这两者统称为“拉电阻”,最基本的作用是:将状态不确定的信号线通过

2023-06-10 14:17:53 1950

1950

上拉电阻或下拉电阻是电路板维修技术中的两个专业技术术语,在分析电路板中的电路控制原理时经常会用到上拉电阻或下拉电阻这两个专业技术术语。

2024-02-03 12:26:59 282

282

电子发烧友App

电子发烧友App

评论