【摘 要】 介绍了ITU-TG.723.1标准语音编译码器的算法及其在ADSP-2181芯片上的实现 。软硬件结合实现了语音信号的采样和实时编译码,完全符合ITU-TG.723.1标准的定点算法,通过了ITU-T的所有测试向量。

关键词:语音编译码,DSP,ITU┐TG.723.1

1 引 言

当前,Voice over IP(VoIP)技术正在不断普及,其中使用的低码率语音压缩标准主要有G.723 .1和G.729两种。随着VoIP技术的不断发展,要求产品的集成度与性能进一步提高,利用新一代高性能DSP芯片,实现单片DSP处理多路语音信号,是今后的发展趋势。

G.723.1标准是ITU组织于1996年推出的一种低码率编码算法。主要用于对语音及其它多媒体声音信号的压缩,如可视电话系统、数字传输系统和高质语音压缩系统等。G.723.1标准可在6.3kbps和5.3kbps两种码率下工作。其中,高码率算法具有较高的重建语音质量,而低码率算法的计算复杂度则较低。与一般的低码率语音编码算法一样,G.723.1标准采用线性预测的合成分析法。对激励信号进行量化时,高码率算法采用多脉冲最大似然量化(MP-MLQ),而低码率算法则采用算术码本激励线性预测(ACELP)。

2 算法介绍

语音信号的参数模型是用激励信号激励一个系统模型来模仿气流冲激声道产生的声音。线性预测法基于全极点模型假定,采用时域均方误差最小准则来估计模型参数。分析过程中要提取的参数包括声道系统的LSP参数、自适应码本的延迟和增益,

以及固定码本中脉冲的位置和符号。

G.723.1编码器能对以8kHz采样的话带语音信号进行压缩。为了降低码率,G.723.1采用了较长的帧尺寸,每帧240个样值,即30毫秒帧长。每帧输入信号首先通过一阶高通滤波器滤除直流分量,然后将之分成四个60个样值的子帧,每个子帧独立进行LPC分析。为了提高LPC系数的连续性,采用了长度为180个样值的重叠窗,即同时包含前后两个子帧,这使算法引入60个样值的超前时延,因此算法的总时延为37.5毫秒。LPC系数用线性谱频率(LSF)表示,LSF参数采用预测分裂矢量量化,只对第四子帧进行。为了提高量化感知质量,高通滤波后的语音信号需通过共振峰感知加权滤波器和谐振峰噪声整形滤波器以生成初始目标信号。前者参数由各子帧的未量化LPC系数构成,后者通过对每两子帧进行开环基音周期估计得到,其中基音周期的范围为18到142个样值。LPC合成滤波器、共振峰感知加权滤波器和谐振峰噪声整形滤波器用于系统零输入响应计算和最佳激励估计。G.723.1编码器还包括一个五阶基音预测器,其参数根据开环基音估计值和脉冲响应进行闭环基音搜寻得到。在进行最佳激励估计时,需从初始目标信号中减去系统零输入响应和基音预测器贡献以得到最终目标信号,然后针对高低码率分别采用MP-MLQ和ACELP方法进行量化。其中,LSF参数、基音值和激励参数需传送给解码器。

解码器首先根据得到的LSF参数重建LPC合成滤波器,然后根据基音值和激励参数得到自适应码本激励信号和固定码本激励信号。

2.1 声道模型参数的提取

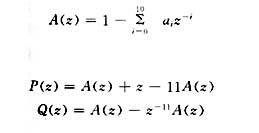

十阶全极点模型系统的传递函数为:

其中,S(z)和U(z)分别是输出信号s(n)和输入信号u(n)的Z变换。因此误差信号为:

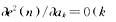

要使均方误差最小,{ak}必定满足 =1,2,...10),由此可得到以

=1,2,...10),由此可得到以 k为变量的方程组:

k为变量的方程组:

其中,R(n)为S(n)的自相关函数值。对于这个Toeplitz矩阵,用Durbin递推算法可方便求解。

因为线谱对参数(LSP)良好的量化特性和内插特性,LPC参数要转换为LSP参数进行传输。

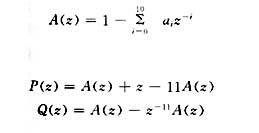

设线性滤波器的逆滤波器为

ωi和θi分别是P(z)和Q(z)的第i个零点。ωi和θi成对出现,反映信号的频谱特性,因此称为线谱对。对P(z)和Q(z)的系数做离散傅立叶变换得到zk=e-jπk/N(k=0,1,2...N)各点的值,搜索极小值点的位置,就是可能的零点位置。

2.2 自适应码本的搜索

开环搜索是基于整帧的整数基音估计。为了提高可靠性,对原始信号进行预处理,用中心削波函数对原始信号进行削波。然后用自相关基音检测法估

计基音Top。闭环搜索是基于子帧的基音细搜索。将LPC合成滤波器、共振峰感知加权滤波器和谐波噪声滤波器一起构成综合滤波器,计算出该综合滤波器的冲激响应。用估算出的开环基音周期和计算所得综合滤波器的冲激响应,通过一个五阶的基音预测器,可计算出闭环基音周期。

2.3 固定码本的搜索

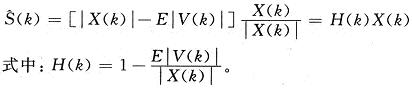

对自适应码本搜索后得到的残差余量信号进行固定码本搜索。

对高码率(6.3kbps)的固定码本搜索采用脉冲最大似然量化法(MP-MLQ)。激励信号可表示为

其中,G为增益因子,δ(n)为单位脉冲响应,{ak}和{mk}分别是单位脉冲响应的符号和位置。M为脉冲的数目,偶数帧取6,奇数帧取5。

编码算法的任务是估计G、{ak}和{mk},使误差信号e〔n〕的均方值最小。

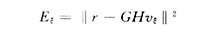

其中,r〔n〕表示目标矢量,自适应码本搜索后得到的残差信号,h〔n〕表示加权合成滤波器的冲激响应。

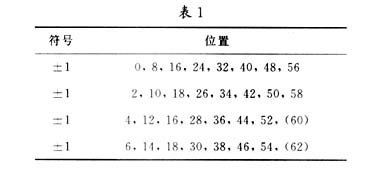

对低码率(5.3kbps)编码器固定码本搜索采用代数码本激励线性预测法(ACELP)。每一子帧中有4个脉冲,它们可能的位置如表1所示。

表1 码本搜索同样是使加权语音信号r〔n〕与加权合成语音信号之间均方误差最小。即:

其中,r表示目标矢量,自适应码本搜索后得到的残差信号,G是码本增益,vξ是代数码本中索引ξ对应的码本,H是加权合成滤波器的截断冲激响应。

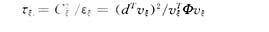

要求最佳码本,即要搜索使τξ最大的ξ,

其中,τξ是一个中间参数,d是r〔n〕和h〔n〕之间的相关值,Φ是冲激响应的协方差矩阵。C、ε的计算:

对奇位置的码矢量,先把偶脉冲移一个样本位置,然后用上式计算。

3 算法实现

3.1 硬件设计

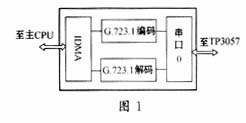

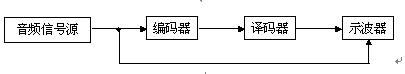

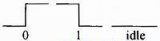

系统框图如图1所示。

模拟的语音信号通过TP3057的A/D转换变为数字信号送入ADSP-2181(采样频率8kHz)。TP3057是美国国家半导体公司生产的A律编/解码器,它包含一个利用A/D和D/A转换结构的A律脉冲编码调制的编解码器/滤波器单片电路和一个串行PCM接口。其中,编码部分还包含一个可调输入增益的放大器、一个有源RC前置滤波器、自动调零电路、一个A率压缩编码器。解码部分包括一个A律解码器和截止频率为3400Hz的低通滤波器。前者从A律压扩的信号中重建模拟信号,后者校正译码器输出的sinx/x响应并滤除高频信号。

ADSP-2181是Analog Devices公司生产的一种性能优越的单片机,适合于高速的数字信号处理。 ADSP-2181除了三个运算单元、数据地址发生器和一个程序序列器,还含有两个串行口、一个16位的内部IDMA口、一个8位的BDMA口、一个可编程定时器、外部中断能力及片内程序和数据存储器。片内集成了80k字节的存储器,包括16k长度为24bit的程序存储器和16k长度为16bit的数据存储器。

利用IDMA口的自动接受发送功能,可以方便地实现ADSP-2181与主CPU间的数据交互。PC机通过IMDA口将程序装载入ADSP-2181内部存储器中。在ADSP-2181全速执行时,主机可以查询其状态,读取压缩后的码流,也可送入待解码的数据。

3.2 软件设计

软件设计包括三个模块:接口模块、编码模块和解码模块。

接口模块实现ADSP-2181与主CPU之间的数据交换。该模块包括DSP的主控程序和数据传输两部分。DSP的主控程序负责将采集到的语音数据分帧,送入编码器,并将接受到的码流分类后送入解码模块。数据传输部分负责采集数据和与主CPU的数据交换。

DSP程序根据ITU-TG.723.1标准定点算法,分为初始化(G723—Init)、编码(G723—Incode)、解码(G723—Decode)三个模块。

G723—Icode对包含240个采样点的一帧信号进行编码,返回12个或10个字长的二进制数据。

输入数据由串口得到,放在数组G723—Enc—Inp中,返回值放在数组G723—Enc—Out中,对于6.3kbps长工为12个字,对于5.3kbps长度为10个字。其格式按照G.723.1标准进行封装。

G723—Decode根据接收到的12字或10字打包数据重建240个语音样点。输入数据放在G723

Dec—Inp中,输出放在数组G723—Dec—Out中。

主机程序采用VisualC++编写,通过串口与DSP通信。

3.3 C语言的优化

开发中采用AD公司的集成仿真软件VisualDSP++,但是通常,C编译器能完成整个工作的70%,而30%的进一步优化必须通过手写汇编来实现。

3.3.1 循环展开

使用具有并行能力的DSP开发软件时,一个重要的思想就是充分利用DSP的字长和数目众多的运算单元,尽量把循环体展开。通过增加每次循环中执行的指令数来减少总的循环次数,可使得在同样的时钟周期内能运行更多的指令,提高了循环的效率。

3.3.2 提高寄存器的利用率

DSP芯片内部的运算单元运行效率非常高,但如果寄存器和数据总线之间的数据交换频繁,将使DSP的执行效率大打折扣。因为DSP在进行内存操作时,往往需要若干周期的延迟,如Load指令要有4个周期的延迟,Store指令需要2个周期的延迟。为了减少耗时的内存操作,可以在程序进入循环体之前,将要频繁使用的数据预先放入寄存器,然后反复调用,实践证明这种方法可以提高一部分效率。

4 实验结果

所有代码全部通过了ITU-T测试矢量的测试。

测试结果表明,对于高码率(6.3kbps)所需计算量为24.8MIPS,对于低码率(5.3kbps),所需计算量为21.3MIPS。该实现可以在IP电话、视频会议中得到广泛应用。

参考文献

1 易克初,田斌,付强.语音信号处理.北京:国防工业出版社,2000

2 赵训威,吴善培,张平.G.723.1声码器的DSP实现.电声技术,2001(8):23~27

关键词:语音编译码,DSP,ITU┐TG.723.1

1 引 言

当前,Voice over IP(VoIP)技术正在不断普及,其中使用的低码率语音压缩标准主要有G.723 .1和G.729两种。随着VoIP技术的不断发展,要求产品的集成度与性能进一步提高,利用新一代高性能DSP芯片,实现单片DSP处理多路语音信号,是今后的发展趋势。

G.723.1标准是ITU组织于1996年推出的一种低码率编码算法。主要用于对语音及其它多媒体声音信号的压缩,如可视电话系统、数字传输系统和高质语音压缩系统等。G.723.1标准可在6.3kbps和5.3kbps两种码率下工作。其中,高码率算法具有较高的重建语音质量,而低码率算法的计算复杂度则较低。与一般的低码率语音编码算法一样,G.723.1标准采用线性预测的合成分析法。对激励信号进行量化时,高码率算法采用多脉冲最大似然量化(MP-MLQ),而低码率算法则采用算术码本激励线性预测(ACELP)。

2 算法介绍

语音信号的参数模型是用激励信号激励一个系统模型来模仿气流冲激声道产生的声音。线性预测法基于全极点模型假定,采用时域均方误差最小准则来估计模型参数。分析过程中要提取的参数包括声道系统的LSP参数、自适应码本的延迟和增益,

以及固定码本中脉冲的位置和符号。

G.723.1编码器能对以8kHz采样的话带语音信号进行压缩。为了降低码率,G.723.1采用了较长的帧尺寸,每帧240个样值,即30毫秒帧长。每帧输入信号首先通过一阶高通滤波器滤除直流分量,然后将之分成四个60个样值的子帧,每个子帧独立进行LPC分析。为了提高LPC系数的连续性,采用了长度为180个样值的重叠窗,即同时包含前后两个子帧,这使算法引入60个样值的超前时延,因此算法的总时延为37.5毫秒。LPC系数用线性谱频率(LSF)表示,LSF参数采用预测分裂矢量量化,只对第四子帧进行。为了提高量化感知质量,高通滤波后的语音信号需通过共振峰感知加权滤波器和谐振峰噪声整形滤波器以生成初始目标信号。前者参数由各子帧的未量化LPC系数构成,后者通过对每两子帧进行开环基音周期估计得到,其中基音周期的范围为18到142个样值。LPC合成滤波器、共振峰感知加权滤波器和谐振峰噪声整形滤波器用于系统零输入响应计算和最佳激励估计。G.723.1编码器还包括一个五阶基音预测器,其参数根据开环基音估计值和脉冲响应进行闭环基音搜寻得到。在进行最佳激励估计时,需从初始目标信号中减去系统零输入响应和基音预测器贡献以得到最终目标信号,然后针对高低码率分别采用MP-MLQ和ACELP方法进行量化。其中,LSF参数、基音值和激励参数需传送给解码器。

解码器首先根据得到的LSF参数重建LPC合成滤波器,然后根据基音值和激励参数得到自适应码本激励信号和固定码本激励信号。

2.1 声道模型参数的提取

十阶全极点模型系统的传递函数为:

其中,S(z)和U(z)分别是输出信号s(n)和输入信号u(n)的Z变换。因此误差信号为:

要使均方误差最小,{ak}必定满足

其中,R(n)为S(n)的自相关函数值。对于这个Toeplitz矩阵,用Durbin递推算法可方便求解。

因为线谱对参数(LSP)良好的量化特性和内插特性,LPC参数要转换为LSP参数进行传输。

设线性滤波器的逆滤波器为

ωi和θi分别是P(z)和Q(z)的第i个零点。ωi和θi成对出现,反映信号的频谱特性,因此称为线谱对。对P(z)和Q(z)的系数做离散傅立叶变换得到zk=e-jπk/N(k=0,1,2...N)各点的值,搜索极小值点的位置,就是可能的零点位置。

2.2 自适应码本的搜索

开环搜索是基于整帧的整数基音估计。为了提高可靠性,对原始信号进行预处理,用中心削波函数对原始信号进行削波。然后用自相关基音检测法估

计基音Top。闭环搜索是基于子帧的基音细搜索。将LPC合成滤波器、共振峰感知加权滤波器和谐波噪声滤波器一起构成综合滤波器,计算出该综合滤波器的冲激响应。用估算出的开环基音周期和计算所得综合滤波器的冲激响应,通过一个五阶的基音预测器,可计算出闭环基音周期。

2.3 固定码本的搜索

对自适应码本搜索后得到的残差余量信号进行固定码本搜索。

对高码率(6.3kbps)的固定码本搜索采用脉冲最大似然量化法(MP-MLQ)。激励信号可表示为

其中,G为增益因子,δ(n)为单位脉冲响应,{ak}和{mk}分别是单位脉冲响应的符号和位置。M为脉冲的数目,偶数帧取6,奇数帧取5。

编码算法的任务是估计G、{ak}和{mk},使误差信号e〔n〕的均方值最小。

其中,r〔n〕表示目标矢量,自适应码本搜索后得到的残差信号,h〔n〕表示加权合成滤波器的冲激响应。

对低码率(5.3kbps)编码器固定码本搜索采用代数码本激励线性预测法(ACELP)。每一子帧中有4个脉冲,它们可能的位置如表1所示。

表1 码本搜索同样是使加权语音信号r〔n〕与加权合成语音信号之间均方误差最小。即:

其中,r表示目标矢量,自适应码本搜索后得到的残差信号,G是码本增益,vξ是代数码本中索引ξ对应的码本,H是加权合成滤波器的截断冲激响应。

要求最佳码本,即要搜索使τξ最大的ξ,

其中,τξ是一个中间参数,d是r〔n〕和h〔n〕之间的相关值,Φ是冲激响应的协方差矩阵。C、ε的计算:

对奇位置的码矢量,先把偶脉冲移一个样本位置,然后用上式计算。

3 算法实现

3.1 硬件设计

系统框图如图1所示。

模拟的语音信号通过TP3057的A/D转换变为数字信号送入ADSP-2181(采样频率8kHz)。TP3057是美国国家半导体公司生产的A律编/解码器,它包含一个利用A/D和D/A转换结构的A律脉冲编码调制的编解码器/滤波器单片电路和一个串行PCM接口。其中,编码部分还包含一个可调输入增益的放大器、一个有源RC前置滤波器、自动调零电路、一个A率压缩编码器。解码部分包括一个A律解码器和截止频率为3400Hz的低通滤波器。前者从A律压扩的信号中重建模拟信号,后者校正译码器输出的sinx/x响应并滤除高频信号。

ADSP-2181是Analog Devices公司生产的一种性能优越的单片机,适合于高速的数字信号处理。 ADSP-2181除了三个运算单元、数据地址发生器和一个程序序列器,还含有两个串行口、一个16位的内部IDMA口、一个8位的BDMA口、一个可编程定时器、外部中断能力及片内程序和数据存储器。片内集成了80k字节的存储器,包括16k长度为24bit的程序存储器和16k长度为16bit的数据存储器。

利用IDMA口的自动接受发送功能,可以方便地实现ADSP-2181与主CPU间的数据交互。PC机通过IMDA口将程序装载入ADSP-2181内部存储器中。在ADSP-2181全速执行时,主机可以查询其状态,读取压缩后的码流,也可送入待解码的数据。

3.2 软件设计

软件设计包括三个模块:接口模块、编码模块和解码模块。

接口模块实现ADSP-2181与主CPU之间的数据交换。该模块包括DSP的主控程序和数据传输两部分。DSP的主控程序负责将采集到的语音数据分帧,送入编码器,并将接受到的码流分类后送入解码模块。数据传输部分负责采集数据和与主CPU的数据交换。

DSP程序根据ITU-TG.723.1标准定点算法,分为初始化(G723—Init)、编码(G723—Incode)、解码(G723—Decode)三个模块。

G723—Icode对包含240个采样点的一帧信号进行编码,返回12个或10个字长的二进制数据。

输入数据由串口得到,放在数组G723—Enc—Inp中,返回值放在数组G723—Enc—Out中,对于6.3kbps长工为12个字,对于5.3kbps长度为10个字。其格式按照G.723.1标准进行封装。

G723—Decode根据接收到的12字或10字打包数据重建240个语音样点。输入数据放在G723

Dec—Inp中,输出放在数组G723—Dec—Out中。

主机程序采用VisualC++编写,通过串口与DSP通信。

3.3 C语言的优化

开发中采用AD公司的集成仿真软件VisualDSP++,但是通常,C编译器能完成整个工作的70%,而30%的进一步优化必须通过手写汇编来实现。

3.3.1 循环展开

使用具有并行能力的DSP开发软件时,一个重要的思想就是充分利用DSP的字长和数目众多的运算单元,尽量把循环体展开。通过增加每次循环中执行的指令数来减少总的循环次数,可使得在同样的时钟周期内能运行更多的指令,提高了循环的效率。

3.3.2 提高寄存器的利用率

DSP芯片内部的运算单元运行效率非常高,但如果寄存器和数据总线之间的数据交换频繁,将使DSP的执行效率大打折扣。因为DSP在进行内存操作时,往往需要若干周期的延迟,如Load指令要有4个周期的延迟,Store指令需要2个周期的延迟。为了减少耗时的内存操作,可以在程序进入循环体之前,将要频繁使用的数据预先放入寄存器,然后反复调用,实践证明这种方法可以提高一部分效率。

4 实验结果

所有代码全部通过了ITU-T测试矢量的测试。

测试结果表明,对于高码率(6.3kbps)所需计算量为24.8MIPS,对于低码率(5.3kbps),所需计算量为21.3MIPS。该实现可以在IP电话、视频会议中得到广泛应用。

参考文献

2 赵训威,吴善培,张平.G.723.1声码器的DSP实现.电声技术,2001(8):23~27

电子发烧友App

电子发烧友App

评论