ADSP-TS201S - TigerSHARC-R Embedded Processor - Analog Devices

2022-11-04 17:22:44

ADSP-TS201SABP-050 245PCS现货

2019-01-07 10:27:12

PCS.预计春节后3月份到货。ADSP-TS201SAPBZ-060 在途400只+公司库存285只=685PCS ADSP-TS201SAPBZ050 2404 PCS ADSP-TS201SABP-050 245 PCS ADSP-TS201SYBPZ050873 PCS

2018-12-21 19:48:14

管脚的处理,主要参考ADI网站中所给出的数据手册。另外TS201支持多片DSP互连,最多可达8片。通过链路口完成片与片之间的通信,电路连接简单。4 外部总线接口技术ADSP-TS201外部总线支持各种

2019-04-12 07:00:11

{:12:}{:12:}{:12:}{:12:}{:12:}报道:ADSP-TS201谁用过

2012-09-19 14:14:35

用于多处理TigerSHARC系统的集群总线通信的详细信号完整性和时序分析。该系统由8个ADSP-TS101S器件,一个主处理器和SDRAM组成,其集群总线运行频率为100MHz。包括仿真结果和物理

2019-08-30 09:24:28

存储器&数据存储器RAM;集成I/O外围设备:串行端口、计时器,主机接口端口(仅限ADSP-2111)。 特征 25 MIPS,40 ns最大指令率;用于程序和数据存储器的独立片上总线;程序

2020-07-17 14:23:24

ADSP-21489有三种启动模式,SPI Slaver;SPI Master;AMI boot;我想知道,这些boot的引导都是MCU片内的吗?

我现在自己做了块板子,只用到了并行

2023-11-30 07:29:39

本人刚接触cpci总线,自己做的背板(两槽),一块插计算机,一块自己做的电路板,出现如下

2008-12-29 18:35:26

KIT LITE EVAL FOR ADSP-TS201S

2023-03-22 19:55:59

EPROM读操作时需插入16个等待周期,并且在最后一个EPROM引导总线周期后有3个等待周期,用做EPROM的断开时间。ADSP-TS201提供BMS引脚用于引导存储器选择,作为Flash的片选信号,实现系统

2008-10-07 11:01:37

链路口传输,每个链路口的传输率达到250 MB/s。整个TigerSHARC芯片的I/O带宽达到1 800 MB/s。选用的实时信号处理板基于标准的CPCI总线,由4片TS101构成共享总线的并行

2019-07-22 06:29:35

交流下ADSP TS201的RS422串口通信,EMIF的SDRAM,没思路啊

2018-10-30 09:57:11

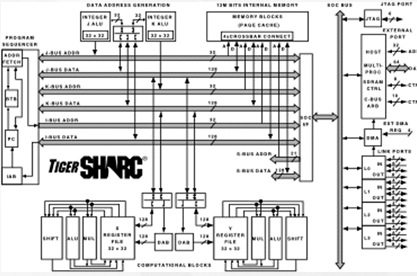

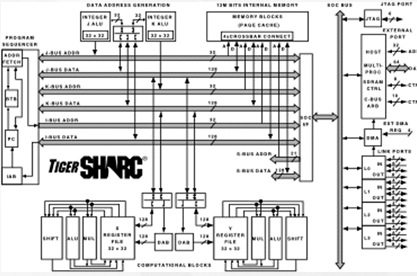

本文主要结合ADI公司的高性能ADSP-TS201的结构特点,讨论了在系统设计的过程中应该重点注意的几个问题和ADSP-TS201的外部接口技术,并给出了其与SDRAM,FPGA的连接实例,对基于TigerSHARC系列DSP的应用设计具有实用的参考价值。

2021-05-27 06:59:04

我想用DSP能够和CPCI总线连接。C6000系列的。不知道有什么方案?不想用PCI2040

2018-06-21 01:00:59

上SDRAM控制器,片上DMA控制器(提供14条DMA通道)。3 DSP并行处理结构设计ADSP-TS201S之间的数据传输通道可选择的方式有如下两种:高速链路口(LINK)方式和高速外部总线口(簇

2019-05-21 05:00:19

外挂Flash的TMS320VC5409引导装载设计,不看肯定后悔

2021-04-27 06:02:41

有没有任何问题与CyPress CYBLY-022001引导加载程序?已创建并编译了引导加载程序和可引导加载项目,并将可引导加载的.HEX文件编程到设备中。重置后,该设备确实等待

2019-09-30 13:28:50

用FX3开发USB摄像头。一般来说,嵌入式系统是在系统启动ROM中启动的,因为它是EZ-USB FX3,我知道它是用FX3引导加载程序启动的,但是我不知道如何使用/安装它。谁能给我简单介绍一下

2019-10-14 10:12:33

什么是DSP流水线协议?如何利用FPGA与ADSP TS201去设计总线接口?

2021-04-28 06:31:06

在雷达信号处理、数字图像处理等领域中,信号处理的实时性至关重要。由于FPGA芯片在大数据量的底层算法处理上的优势及DSP芯片在复杂算法处理上的优势,DSP+FPGA的实时信号处理系统的应用越来越广泛。那么,我们该怎么利用FPGA与ADSP TS201设计总线接口呢?

2019-08-09 06:56:11

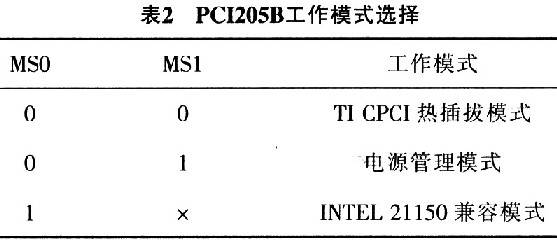

CPCI的特点是什么?CPCI总线与Intel 82551是如何连接的?如何去实现一种基于CPCI总线的以太网卡?

2021-06-03 06:49:06

怎么实现基于CPCI总线的多网口卡设计?

2021-06-02 06:15:08

S32K344引导程序

2023-04-21 06:43:23

我最近开始使用 S32K344 评估板,想知道,你们有 S32K344 设备的统一引导加载程序吗?如果没有,预计什么时候发布?

2023-03-29 08:16:07

如何修改和使用其他MCU的S32K148引导加载程序示例的文档? 如果你能简单地指出我应该注意的关于为 S32K116 开发引导加载程序项目的主题,那就太好了!

2023-03-21 07:12:10

ADSP-TS201的链路口程序应怎么写啊,毫无头绪啊,寄存器也看不懂,ADI公司没找到参考的链路口程序啊

2018-12-10 09:17:06

ADSP-21489有三种启动模式,SPI Slaver;SPI Master;AMI boot;我想知道,这些boot的引导都是MCU片内的吗? 我现在自己做了块板子,只用到了并行

2018-10-18 10:16:39

请问ADSP-21489(100引脚),选用并行 FLASH(比如M29W320)引导,BOOT_CFG1-0 引脚如何配置?

2024-01-15 07:52:48

您好请问ADSP-21489(100引脚),且选用并行 FLASH(比如M29W320)引导,BOOT_CFG1-0 引脚如何配置?

2018-10-31 17:00:51

介绍了一种基于CPCI总线并采用TS201,stratix和GA3816作为系统信号的高速信号处理平台。同时简单介绍了GA3816芯片的一些特点,详细说明了该信号处理系统的结构和功能,给出了系统

2009-03-07 10:01:32 4

4 在机载SAR 的实时成像处理器中,回波信号方位向带宽以及方位向采样率不能很好的满足成像处理的要求,本文选择ADSP-TS201 处理器芯片对回波信号在成像之前对其进行方位向预处

2009-08-05 09:45:52 18

18 ADSP-TS101 是ADI 公司新一代高性能浮点DSP,开始应用在高速数据采集和处理系统中。TS101 外部总线接口可编程,方便和各种总线外设接口。本文结合TS101 与同步FIFO、SDRAM 和FPGA 的接

2009-08-11 09:49:31 28

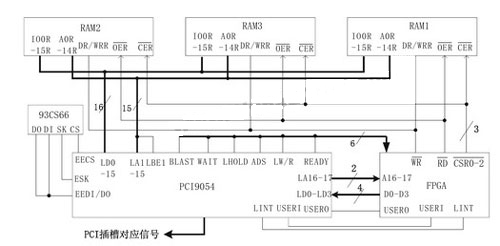

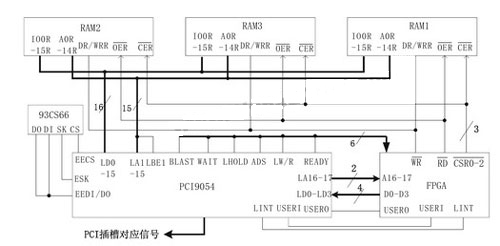

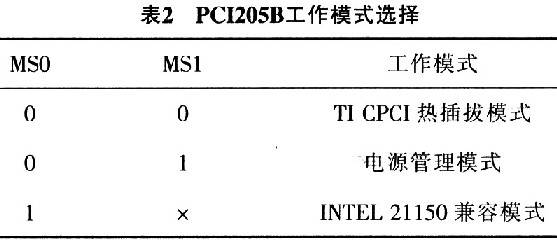

28 CPCI 总线是一种兼容性强、功能全面的计算机总线。文章通过对TI 公司推出的DSP 芯片(TMS320F2812)、FPGA 芯片(EPF10K30A)和CPCI 接口芯片(PCI9054)的功能和特点的深入分析,讨论了

2009-12-19 12:08:10 35

35 为满足复杂信号处理的实时性要求,通过对高速数字信号处理器TS201 的系统结构及其软件开发过程的研究,在TS201 EZ-KIT 板上实现了自适应旁瓣对消(ASLC)处理,结果表明了TS201 数字

2010-01-07 12:01:33 24

24 提出一种基于CPCI总线插槽的4网口卡的设计方案。运用Intel公司的Intel82551以太网控制器和TI公司PCI2050B PCI-PCI桥器件实现4路10/100 Mb/s自适应网口,重点介绍PCI总线桥的设计要点。该扩展

2010-07-10 15:58:28 28

28 描述ADSP-TS201S是TigerSHARC处理器系列中的最新款器件之一。ADI公司的TigerSHARC处理器面向众多依靠多个处理器共同工作来执行计算密集型实时功能的信号处理应用,非常适合

2024-01-26 11:33:09

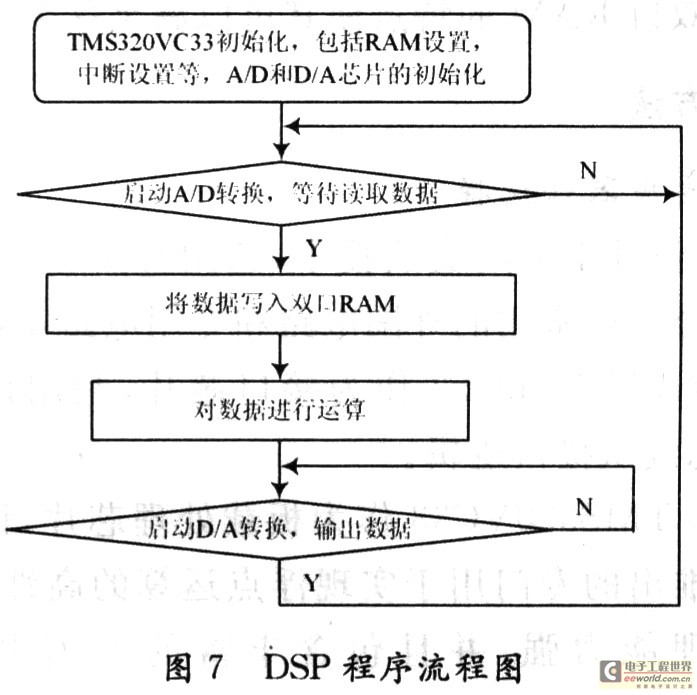

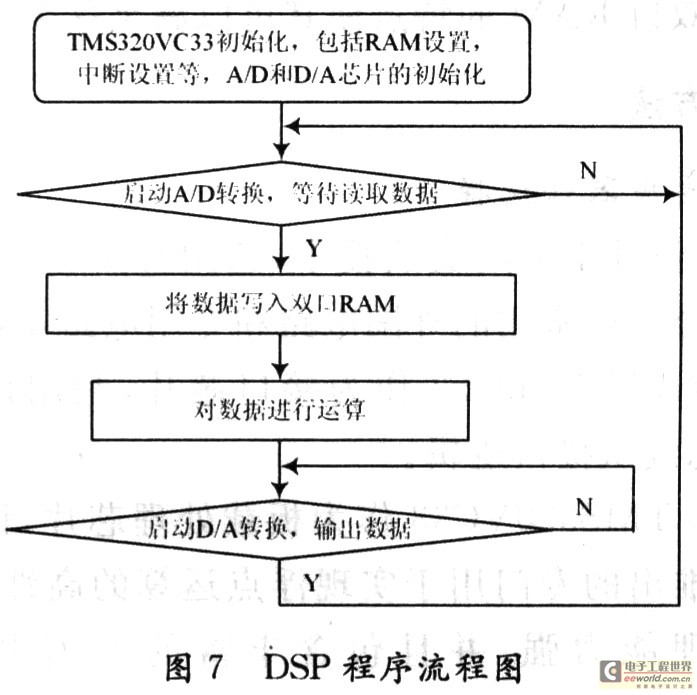

介绍了一种基于ADSP-TS201的无线电测向系统。给出了系统的总体结构和工作原理,研究了MUSIC测向算法及基于零点预处理的波束合成算法,介绍了DSP模块的设计思想和程序流程图。实

2010-11-22 14:52:42 39

39 采用ADSP-TS201S芯片的图像采集处理系统

随着人们对实时信号处理要求的不断提高和大规模集成电路的迅速发展,作为数字信号处理核心和标志的数字

2009-03-30 12:19:18 1162

1162

基于CPCI总线的智能A/D,D/A模块设计

0 引 言

在工业控制领域,为了实现采集和控制功能,经常会使用到A/D,D/A模块。在实际使用中A/D,D/A

2009-11-27 09:35:51 845

845

FPGA与ADSP TS201的总线接口设计

在雷达信号处理、数字图像处理等领域中,信号处理的实时性至关重要。由于FPGA芯片在大数据量的底层算法处理上的优势及DSP芯片在复杂

2009-12-11 10:13:29 2356

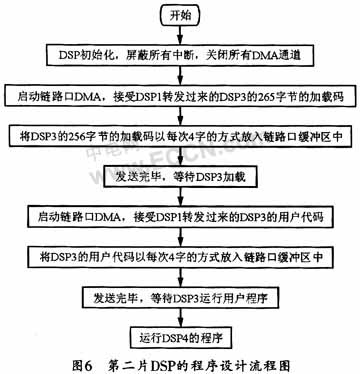

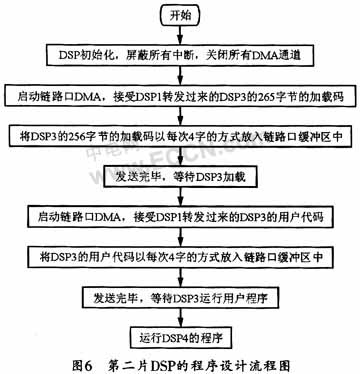

2356 多片TS101S的加载引导设计分析及实现

0 引言ADSP-TS101S数字信号处理器是美国ADI公司推出的TigerSHARC系列中的一款具有极高性能的静态超标量处理器。该处理器已

2010-03-31 10:20:26 1319

1319

以太网(Ethernet)作为应用最广泛的局域网技术异军突起,已经迅速走向工业自动化控制领域的前台。CPCI总线系统插槽有限,设计基于CPCI总线的多网口卡可节省空间,又可以满

2010-09-10 09:56:34 1601

1601

特征: 处理器: 每簇由两个可以达到600MHz的ADSP-TS201 DSP处理器;整板共两簇。每个DSP可以进行3.6 GFLOPS的浮点处理能力(每个板上有4个处理器,就可以进行14.4GFLOPS的处理能力)。每个DSP芯片内有24MbitsRAM哈佛超标量体系结构; 一个用于接口连接和协处

2011-02-25 15:49:54 75

75 本文设计的系统采用PLX公司生产的CPCI协议转换芯片PCI9054,通过Verilog HDL语言在FPGA中产生相应的控制信号,完成对数据的快速读写,从而实现了与CPCI总线的高速数据通信。

2011-07-17 10:47:57 12055

12055

本文在详细阐述处理板的整体结构和DSP与PCI9656的接口电路设计原理的基础上,提出一种ADSPTS201基于桥芯片PCI9656实现与CPCI总线通信的雷达信号处理板的设计方案,实现RocketIO到DSP数据的

2011-09-08 13:56:47 1970

1970

CPCI总线是一个开放式、国际性技术标准,由PCI总线工业计算机制造商组织PICMG(PCI Industrial Computer Manufacturer Group)负责制定和支持。CPCI总线具有严格的标准和规范,保证其具有良好的兼

2011-09-09 11:53:16 21

21 通过在FPGA中编写Verilog HDL语言控制CPCI协议转换芯片,从而实现与CPCI总线之间的高速通信。实验结果证明,该设计方案工作稳定、传输速度快、数据准确,并可扩展到其他需要通过CPCI总线的

2011-12-07 14:22:06 51

51 基于ADSP_TS201S的多DSP并行系统设计

2015-12-29 17:33:04 22

22 TS201的实时图像处理系统链路口通信设计

2017-08-31 15:10:19 10

10 大规模集成电路技术的发展,作为数字信号处理的核心数字信号处理器(DSP)得到了快速的发展和应用。ADSP-TS201DSP是美国模拟器件(ADD公司继TSl01之后推出的一款高性能处理器。此系列DSP性价比很高,兼有FPGA和ASIC信号处理性能和指令集处理器的高

2017-10-20 15:01:32 0

0 摘要:为满足宽带雷达信号处理对处理速度和实时性的要求,提出一种基于4片ADSP-TS201S的DSP并行系统设计。通过分析比较3种ADSP-TS2 01S的并行处理结构,结合实际需求,采用外部总线

2017-10-31 16:41:04 0

0 现代雷达信号处理已成为雷达功能实现的关键,本文根据某型雷达信号处理机的系统需要,对其硬件结构及软件设计做了系统优化。设计了1套以4片 TS201和1片FPGA为核心信号处理板,该系统仅用l副板卡

2017-12-11 02:21:07 1881

1881

模拟器件公司(Analog Devices)推出的下一代TigerSHARC处理器ADSP-TS201,ADSP-TS-202和ADSP-TS203。它的每瓦DSP性能是最高的。

2021-01-11 12:01:00 1803

1803

ADSP-TS201S Iba-DataFile BGA包(09/2003)

2021-04-12 16:09:33 10

10 ADSP-TS201S EZ-KIT精简版ğ超级政府/超级政府手册

2021-04-13 10:25:37 0

0 ADSP-TS201 EZ-KIT Lite电路板设计数据库

2021-04-13 12:13:17 1

1 EE-201:ADSP-TS20x TigerSHARC®处理器片上SDRAM控制器

2021-04-13 18:00:50 6

6 EE-198:ADSP-TS201S TigerSHARC®处理器IBIS文件用户指南

2021-04-13 18:10:30 8

8 ADSP-TS201S:TigerSHARC嵌入式处理器过时数据表

2021-04-15 18:45:56 6

6 EE-205:将代码从ADSP-TS101S TigerSHARC®处理器移植到ADSP-TS201S TigerSHARC处理器的注意事项

2021-04-16 13:54:51 9

9 EE-283:采用ADSP-TS20x TigerSHARC®处理器的外部总线仲裁

2021-04-16 15:34:05 10

10 EE-170:评估ADSP-TS201S TigerSHARC®处理器的功耗

2021-04-21 10:41:30 6

6 EE-182:ADSP-TS201S TigerSHARC®处理器的散热设计

2021-04-22 09:46:01 10

10 设计了一种基于CPCI总线标准的PMC接口载板。载板以FPGA为核心,集成了CPCI接口模块和DPRAM(双口RAM)模块,CPCI接口模

2021-05-05 16:56:00 3055

3055

ADSP-TS201S EZ-KIT Lite评估系统手册(3.0版,2007年1月)

2021-05-13 08:49:32 0

0 ADSP-TS201S EZ-KIT Lite评估系统手册(2.0版,2005年1月)

2021-05-13 19:09:15 0

0 ADSP-TS201 TigerSHARC处理器编程参考

2021-05-18 09:21:19 1

1 ADSP-TS201 TigerSHARC处理器硬件参考

2021-05-18 15:46:19 1

1 ADSP-TS201S EZ-KIT精简版ğ超级政府/超级政府手册

2021-05-24 18:47:02 0

0 EE-218:为ADSP-TS201 TigerSHARC®处理器编写高效浮点FFT

2021-05-26 09:17:20 5

5 ADSP-TS201S EZ-KIT Lite为开发人员提供一种经济有效的方法,可以初步评估ADSP-TS201S TigerSHARC® 处理器和其多处理器能力。 该EZ-KIT Lite包括桌面

2021-06-09 08:59:50 4

4 ADSP-TS201S Iba数据文件BGA包(092003)

2021-06-16 12:02:33 2

2 ADSP-TS201S EZ-KIT Lite®手册

2021-06-17 09:57:57 2

2 ADSP-TS201 EZ-KIT Lite电路板设计数据库

2021-06-17 16:05:58 0

0 EE-201 ADSP-TS20x TigerSHARC®处理器片上SDRAM控制器

2021-06-18 10:47:01 4

4 EE-198 ADSP-TS201S TigerSHARC®处理器IBIS文件用户指南

2021-06-18 11:13:33 2

2 基于CPCI总线的四通道总线通讯模块设计

2021-06-22 16:58:19 16

16 电子发烧友网为你提供ADI(ti)TS201S-EZLITE相关产品参数、数据手册,更有TS201S-EZLITE的引脚图、接线图、封装手册、中文资料、英文资料,TS201S-EZLITE真值表,TS201S-EZLITE管脚等资料,希望可以帮助到广大的电子工程师们。

2021-09-02 12:00:02

产品主要特点

符合CPCI总线标准规范

国产加固机架式CPCI测控平台

标准19寸机架式安装

CPCI模块信号后出线设计

内置厚物科技CPCI-9333或CPCI-9363控制器

内置

2022-04-26 15:07:08 468

468

电子发烧友网站提供《基于ADSP-TS201的着陆雷达恒虚警电路实现.pdf》资料免费下载

2023-10-23 09:59:21 0

0 电子发烧友网站提供《TigerSHARC® ADSP-TS201S处理器的散热设计要点.pdf》资料免费下载

2023-11-29 11:12:01 0

0 产品概述 键石 CPCI6320 是一款高品质的视频播放板,该板基于 CPCI 总线,采用 Sigma Designs 公司的 EM8470 流处理器,支持多种音视频格式,兼容即插即用(PNP)。 在安装和使用键石 CPCI6320 型视频播放板前,建议您先阅读本手册,以便了解如何安装和使用该产品。

2023-12-11 14:40:51 0

0

正在加载...

![]() )等控制信号,从EPROM或FLASH中加载代码。在从引导模式下,TS201作为被动方,不向外部输出控制信号,外部主机或其他设备向TS201的主机或链路口传送要加载的代码,TS201仅启动若干DMA通道,并执行第一个DMA所接收的加载核。

)等控制信号,从EPROM或FLASH中加载代码。在从引导模式下,TS201作为被动方,不向外部输出控制信号,外部主机或其他设备向TS201的主机或链路口传送要加载的代码,TS201仅启动若干DMA通道,并执行第一个DMA所接收的加载核。![]() 引脚的设置,可将DSP的引导过程设置成主引导模式或从引导模式。在DSP复位期间,如果引脚为低电平,则选择主引导模式,DSP从外部EPROM或FLASH中加载程序;若

引脚的设置,可将DSP的引导过程设置成主引导模式或从引导模式。在DSP复位期间,如果引脚为低电平,则选择主引导模式,DSP从外部EPROM或FLASH中加载程序;若![]() 引脚为高电平,则进入从引导模式,DSP为空闲状态,等待主机或链路口加载程序。两种引导模式都有相同的加载过程,具体步骤如下:

引脚为高电平,则进入从引导模式,DSP为空闲状态,等待主机或链路口加载程序。两种引导模式都有相同的加载过程,具体步骤如下:

电子发烧友App

电子发烧友App

评论