本文采用德州仪器公司的16位定点DSP芯片TMS320VC5509A(以下简称5509A),其PGE封装形式只有14根地址总线(A0~A13),最大只能寻址16KB的Flash存储器。若要寻址更大地址空间,就需要控制Flash存储器的高位地址线。常见的解决方案是采用DSP的通用输入输出GPIO(General Purpose Input/Output)引脚来控制Flash的高位地址线,从而实现Flash存储器的分页访问。然而,对于较大容量的Flash存储器,本文介绍了一种基于CPLD快速译码的DSP二次引导方法,利用CPLD的时序严格、译码速度快、可在线编程等特点,在 DSP的外部存储器接口EMIF的CE2空间模拟了一个Flash换页寄存器FPR(Flash Page Register),在上电复位后控制Flash的高位地址线,从而实现Flash的分页访问。

CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件,是从PAL和GAL器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆(“在系统”编程)将代码传送到目标芯片中,实现设计的数字系统。CPLD主要是由可编程逻辑宏单元(MC,Macro Cell)围绕中心的可编程互连矩阵单元组成。其中MC结构较复杂,并具有复杂的I/O单元互连结构,可由用户根据需要生成特定的电路结构,完成一定的功能。由于CPLD内部采用固定长度的金属线进行各逻辑块的互连,所以设计的逻辑电路具有时间可预测性,避免了分段式互连结构时序不完全预测的缺点。

1 TMS320VC5509A的并行引导模式

1.1 5509A的引导模式

5509A的引导模式选择是通过4个模式选择引脚BOOTM[3:0]来配置的,BOOTM3~0引脚分别与GPIO0、3、2、1相连。5509A提供了六种引导模式,即EHPI引导模式、8位/16位并行EMIF引导模式、8位/16位标准串行口引导模式、SPI EEPROM引导模式、USB引导模式以及I2C E2PROM引导模式。

在16位并行EMIF引导模式下,DSP芯片内部固化的Bootloader程序上电复位后,首先从CE1空间首地址0x200000h处开始读取程序代码,DSP芯片,也称数字信号处理器, 是一种具有特殊结构的微处理器。DSP芯片的内部采用程序和数据分开的哈佛结构,具有专门的硬件乘法器,广泛采用流水线操作,提供特殊的DSP指令,可以用来快速的实现各种数字信号处理算法。

1.2 5509A的引导表格式

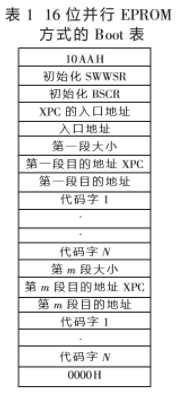

程序代码以引导表的格式存储在Flash存储器中。引导表是独立于所选引导模式的一种特定的格式,包含了用户程序的代码段、数据段、段在RAM中的目标地址以及程序入口地址等其他相关信息。5509A引导表结构如表1所示。

DSP芯片内部固化的Bootloader的主要功能是将Flash中存储的引导表按一定顺序加载到RAM中,然后跳转到32位程序入口地址开始执行。引导表文件可以通过TI公司提供的16进制转换工具生成,一般是hex格式,然后将此hex文件烧写到 Flash存储器中供Bootloader加载。

2 DSP二次Bootloader的原理及实现

由上述分析可知,DSP用户程序的并行加载过程是由DSP内固化的Bootloader实现的。由于5509A的PGE封装只有14根地址线,最多只能访问到16K×16bit地址空间。对于超过16KB的用户代码,Bootloader将不能加载全部的引导表文件。

二次Bootloader的原理是由用户自行编写一个代码长度小于16KB的引导程序(以下简称 uboot),其功能与DSP内固化的Bootloader相同,用于加载最终的用户代码。BootLoader就是在操作系统内核运行之前运行的一段小程序。通过这段小程序,我们可以初始化硬件设备、建立内存空间映射图,从而将系统的软硬件环境带到一个合适状态,以便为最终调用操作系统内核准备好正确的环境。在嵌入式系统中,通常并没有像BIOS那样的固件程序(注,有的嵌入式CPU也会内嵌一段短小的启动程序),因此整个系统的加载启动任务就完全由BootLoader来完成。比如在一个基于ARM7TDMI core的嵌入式系统中,系统在上电或复位时通常都从地址0x00000000处开始执行,而在这个地址处安排的通常就是系统的BootLoader程序。

2.1 DSP与Flash及CPLD的硬件接口

本文采用AMD的 Am29LV800作为DSP的外部存储器扩展。Am29LV800按8位方式访问,容量为1M字;按16位方式访问,容量为512K字。DSP外围电路逻辑译码及Flash高位地址线模拟由CPLD实现。Xilinx公司的XC9572XL是一款高性能的CPLD芯片,最高主频可达178MHz,包含了72个宏单元,1600个可用门电路,其TQFP封装有72个可用I/O引脚[7]。图1是5509A与CPLD及Flash之间的硬件接口设计原理图。

如图1所示,5509A的地址线A[13:1]与Flash的地址线A[12:0],A0未用。Flash存储器被映射到DSP的CE1空间,由片选线CE1经CPLD译码后选通。其中DSP的地址线A13和A与CPLD接口,用于换页寄存器FPR的模拟。

2.2 CPLD译码VHDL程序设计

目前DSP系统主频越来越高,运算速度越来越快,利用小规模逻辑器件译码的方式已不能满足DSP系统性能的需求。CPLD是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆(“在系统”编程)将代码传送到目标芯片中,实现设计的数字系统。

本文利用CPLD的快速逻辑译码功能,模拟了一个FPR寄存器来控制Flash的高位地址线。VHDL语言源程序如下:

begin

fce <=ce1;

foe <=aoe;

fwe <=awe;

h_addr <=a13;

l_addr <=a3&a2&a1;

datain <=d5&d4&d3&d2&d1&d0;

facs <=′1′ when h_addr=′1′

and ce2=′0′ and l_addr='000'

else ′0′; --CE2 0x400000

FPR:process(facs,awe,reset)

begin

if reset=′0′ then

fa<=″000000″;

else if reset=′1′ then

if awe′event and awe=′1′ then

if facs=′1′ then

fa<=datain(5 downto 0);

end if;

end if;

end if;

end process;

dataout<=fa when aoe=′0′ and facs=′1′

else ″ZZZZZZ″;

d5 <=dataout(5);

d4 <=dataout(4);

d3 <=dataout(3);

d2 <=dataout(2);

d1 <=dataout(1);

d0 <=dataout(0);

fa18 <=fa(18);

fa17 <=fa(17);

fa16 <=fa(16);

fa15 <=fa(15);

fa14 <=fa(14);

fa13 <=fa(13);

end behaviour;

由上述VHDL程序可知,FPR寄存器被映射到了CE2空间的0x401000地址。其中引入A13及A[3:1]地址线的目的是为了便于以后的功能扩展,映射出更多的寄存器,VHDL全名Very-High-Speed Integrated Circuit HardwareDescription Language,诞生于1982年。1987年底,VHDL被IEEE和美国国防部确认为标准硬件描述语言 。自IEEE-1076(简称87版)之后,各EDA公司相继推出自己的VHDL设计环境,或宣布自己的设计工具可以和VHDL接口。1993年,IEEE对VHDL进行了修订,从更高的抽象层次和系统描述能力上扩展VHDL的内容,公布了新版本的VHDL,即IEEE标准的1076-1993版本,简称93版。VHDL和Verilog作为IEEE的工业标准硬件描述语言,得到众多EDA公司支持,在电子工程领域,已成为事实上的通用硬件描述语言。

FPR寄存器定义如表2所示。

FPR寄存器的第5~0位分别控制Flash的高位地址线A18~A13,第7~6位无效。当DSP 上电复位时,FPR寄存器的值被设置为全0,此时Flash的所有高位地址线均处于低电平状态,DSP开始访问Flash的最低8KB地址单元。复位结束,就可以对FPR寄存器写入值,改变Flash的高位地址,从而实现Flash的分页访问。这样Am29LV800 Flash的512K字存储空间相当于被划分为64页(0~63),每页8K字,当程序大于一页时,修改FPR,进行软件翻页,读入下一页Flash数据,此时FPR寄存器与Flash的地址映射关系为:

Flash地址单元=(FPR《13)+DSP地址线A[13:1]

2.3 二次Bootloader的实现

基于上述的设计和分析,要实现大程序的自动引导,可以采用二次Bootloader的方法。首先要设计一个uboot程序,大小不能超过一页。将 uboot程序烧写到Flash存储器的第0页,也就是DSP上电复位后被固化的Bootloader自行引导的那一页。uboot的主要功能是通过修改 FPR寄存器值,并按照引导表的格式读取Flash存储器的其他页程序到RAM中,最后跳转到用户程序的32位入口地址开始执行,即:

unsigned int*FPR=(unsigned int*) 0x401000;

若*FPR=1,即可以访问Flash的第1页。

在编写uboot程序和用户程序时,要对存储器空间重新分配,即在定义CMD文件时,要注意用户程序所占用的存储空间不能与uboot程序占用的存储空间重叠。因为uboot首先被加载运行,在运行时加载用户程序,也需要占用RAM地址空间。而且uboot程序代码长度不能超过一页。当烧写Flash时,必须将uboot程序烧写到Flash的第0页,然后将用户程序烧写到第一页或以后的存储空间中。

3 实验结果

以煤矿井下煤矸分界传感器为例,测试本文介绍的基于CPLD译码的DSP二次Bootloader方法。该传感器采集放煤时煤矸石振动信号,经AD转换后送入DSP经数字信号处理,分析得出煤矸石放落比例。

将大小约2K字的uboot程序烧写到Flash第0页,用户烧写到第1~3页。经多次测试,该系统从上电复位到开始运行用户程序,耗时大约0.3s,而且系统运行稳定可靠。

电子发烧友App

电子发烧友App

评论