异质运算架构(HSA)将有助实现高效能、低功耗处理器设计。随着HSA标准和软体解决方案日益成熟,处理器研发人员将能利用此技术促进系统单芯片(SoC)内部的异质核心协同运作,并透过软体将复杂任务分配至最合适的运算单元,进而兼顾高运算效率和低能源消耗。

异质运算的时代终于来临,恰好能够解救处理器设计者脱离为迎合摩尔定律的28奈米(nm)新制程成本增加问题。处理器设计师不必只是仰赖昂贵的低功率电晶体,而是可以透过系统架构改善,将软体工作负载分配至不同异质运算单元,藉此协助降低能源消耗。

业界大厂合力推动 HSA技术受瞩目

近年来,处理器能源效率的进步,多半是因为朝小型化半导体制程的迅速发展,随着制造技术的推陈出新,每一电晶体的成本不断提高,异质系统架构(Heterogenous System Architecture, HSA)等替代技术因此而崛起。

不同于仰赖相同通用中央处理器(CPU)核心的同质处理器架构,HSA连结多种运算核心,如CPU、绘图处理器(GPU)、数位讯号处理器(DSP)、现场可编程闸阵列(FPGA)及固定功能硬体等,各类核心针对不同类型的应用工作负载而优化。

由超微半导体(AMD)、安谋国际(ARM)、Imagination、联发科、高通(Qualcomm)、三星电子(Samsung Electronics)与德州仪器(TI)等所设立的“HSA基金会”,旨在确保应用程式能够将任务分配至对于特定工作负载具有最高电源效率的超微次世代绘图核心(GCN)运算单元,藉此妥善管理应用程式执行。HSA基金会建立一套连接异质运算核心的开放标准,让各家业者得以各自发展支援共同软体基础架构的解决方案,从而实现具有高效能及高电源效率的异质应用。

同时支援x86/ARM架构 HSA实现跨平台设计

超微半导体于2014年初发表A系列加速处理器(APU)--Kaveri,可支援HSA功能。软体业者能够利用该系统,设计出广泛部署支援HSA之应用程式所需的软体开发工具。

HSA 的重要特性之一是能跨平台支援x86产品及安谋国际架构产品,并具备开发系统,可供开发支援HSA中间语言(HSAIL)的编译器及其他工具,促进真正的可携式应用。2014年6月首次公开发布HSA系统架构规格(暂定为版本1.0)后,现已有更多软体开发团队能够得知HSA的详情,进而利用更为简单的 HSA异质运算编程模型开发出新的节电演算法。

由于目前系统效能扩展受限于电力消耗,超微半导体已着手研发支援高度平行任务,可于 CPU与GPU间无缝平移的异质运算形式。这项技术创新构成HSA的基础,带来加强能源效率,同时提升效能并维持可编程性的契机。而要整合CPU与GPU 于同一芯片,关键就在于GPU的设计。

每单位能源消耗所完成的工作是通用的能源效率指标。举例来说,一台笔记型电脑的效率越高,就能让使用者以越少的电池耗电量及越低的发热程度完成相同任务。就行动运算而言,美国能源之星计画(United States Energy Star Program)制定一套典型耗能的合理概算标准;特别的是,这套标准是以“短期闲置”电力为主要依据。

一般而言,存取文件或打开网页之后,使用者会花时间检视结果。这样的闲置期间在现代系统中可能短如按键输入之间或影片讯框之间的间隔,这段时间处理器会进入低耗电状态。因此,超微半导体将运算能力除以标准能源使用,定义为其行动装置芯片的通常使用效率。例如,将两台效能相近的笔记型电脑相较,使用者必然偏好电池续航力较长的机种。同样地,若将两台电池续航力相同的笔记型电脑相较,使用者必然也会倾向选择效能较高且反应速度较快的那一台。这两种情况都能透过标准使用能源效率指标具体呈现。

超微半导体计画于未来6年之内将标准使用能源效率提升二十五倍,且已委托市场分析公司Tirias Research技术分析师就此目标加以评估,并为超微半导体所做研究的结果统整成一份技术白皮书,公布于Tirias Research网站。

为达成二十五倍如此积极的目标,超微半导体将广泛运用各种资源,除着重架构、设计及软体等方面之外,还将辅以矽晶圆制程技术。具体而言,超微半导体将聚焦于以下三大面向:

这些改良有助于降低闲置耗电,并发挥快速完成工作以更快回复低耗电状态的“加速进入闲置模式(Race To Idle)”优点。

.强化异质运算能力

HSA能够帮助APU提升一般工作负载效能(如以PCMark 8 v2.0等产业标准为基准测试所示),以及新兴的视觉导向互动工作负载(如自然使用者介面连同影像及语音辨识)。

.高电源效率实施的创新

透过运用如先进功率闸控、低电压操作等技术以及进一步整合系统组件等做法,提升APU矽智财(IP)效率。

Tirias Research指出,将降低闲置耗电及智能化电源管理所达成的节电功效,同时与异质运算效能提升和程序改善相结合。超微半导体应能达成在2014?2020年之间实现二十五倍标准使用能源效率改善的目标。

超微半导体目前已将笔记型电脑中的GPU、记忆体控制器、输入/输出(I/O)控制器及周边汇流排等系统组件全部都整合于单一晶粒中,可实现同时监控CPU 与GPU的精密化电源管理。这项技术能够有效平衡两种单元之间的电力最佳化,将散热能力集中在最须要散热的单元。除此之外,将GPU移至CPU晶粒,可以减少所需要之记忆体介面数量,同时还可以达到省电之效果。

超微半导体的智能电源管理以专用晶粒控制器追踪功耗、温度及各主要组件活动情形,使APU进一步提升效率。这种功率微控制器就像是“APU交响曲”的指挥,在正确的时间将处理重点导向正确的位置,其可快速回应热事件,控制器能够快速分配电力到CPU的特定部位,以发挥最大效能与效率。另外,也能判断各单元何时最无活动现象,并将其运作降低至最小状态或将之完全关闭。

处理元件若能以最短时间完成工作,然后进入最深休眠状态,即达到其最大能源效率。这种“加速进入闲置模式”行为对于网页浏览、文件编辑和相片编辑等多数消费者导向任务都很有助益。协调GPU与CPU的使用能够使APU更快完成任务,然后降低功率、减少总耗能(能量=功率×时间)。此一耗电状态过渡时间应极短,使单元尽快降低功率,让处理器能够在使用者进行按键输入或影片讯框之间,就可进入闲置状态。

借重HSA编程架构 处理器达成高效能/低功耗

超微半导体现正着手设计与1.0版HSA相容的新款APU,而HSA规格的目的在于协助软体利用GPU及其他处理元件的功率与效能。以GPU而非CPU来执行高度平行码时,APU能够利用其GPU核心的能源效率,以及巨量平行运算来处理工作负载,更快完成任务。HSA编程架构可将工作负载导向最佳芯片资源,例如专为特定演算法所设计的加速器,其设计宗旨在于减少完成固定工作负载所需周期数量及电力消耗,并在行动装置的功率限制内执行高阶运算密集式应用程式,转由GPU而非CPU处理之后,高阶行动应用程式(如语音辨识、手势辨识、脸部辨识等次世代使用者介面和相片索引)都能获得次方程度的效能改善。

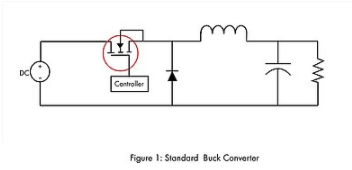

个人电脑处理器的效能随时间而成长,但步调相对较慢。另一方面,由于设计者将更多芯片空间留给图形处理,以支援4K解析度的显示设备,GPU效能得以快速攀升。藉由HSA架构,超微半导体就能善用这种GPU效能成长。将GPU用于一般任务的优点,展现于个人电脑应用程式和基准测试中(图1)。

图1 标准35W行动处理器的GPU运算趋势

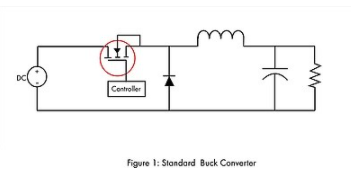

OpenCL 是首批支援以GPU执行平行运算的业界标准编程语言之一,可供C程式发挥语言扩充的功效,为代码的运算密集部分带来次方程度的效能提升。采用OpenCL 1.x(以OpenCL 2.x全面启用HSA的前身)加速时,PCMark 8 v2.0基准测试展现多达25%的增益(图2)。

图2 现有平台经由GPU卸载所达成的PCMark 8 v2.0加速

回头参考图1所示,异质架构利用GPU效能的快速成长,而GPU效能远胜近代CPU效能,GPU仍会是让未来处理器实现更高效能与能源效率的关键。每一个 GPU都有多个“着色器”核心(超微半导体将其称之为“串流处理单元”),每个核心都能处理整数或浮点运算,同时维持小于标准CPU核心的体积与耗电量。而且,由于每一个着色器核心都很小,所以单一晶粒可以整合数十甚至数百个着色器核心与个位数的通用CPU核心。因此,GPU可以对运用这么多处理核心的工作负载,产生次方以上程度的运算提升。上述所提及的每一种高阶应用程式,都可利用GPU固有的平行运算能力,来达成如此惊人的效能增益,而且耗电量极低。

图3显示超微半导体从2008年“Puma”CPU处理器,到2020年预测APU的标准使用耗电降低趋势。虚线表示至2015年的耗电趋势,Tirias Research预测超越此点后至2020年之间降低速度会相对减缓,因为耗电已趋近于0瓦(W)。但Tirias Research预测2015年,异质运算将大幅提升,驱动与GPU能力相称的更高效能水准。

图3 APU的能源使用与运算趋势

闲置耗电量降低,将可以帮助标准使用耗电,得以从相邻的2008年平台“Puma”CPU的近4W,降低至2014年“Kaveri”APU的1.6W,将会产生2.5倍的基准耗电量改善(两种产品都适用于相同的35W笔记型电脑热功率封包)。数量更多的CPU核心、更快的时脉速度,以及GPU运算协助,使得处理器效能得以改善,让“Kaveri”的运算力比起“Puma”高达4.5倍。因此,相较于“Puma”,“Kaveri”提供十倍 (2.5×4.5)以上的标准使用能源效率增加,如标准耗能最大效能所示。

Tirias Research预估超微半导体将利用多项远远超越“Kaveri”的效能改善,在2015年达成下一次的大幅耗电降低。由于耗电渐趋于零,且开始以平台组件功率为主,未来的闲置耗电降低步调必将趋缓。Tirias Research分析,根据超微半导体产品规画,该公司可望在2008年至2020年之间实现标准使用耗电量的大幅降低,在此12年间达成16倍的改善,如图3A线所示。

有鉴于GPU的效能预计将持续提升,且可运用此种异质运算能力(图3中B实线)的应用程式将越来越多,Tirias Research预测超微半导体将于2020年达到对等点。在此点上,约有一半的尖峰值效能将来自GPU,另一半则来自CPU。保守估计,由于CPU及 GPU两者都在持续进化,这种矽芯片资源分配方式能够使2020年的未来APU相较于2014年的“Kaveri”产生四倍的运算效能提升。

Tirias Research相信更大的GPU和更趋平行的应用程式将有助于促进更显着的效能改善。以此合理保守估计额外的四倍运算效能提升,结合至少六倍的标准使用耗电量降低,将可使超微半导体的最大效能对闲置耗电比在2014年至2020年之间展现高达二十五倍的改善。这是十分惊人的大幅变化,兼具两方面之长,低闲置耗电既可以减少能源耗用,又能以高峰值效能支援未来的高阶应用。

由于HSA可降低对于APU之CPU端的依赖程度,超微半导体将之视为改善高度平行工作负载效能与节电的必要方法。除了GPU之外,超微半导体现正配合智能型手机芯片开发者所需,将单一功能加速器整合于APU。这些专用加速器的设计目标是以最小晶粒面积提供最高能源效率表现,将耗电量降到最低。专用单元的缺点在于无法轻易适应新的演算法,因为可编程性的有限。而其他替代性可编程单元如以通讯与音讯处理见长的数位讯号处理器,可替CPU核心分担相关任务。

例如,超微半导体已于其最新APU及GPU中加入数位音效处理器,藉此解除CPU处理音讯的负担。对如音讯处理等工作负载而言,这些微小的架构新增可带来极大的功率效率增益,相较于单独以CPU处理,其增益可达两倍至将近二十五倍不等。

超微半导体运用支援HSA的软体结合其节电设计,让笔记型电脑和平板电脑APU的电池续航力与峰值效能胜过现今水准。

电子发烧友App

电子发烧友App

评论