锁相技术是如何定义的?锁相环是指什么?锁相环的三个组成部分和相应的运作机理是什么?

2021-06-21 06:52:00

锁相环仿真,可以参考一下!

2012-08-13 09:11:17

问一下大家,labview的锁相环怎么设计,我不知道怎么设计NCO,计算频率控制字的时候需要系统时钟频率,但是这个不知道怎么弄,大家有知道的吗,帮一下忙,谢谢!

2017-06-20 10:36:08

图解实用电子技术丛书,介绍锁相环(PLL)电路设计与应用,供大家参考

2016-06-21 22:51:39

要实现锁相环的基本原理及工作状态,如何编写程序呢?

2014-06-11 21:33:38

请问锁相环仿真用什么软件好,我们需要用到ADF4110VOC选择MAX2606

2016-06-27 15:57:53

硬件锁相环和软件锁相环,这个很好理解,很多东西原来都是直接用硬件电路搞出来,现在有可编程器件了,再利用软件来实现。传统的硬件锁相环在如谐波、频率突变、相位突变等电压畸变以及三相电压不平衡情况下,很难

2015-01-04 22:57:15

我用msp430和adf4106加一个vco 和环路滤波做了一个锁相环,但频率漂到其他地方了!请大神解决

2016-01-20 15:07:57

听说锁相环可以倍频,倍频时输入输出频率都不一样,如何锁相呢?

2023-04-24 10:14:34

ADI是高性能模拟器件供应商,在锁相环领域已有十多的的设计经验。到目前为止,ADI的ADF系列锁相环产品所能综合的频率可达8GHz,几乎能够涵盖目前所有无线通信系统的频段。ADF系列PLL频率合成器

2018-11-06 09:03:16

锁相环控制频率的原理锁相环频率自动跟踪-------用锁相环可以确保工作在想要的频率点上如何理解以下两段话?鉴相器是相位比较装置, 它把输入信号和压控振荡器的输出信号的相位进行比较, 产生对应

2022-06-22 19:16:46

我有一个锁相环电路的pcb板和proteus仿真电路。

2023-10-04 07:58:55

对于锁相环部分一直有个疑问:1)鉴相器是根据输入信号和输出信号的相位差来输出一个电压,通过LP后,控制压控振荡器的频率输出2)假如输入鉴相器的频率不同,那么电路是如何根据相位差来判断频率之间的差值呢?也就是相位差与频率差之间的关系是怎样的? 有木有相关的资料可以参考?或是请大牛们解释下,多谢啦

2017-07-27 09:03:46

本帖最后由 gk320830 于 2015-3-7 20:18 编辑

锁相环的原理,特性与分析所谓锁相环路,实际是指自动相位控制电路(APC),它是利用两个电信号的相位误差,通过环路自身调整作用,实现频率准确跟踪的系统,称该系统为锁相环路,简称环路,通常用PLL 表示。

2008-08-15 13:18:46

电荷泵锁相环的基本原理是什么?电荷泵锁相环的噪声模型与相位噪声特性是什么?电荷泵锁相环的相位噪声与环路带宽关系是什么?

2021-06-07 06:57:53

本帖最后由 zhihuizhou 于 2011-12-21 17:43 编辑

锁相环PLL原理与应用 第一部分:锁相环基本原理 一、锁相环基本组成 二、鉴相器(PD) 三

2011-12-21 17:35:00

那个对讲机的锁相环的程序怎么写?是基于STM32单片机的,锁相环芯片使用的是LMX2337

2014-04-09 08:18:49

你好,咨询一个有关锁相环芯片的问题: 使用ADIsimPLL仿真软件进行仿真,发现锁相环芯片4152HV芯片底噪在低频处是平的,而其它芯片,比如ADF4002芯片底噪包含1/f噪声,请问这是什么原因

2019-02-19 10:07:02

本人在进在做锁相环的仿真,进行频率跟踪的用的,可是怎么做都放不出波形,可有会仿真锁相环的?

2014-06-23 11:14:38

锁相环锁定与失锁的标志是什么?

2023-04-24 10:12:07

锁相环使两个波型相位相同, 当上电时有时两个波相位相同,有时不同是什么原因?急需要答案

2016-03-16 20:57:29

频率合成器的主要性能指标锁相环频率合成器原理锁相环频率合成器捕捉过程的分析与仿真

2021-04-22 06:27:35

用FPGA对AD9516进行配置,配置正常。寄存器回读也对,也能对AD9516进行控制。但是,AD9516的内部锁相环不能稳定锁相。锁相检测信号不断地高低翻转。检查0x18寄存器中表示锁相状态的标志位,该标志位也是不停的调变。这个电路是一个多次用过的电路,以前一直非常好用,从来没有遇到这种现象。

2019-02-19 09:38:47

如题,AD9957的锁相环一直失锁,不用锁相环输出点频信号时正常的,用了锁相环后,PLL_LOCK信号一直为低,sync_clk输出信号也不是稳定的周期信号,环路滤波器的值有点误差,因为现有的器件没有那么精确的电容电阻值,问下锁相环的控制除了控制CFR3之外还有别的要注意的么?

2018-12-10 09:30:24

求一ADF5355_锁相环相关资料,最好中文版,详细点

2017-03-06 23:32:13

新版AD公司锁相环仿真软件

2013-07-20 21:44:03

锁相有何意义?CD4046的工作原理是什么?CD4046锁相环有什么应用?

2021-05-27 07:07:38

求助,CD4046锁相环的参数要怎么设计呀?我设计的时候是根据datasheet设计的,可是用protues仿真的时候,在中心频率也入不了锁,引脚1输出总是一高一低,然后把输入信号的电压调大后,不管

2020-10-11 13:02:47

跪求哪位大神曾经实际验证TI自带软件锁相环的正确性(单相‘三相皆可)并最终用示波器拍图验证成功的???最好示波器图是白底,而且是那种带有U盘可以拷贝图片示波器出来的图形。急求!急求!急求!

2017-05-28 18:09:34

HMC820锁相环工作大于3个月时间后有些芯片失锁有30%(大概有100块),通过重新更换锁相环芯片的方式,主板正常工作,现在想读取锁相环里面的程序,请问有什么办法吗?现在找不到失锁的原因。

2018-08-03 08:10:07

电路会不断根据外部信号的相位来调整本地晶振的时钟相位,直到两个信号的相位同步。编辑添加图片注释,不超过 140 字(可选)在数据采集系统中,锁相环是一种非常有用的同步技术,因为通过锁相环,可以

2022-05-31 19:58:27

原理实现的频率及相位的同步技术,其作用是将电路输出的时钟与其外部的参考时钟保持同步。当参考时钟的频率或相位发生改变时,锁相环会检测到这种变化,并且通过其内部的反馈系统来调节输出频率,直到两者

2021-11-04 08:57:18

PLL(锁相环)电路原理是什么?

2022-01-21 07:03:37

`可编程锁相环(PLL)解决方案有多种尺寸和类型可供选择。 PLL以整数N或小数N形式提供同时根据带宽利用无源或有源环路滤波器。 可以通过3线串行接口对其进行快速编程同时提供非常低的杂散抑制和较小

2021-04-03 17:00:58

信号源的任何应用的理想选择,并且利用微带或陶瓷谐振器拓扑结构可提供出色的相位噪声性能。测试仪器雷达系统SFS10500H-LF锁相环SFS10625H-LF锁相环SFS10640H-LF锁相环

2021-04-03 17:05:46

a[10]=[0],用观察窗口观察变量时,只有a[0]=0,其他值仍然是随机值。难道数组的初始化必须对每个元素分别赋值吗?

2. 单相数字锁相环的设计。目前我们在进行单相光伏并网逆变器的开发,在对电网相位的跟踪上处理不是特别好,请问贵司有没有数字锁相环的程序包或者相关的说明文档可以参考?

2018-05-14 03:22:42

labview虚拟锁相环的跟踪锁定时间过长,请问有什么办法可以解决这个问题

2011-05-17 19:03:34

前辈们你们好,我是在校学生在做锁相环鉴频仿真实验,但是无法得到好的结果,请问前辈们可以指导一下么?谢谢!

2020-06-01 10:20:04

介绍了频率捕获、电荷泵锁相环等热点应用问题。目录:第1章 简介1.1 PLL的性质1.1.1 带宽1.1.2 线性1.2 本书结构1.3 文献及注释1.3.1 推荐书目1.3.2 技术文集1.3.3

2017-08-10 17:44:31

什么是锁相环 (PLL)?一个锁相环PLL电路通常由哪些模块组成?

2022-01-17 06:01:54

介绍了锁相环路的基本原理,分析了集成锁相环芯片ADF4106的工作特性,给出了集成锁相环芯片ADF4106的一个应用实例,为高频频率合成器的设计提供了很好的思路。 关键词:ADF4106,锁相环,频率合成器,环路滤波器

2019-07-04 07:01:10

采用后向Euler数值积分法实现二阶锁相环的一个仿真模型,对二阶锁相环进行仿真,那位大侠做过?可以参考下原代码不?

2012-05-28 17:21:05

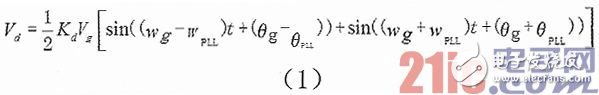

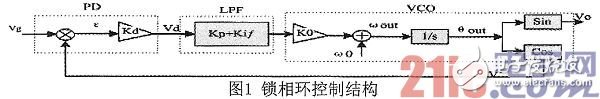

。传统的锁相环各个部件都是由模拟电路实现的,一般包括鉴相器(PD)、环路滤波器(LF)、压控振荡器(VCO)三个环路基本部件。 随着数字技术的发展,全数字锁相环ADPLL(AllDigital

2010-03-16 10:56:10

跟踪输入频率的变化。 锁相环具有良好的跟踪性能。若输入FM 信号时,让环路通带足够宽,使信号的调制频谱落在带宽之内,这时压控振荡器的频率跟踪输入调制的变化。 对于锁相环的详细分析可参阅有关锁相技术

2019-03-17 06:00:00

有没有大神有用Verilog代码写的数字锁相环程序呀,求 。谢谢

2017-07-05 22:54:56

小弟需要对正弦信号进行锁相,就是锁相环的输入输出都是正弦信号,有合适的芯片吗?最好给点资料,小弟急需!!还有芯片要可以外接倍频单元。在此谢过了!!!

2011-03-13 09:46:00

请问可以用锁相环来制作DDS吗?并且用单片机控制

2016-06-28 17:51:01

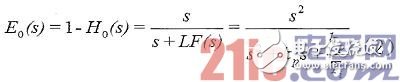

,就像空气之于人类。 本次记录一下基于二阶广义积分器虚拟两相的单相软件锁相环的simulink仿真。仿真搭建如图1 所示。...

2021-07-09 07:20:10

一、内容继续无霍尔的学习,根据原理及仿真,了解相关原理和实现方法。二、知识点1.基于锁相环的转子位置估计反正切函数的转子位置估算由于是根据估算的扩展反电动势进行计算的,但是由于滑模控制在滑动模态下

2021-08-27 06:54:13

随着集成电路技术的不断进步,数字化应用逐渐普及,在数字通信、电力系统自动化等方面越来越多地运用了数字锁相环。它的好处在于免去了模拟器件的繁琐,而且成本低、易实现、省资源。本文综合以上考虑,在一片FPGA中以Quartus II为平台用VHDL实现了一个全数字锁相环功能模块,构成了片内锁相环。

2019-10-10 06:12:52

锁相环频率合成器是什么原理?基于CD4046的锁相环频率合成器的设计

2021-04-12 06:28:35

全数字锁相环由那几部分组成?数字锁相环的原理是什么?如何采用VHDL实现全数字锁相环电路的设计?

2021-05-07 06:14:44

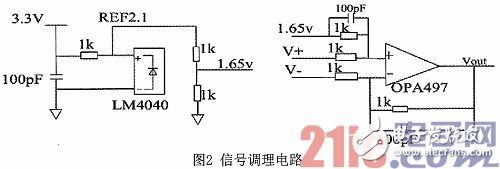

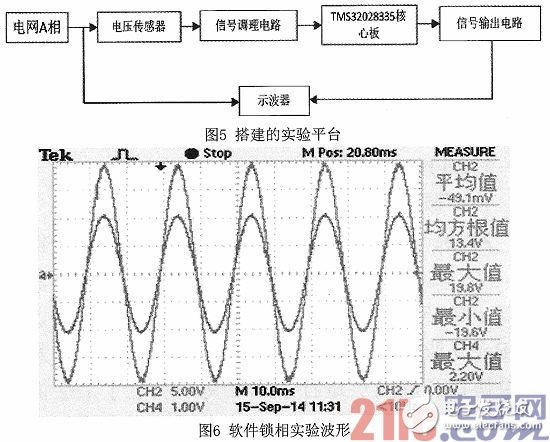

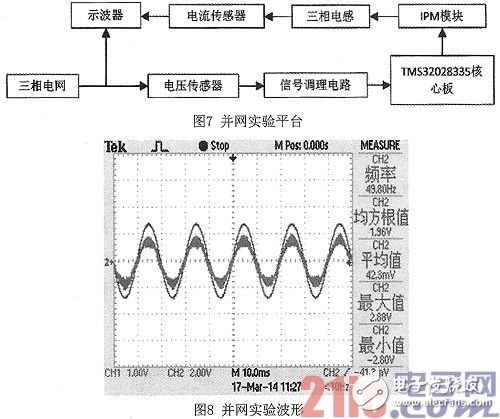

摘要:本文针对光伏并网发电系统中数字锁相环易受过零检测电路影响,稳定度差的问题,采用了相应的硬件和软件方法解决锁相环稳定性问题。硬件上通过提前过零检测来补偿加重滤波器带来的相位滞后;软件上加入判断

2018-12-05 09:53:26

本帖最后由 gk320830 于 2015-3-9 20:38 编辑

最近在用adf 4001做一个锁相环,环路配置好后发现锁定不了,电荷泵cp 输出一直在扫描,检查芯片内部的配置,也没发现什么问题,分频输出也是正常的,哪位高手用过这个芯片,帮我分析分析吧,期待中。。。

2010-09-14 08:52:16

摘要:本文针对光伏并网发电系统中数字锁相环易受过零检测电路影响,稳定度差的问题,采用了相应的硬件和软件方 法解决锁相环稳定性问题。硬件上通过提前过零检测来补偿加重滤波器带来的相位滞后;软件上加入判断

2018-12-03 14:01:24

本文按照数字锁相环设计的步骤,采用手把手的方式讲述设计过程和原理,旨在给数字锁相环初次设计者提供一个思路,缩短开发的时间。 有关数字锁相环的帖子不断出现,但大多没有讲述其原理。翻开有关锁相环的书总是

2012-01-12 15:29:12

数字锁相环设计源程序PLL是数字锁相环设计源程序, 其中, Fi是输入频率(接收数据), Fo(Q5)是本地输出频率.目的是从输入数据中提取时钟信号(Q5), 其频率与数据速率一致, 时钟上升沿锁定在数据的上升和下降沿上;顶层文件是PLL.GDF

2009-12-18 10:37:37

锁相环解调ask,解调信号出不来,哪里错了啊谁能帮我改一下,做设计用的。有偿求助。

2016-01-08 16:56:33

fpga中的用锁相环产生时钟信号相比于用计数器进行分频有哪些优点,看fpga中锁相环的结构,其前期的输入信号和后期的输出信号不也是通过计数器进行分频实现的吗

2014-10-06 10:46:05

RT 我想做一个DSP的软件锁仙环,将电网三相电压侧回来 进行锁相,求dq变换怎么写

2014-05-06 14:59:01

模拟锁相环与数字锁相环的主要区别在哪里?

2023-04-24 10:48:52

经典数字锁相环路结构及工作原理是什么?改进的数字锁相环结构及工作原理是什么怎样对改进的数字锁相环进行仿真?

2021-04-20 06:47:12

。本文就将为大家介绍在DSP系统中如何有效避免噪声和EMI产生,对其中的电源隔离和锁相环进行介绍。 电源隔离和锁相环 如何实现最佳供电是控制噪声和辐射的最大挑战。动态负载开关环境很复杂,包括的因素

2018-11-30 17:14:11

本文介绍了电荷泵锁相环电路锁定检测的基本原理,通过分析影响锁相环数字锁定电路的关键因子,推导出相位误差的计算公式。并以CDCE72010 为例子,通过实验验证了不合理的电路设计或外围电路参数是如何影响电荷泵锁相环芯片数字锁定指示的准确性。

2021-04-20 06:00:37

软件锁相环的基本模型软件锁相环的数学模型多速率条件下的软件锁相环软件锁相环的DSP实现

2021-04-21 07:22:49

怎样去设计一种自适应软件锁相环?如何对自适应软件锁相环进行测试?

2021-06-08 07:07:17

您好! 请问ADI是否这样的锁相环芯片,在外参考输入时钟不关的情况下,开关锁相环芯片,锁相环输出时钟相位保持一致,也就是说只要输入参考不变,开关锁相环芯片,输出时钟相位保持不变,若变,变化范围是多大, 若无此类锁相环芯片,请问ADI是否有此类问题的解决方案。 十分感谢!!

2018-08-31 11:00:43

我刚接触锁相环没多长时间,最近想使用ADF4106搭建一个双环锁相环,我阅读的资料都没有说主环路环路滤波器参数计算问题,我想咨询专家ADIsimPLL是否可以仿真计算双环锁相环,如果可以具体怎么考虑,如果可以告诉我一些主环路环路带宽的知识就更好了.

2019-03-07 10:34:03

音频锁相环相关资料集很多好资料哦! [hide]音频锁相环相关资料等.rar[/hide]

2009-12-04 11:43:03

本帖最后由 gk320830 于 2015-3-7 16:40 编辑

高速数字锁相环的原理及应用

2012-08-17 10:47:04

本文针对一款应用于大规模集成电路的CMOS高频锁相环时钟发生器,提出了一种可行的测试方案,重点讲述了锁相环的输出频率和锁定时间参数的测试,给出了具体的测试电路和测试方法。对于应用在大规模电路系统中的锁相环模块,该测试方案既可用于锁相环的性能评测,也可用于锁相环的生产测试。

2021-04-21 06:28:15

根据虚拟无线电技术的特点和锁相环的基本原理,提出一种适于计算机软件化实现的锁相环数学模型,分析不同参数对锁相环捕获和跟踪性能的影响,得出不同情况下参数设定的基

2008-08-15 12:36:19 101

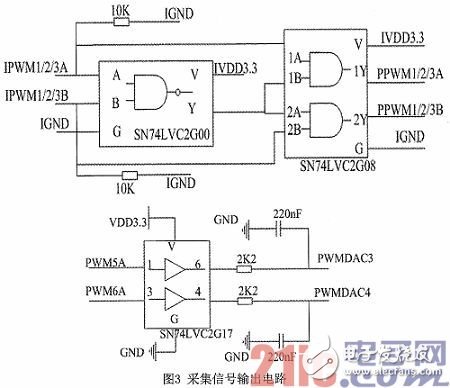

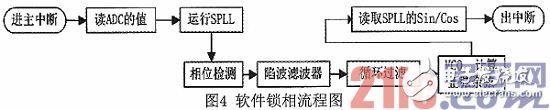

101 基于DSP的软件锁相环的实现

2017-06-22 09:54:06 69

69 中采用的锁相技术是基于数字信号处理技术在 DSP等通用可编程器件上的实现形式 ,由于这一类型锁相环的功能主要通过软件编程实现, 因此可将其称为软件锁相环 (software PLL )。

2021-05-28 10:44:35 33

33

电子发烧友App

电子发烧友App

评论