CPU接收到指令后,它会最先向CPU中的一级缓存(L1 Cache)去寻找相关的数据,然一级缓存是与CPU同频运行的,但是由于容量较小,所以不可能每次都命中。

2022-10-21 09:10:54 1866

1866 A53的L1 Data cache遵从的是MOESI协议,如下所示在L1 data cache的tag中存有MOESI的标记位。

2023-09-01 15:01:21 5024

5024

Cache是位于CPU与主存储器即DRAM(Dynamic RAM,动态存储器)之间的少量超高速静态存储器SRAM(Static RAM)

2023-10-31 15:07:23 347

347

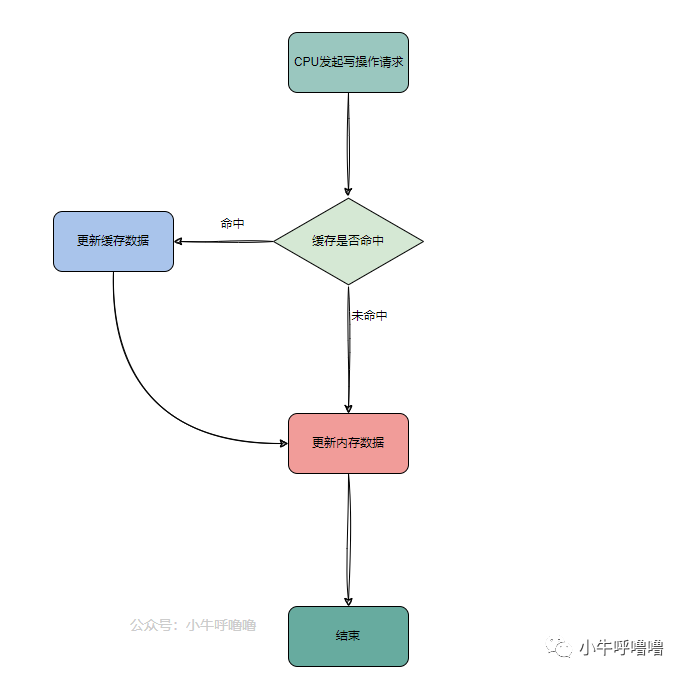

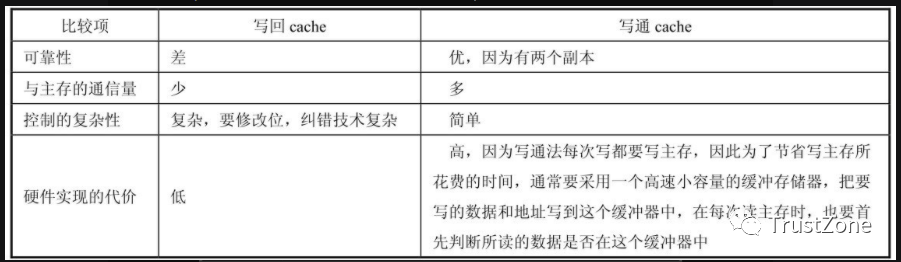

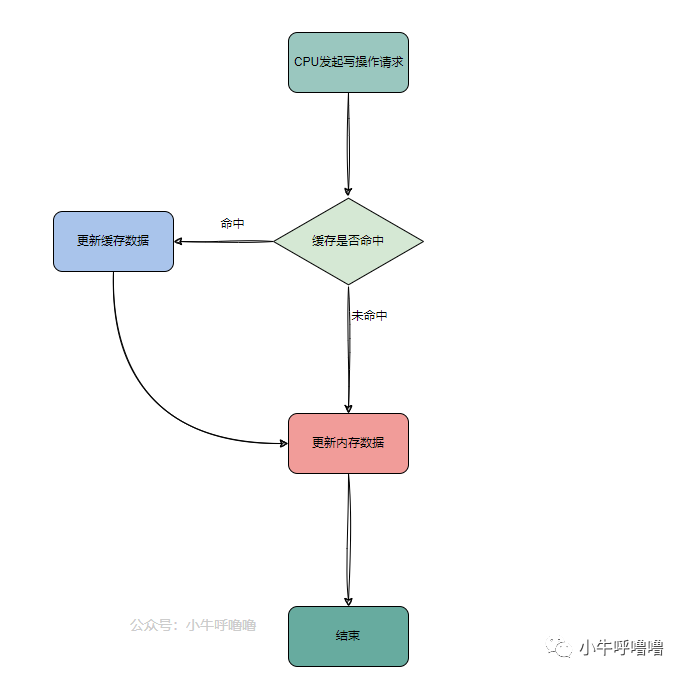

我们介绍`CPU Cache`的组织架构及其进行**读操作**时的寻址方式,但是缓存不仅仅只有读操作,还有 **写操作** ,这会带来一个新的问题

2023-12-04 15:05:32 460

460

请问:

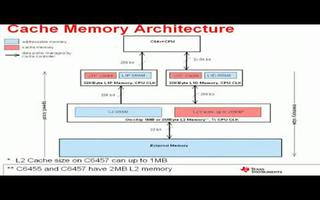

1、如果将L1D CACHE设置为32KB,L1P CACHE设置为32KB,L2 CACHE设置为0KB;

在core的LL2中定义了两个数组,out1占用32KB存储空间,out2占用

2018-06-21 13:28:12

Cache为什么还要分I-Cache,D-Cache,L2 Cache,作用是什么?

2023-10-25 06:38:45

Cache即高速缓存,它的出现基于两种因素:一、CPU的速度和性能提高很快,而主存速度较低且价格高;二、程序执行的局部性特点。将速度较快而容量有限的SRAM构成Cache,可以尽可能发挥CPU

2019-10-12 06:01:10

存储器的层次结构是怎样的?由哪些部分组成的?有何特点?Cache的原理是什么?Cache地址的过程是怎样的?

2021-12-23 09:35:31

cache到 ddr里面的数据呢?还是数据自动cache到L1D里面呢?能不能详细解释一下cache的工作原理!期待您的答复!谢谢!

2018-06-21 15:10:16

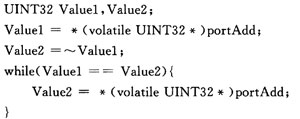

cache有哪些缺点很多时候大家谈论cache都只会谈及各种好处,比如加快程序执行的速度,减少主存的访问。但是,cache还引入了没有cache的系统不存在的一些问题。其中一个缺点就是,程序

2022-06-15 16:16:16

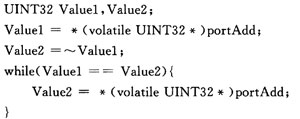

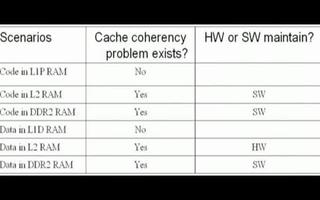

文章目录1、cache的应用——什么时候需要刷cache1、cache的应用——什么时候需要刷cache(1)、cpu在往内存(src地址)写数据时,cache中会缓存这些数据,并没有立即同步到

2021-07-22 08:43:16

ARM处理器中的逻辑cache和物理cache是什么?有没有哪位大神可以帮忙解决一下这个问题

2022-11-03 15:25:40

cache。这对于那些需要频繁修改页表映射的多任务系统具有显著优势。使用虚拟地址作为index也有一些硬件优势,这意味着cache硬件在进行cache look up时不需要进行虚拟地址到物理地址

2022-06-20 15:22:23

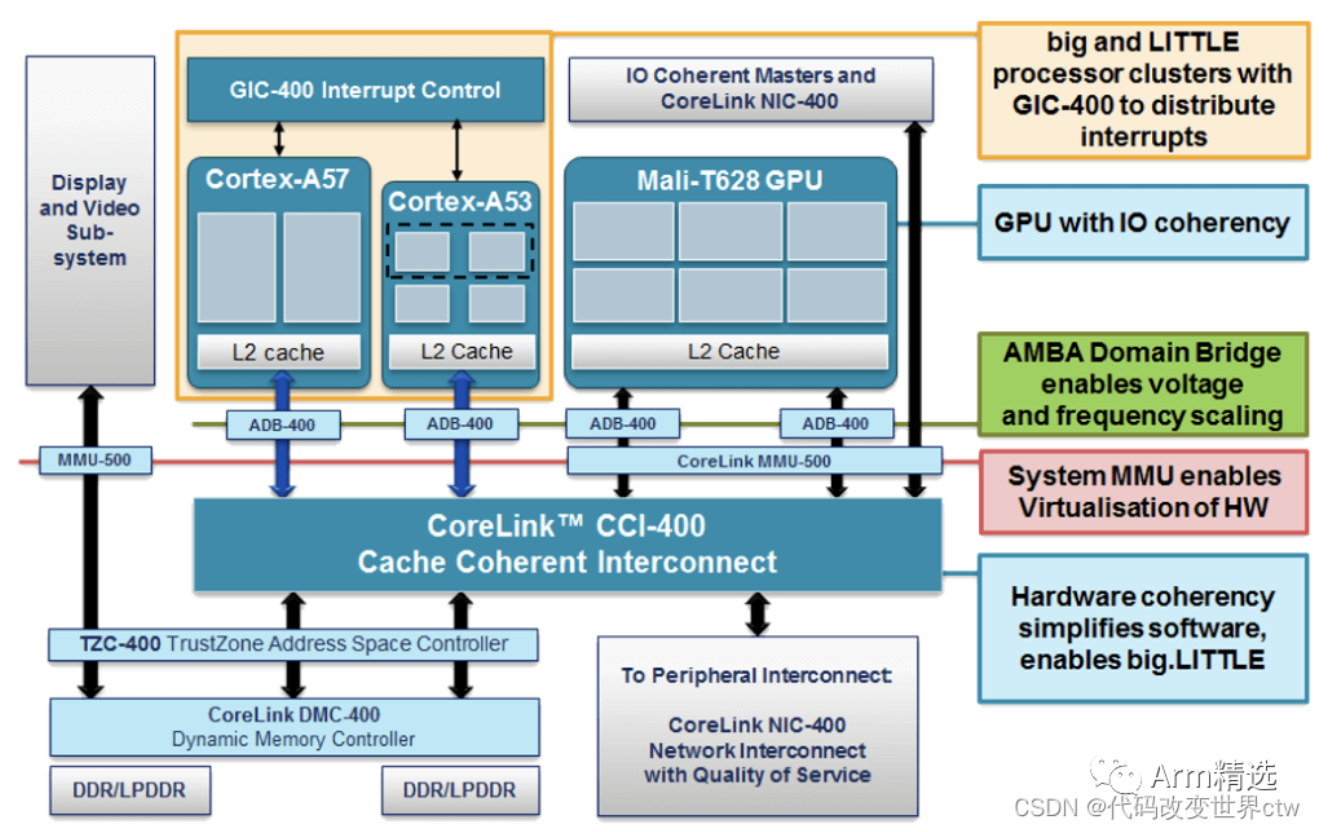

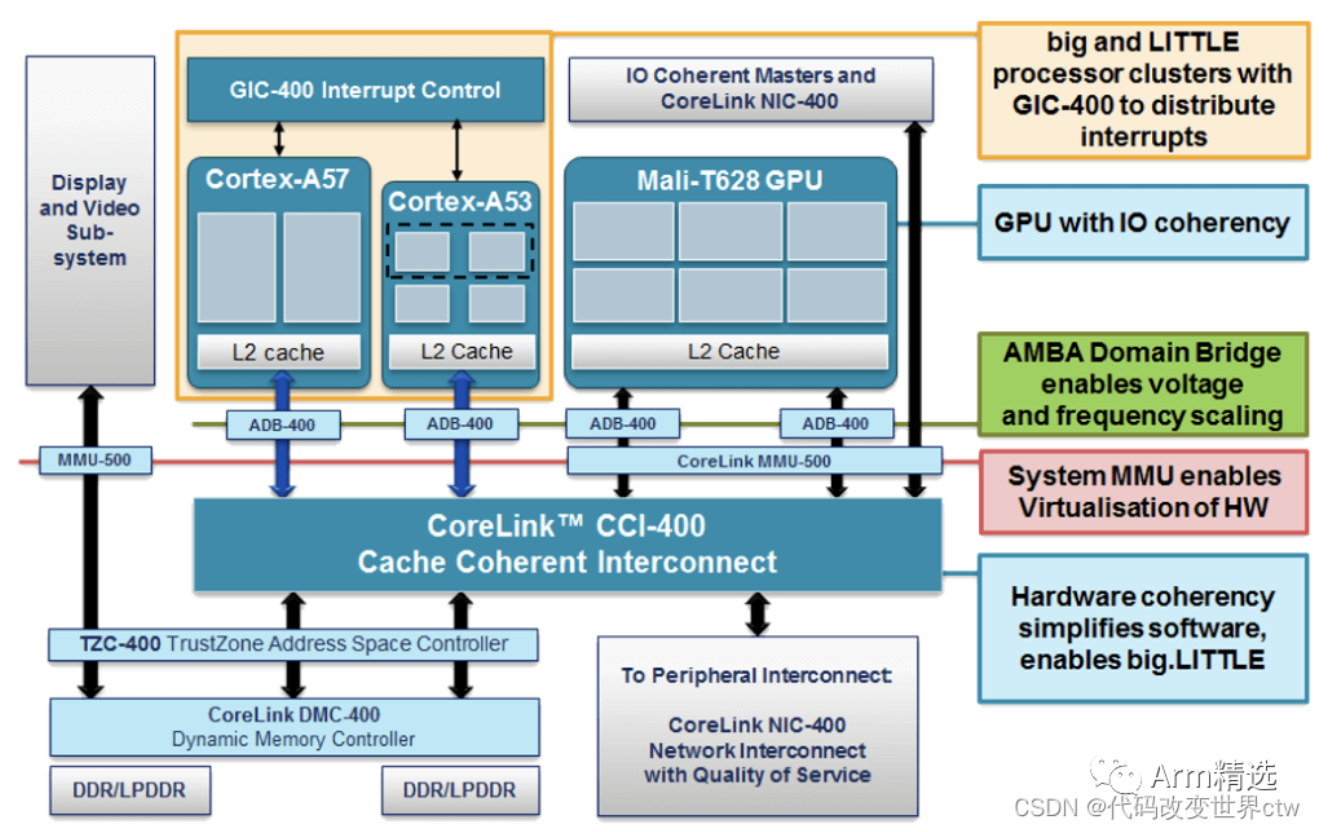

Arm处理器cache的进化Cache对CPU处理器的性能影响毋庸置疑。RISC构架成功的一个重要因素就是cache对内存访问性能的提升。RISC处理器普遍采用load-store的构架,随着

2022-12-14 16:17:15

对于其它外设不会修改,即只有CPU进行读写的数据,有两种配置方案:1.将L2 Cache配置为SRAM,数据存于L2 Cache,即数据直接放置于L2 Cache中2.配置L2 Cahce全部为缓存,将数据存于DDR2中,配置此段DDR2相应的MAP寄存器以上两种方案,哪种方案更优?

2019-08-05 14:50:55

except for not having the U bit.我们可以看到,Cache分为address section和data section两个部分. 它们实际上就是CPU中的一小块RAM,这一

2014-12-29 15:42:51

对于没有接触过底层技术的朋友来说,或许从未听说过cache。毕竟cache的存在对程序员来说是透明的。在接触cache之前,先为你准备段code分析:int arr[10][128];for (i

2022-04-21 11:10:49

设计多级cache可以有很多种方式,可以根据一个cache的内容是否同时存在于其他级cache来分类,即Cache inclusion policy。如果较低级别cache中的所有cacheline

2022-07-20 14:46:15

请教:平台是6678,ccs5.4,使用CSL库函数 CACHE_disableCaching 禁止cache 0x8000000地址CACHE_disableCaching(128);调用

2018-12-28 11:12:02

工程师你好:

最近看了6678的cache手册,仍有下面不确定的问题,请解答(以下都是说的数据cache,不是程序cache)。

1、CPU对L2 RAM和L2 Cache的访问速度是不是一样

2018-06-21 07:43:09

帮忙给解答一下一个基本概念,cpu在访问数据时,如果数据不在L1D和L2中,就需要从DDR等外设中取数,文献中说过,“cache会prefetch读取cache_line长度的地址,保证连续的地址上

2018-06-21 17:31:26

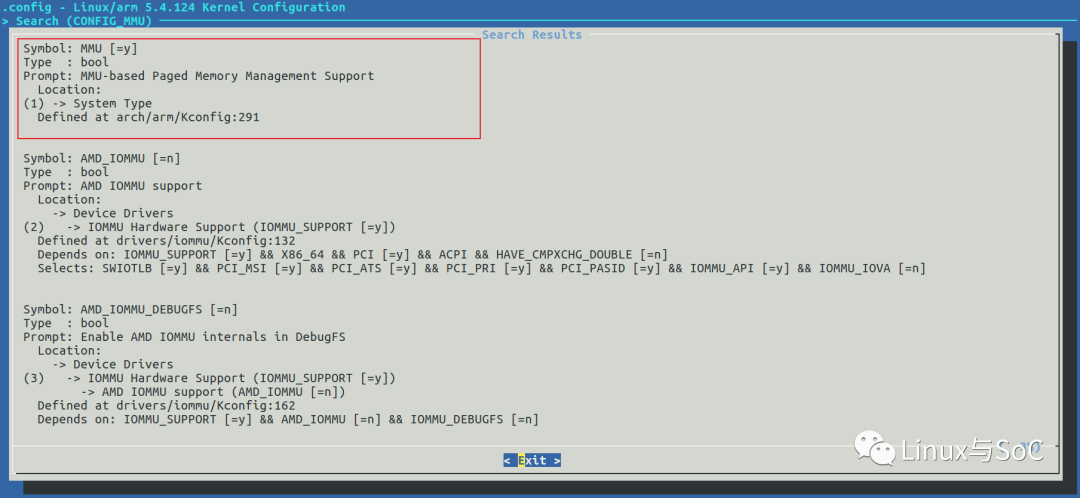

CPU Cache是什么?如何查看自己电脑CPU的Cache信息呢?

2021-10-19 08:42:39

请问,用I.MX6UL开发板OKMX6UL,使用Linux的情况下,如何获取CPU中L1/L2的Cache状态和大小;如何禁用和使能Cache?

2022-11-29 06:37:16

我最近看6437的cache。话说如果不使能所有cache.那dspcpu也是可以访问ddr2的是吧。那这个路径是怎么样的呢。在手册上的Block Diagram等都没看到。都讲的是ddr2到l2,l1到cpu这么个cache路径。按常识肯定是cpu直接访问了ddr2,只是速度慢点而已。

2018-08-02 07:15:27

总是弄不明白cache_inv,cache_wb以及cache_wbinv都有什么区别,请专家指教!

2018-07-24 07:41:03

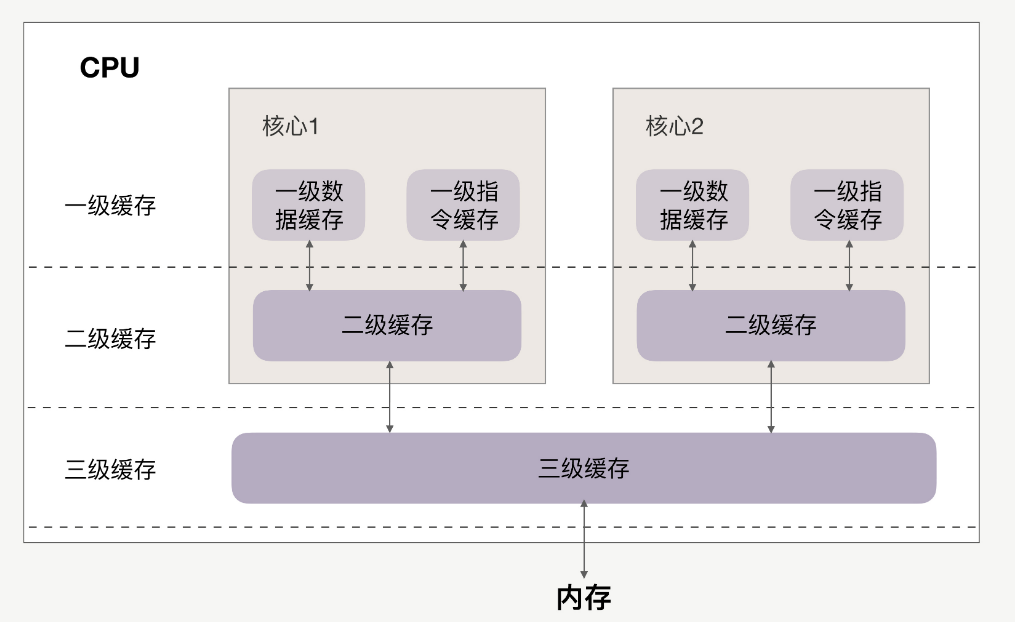

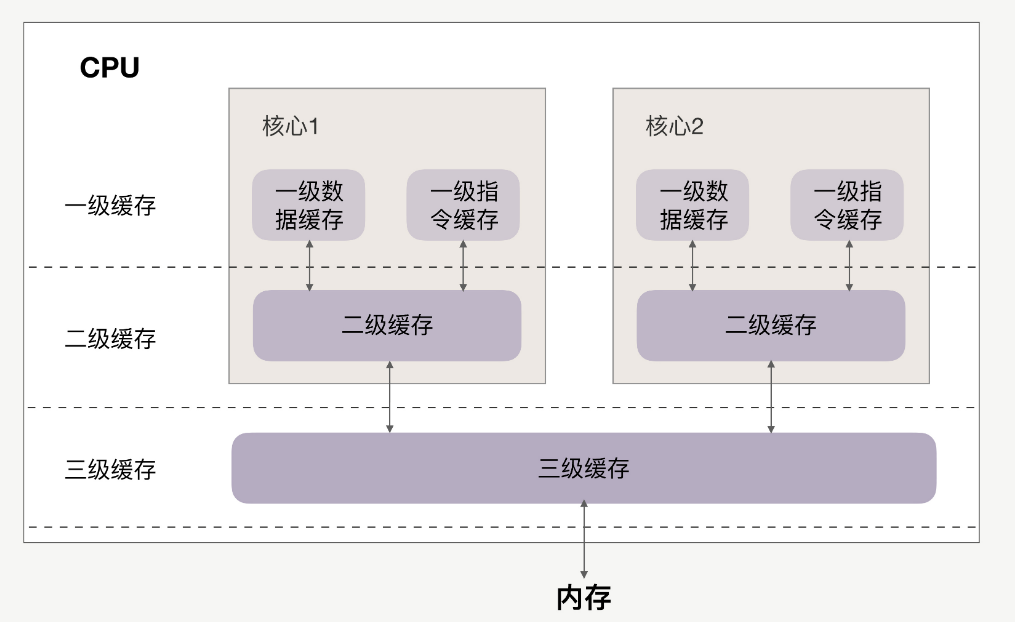

Cycle,且往往被分成 ICache 和 DCache,一般 L1 Cache 是由一个 CPU 核心独享的L2 Cache 一般有较高的相联度 (减少 miss rate) ,容量为几百 KB ~ 几

2022-09-16 14:31:35

以优化压缩cache的替换策略为目标,提出一种优化的基于修正LRU的压缩cache替换策略MLRU-C。MLRU-C策略能利用压缩cache中额外的tag资源,形成影子tag机制来探测并修正LRU替换策略的错误

2009-04-15 09:51:03 36

36 针对嵌入式CPU 指令处理速度与存储器指令存取速度不匹配问题,本文基于FPGA 设计并实现了可以有效解决这一问题的指令Cache。根据嵌入式五级流水线CPU 特性,所设计指令Cache 的地

2009-08-05 14:27:54 36

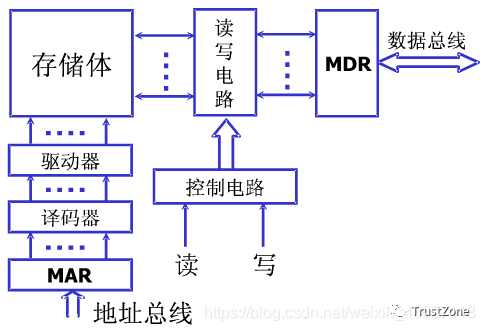

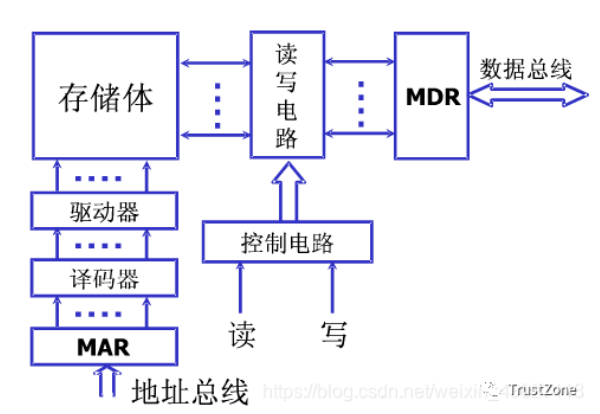

36 Cache的工作原理:Cache的工作原理是基于程序访问的局部性。对大量典型程序运行情况的分析结果表明,在一个较短的时间间隔内,由程序产生的地址往往集中在存储器逻辑地址空

2009-09-19 07:48:54 13

13 摘要:在SoC系统中,片上缓存(Cache)的采用是解决片上处理器和片外存储器之间速度差异的重要方法,Cache中用来存储标记位并判断Cache是否命中的Tag电路的设计将会影响到整个Cache的

2010-05-08 09:26:24 11

11 CACHE对于CPU来说非常重要,它们是处理器和内存等数据交换的高速缓冲地带,可以对使用过的数据和指令进行有选择的保留,以便以后直接调用,这样将大大提高系统的速度。

2010-10-04 21:21:18 22

22 Cache结构的低功耗可重构技术分析

在分析Cache性能的基础上介绍了当前低功耗Cache的设计方法,提出了一种可重构Cache模型和动态

2009-03-29 15:07:55 663

663

什么是缓存Cache

即高速缓冲存储器,是位于CPU与主内存间的一种容量较小但速度很高的存储器。由于CPU的速度远高于主内存,CPU直接

2010-01-23 10:57:13 735

735 什么是Cache/SIMD?

Cache :即高速缓冲存储器,是位于CPU与主内存间的一种容量较小但速度很高的存储器。由于CPU的速度远高于主内存

2010-02-04 11:29:44 515

515 什么是Instructions Cache/IMM/ID

Instructions Cache: (指令缓存)由于系统主内存的速度较慢,当CPU读取指令的时候,会导致CPU停下来

2010-02-04 11:51:01 583

583 什么是Cache

英文缩写: Cache

中文译名: 高速缓存器

分 类: IP与多媒体

解 释: 信息在本地的临时存储

2010-02-22 17:26:39 948

948 高速缓存(Cache),高速缓存(Cache)原理是什么?

高速缓存Cache是位于CPU和主存储器之间规模较小、存取速度快捷的静态存储器。Cache一般由

2010-03-26 10:49:27 6717

6717 cache基本知识培训教程[2]

相联度越高(即 n 的值越大), Cache 空间的利用率就越高,块冲突概率就越低,因而 Cache 的失效率就越低。块冲突是指一

2010-04-13 16:25:37 1982

1982 降低Cache失效率的方法[2]

表4.7列出了在这两种极端情况之间的各种块大小和各种 Cache 容量的平均访存时间。速度最快的情况: Cache 容量为1KB、4KB、1

2010-04-13 16:33:59 4688

4688 嵌入式编程需注意的Cache机制及其原理

1 Cache的原理 Cache即高速缓存,它的出现基于两种因素:一、CPU的速度和性能提高很快,而主

2010-05-26 16:40:03 1150

1150

现代高速处理器的设计中对于cache技术的研究已经成为了提高处理器性能的关键技术,本文针对在流水线结构中采用非阻塞cache技术进行分析研究,提高cache的命中率,降低缺少代价,提高处理器的性能,并介绍了“龙腾”R2处理器的流水线结构的非阻塞cache 的设计。

2015-12-28 09:54:57 8

8 1 Cache的原理 Cache即高速缓存,它的出现基于两种因素:一、CPU的速度和性能提高很快,而主存速度较低且价格高;二、程序执行的局部性特点。将速度较快而容量有限的SRAM构成Cache,可以

2017-11-01 16:16:20 0

0 随着集成电路设计复杂度指数级增长,功能验证已经越来越成为大规模芯片设计的瓶颈,而在多核处理器中,Cache -致性协议十分复杂,验证难度大。针对Cache -致性协议验证提出基于模拟验证的一种

2017-11-17 17:24:07 2

2 cpu在执行程序所用的指令和读数据都是针对内存的,也就是从内存中取得的。由于内存读写速度慢,为了提高cpu和内存之间数据交换的速度,在cpu和内存之间增加了cache,它的速度比内存快,但是造价

2018-04-02 10:35:06 6404

6404 本文开始阐述了CACHE的概念、CACHE替换机构与读写操作,其次介绍了寄存器的原理以及它的主要技术,最后阐述了寄存器和cache两者之间的区别。

2018-04-11 14:10:33 11827

11827 GPU采用了数量众多的计算单元和超长的流水线,但只有非常简单的控制逻辑并省去了Cache。而CPU不仅被Cache占据了大量空间,而且还有有复杂的控制逻辑和诸多优化电路,相比之下计算能力只是CPU很小的一部分

2018-04-28 10:26:00 28332

28332 GPU cache是由Alembic文件派生出来的一种文件格式,为获取Maya中快速播放的性能专门做了优化。这些性能的提升来自于GPU cache文件求值的方式。GPU cache节点会避开Maya的dependency graph求值机制,把缓存数据直接发送到系统的图形卡接口进行处理。

2018-04-28 10:29:00 2726

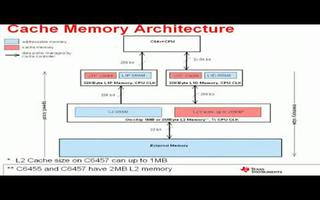

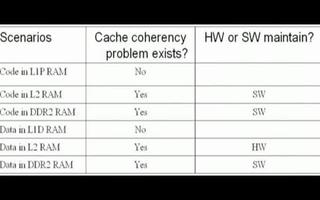

2726 C64+ 系列DSP上Cache 的应用(第一部分)

2018-06-13 01:08:00 3780

3780

C64+ 系列DSP上Cache 的应用(第二部分)

2018-06-13 01:01:00 3661

3661

从Cache-主存模型来看,一方面既要使CPU的访存速度接近于访Cache的速度,另一方面为用户程序提供的运行空间应保持为主存容量大小的存储空间。在采Cache-主存层次的系统中,Cache对用户程序而言是透明的,也就是说,用户程序可以不需要知道Cache的存在。

2018-08-20 15:27:41 4230

4230

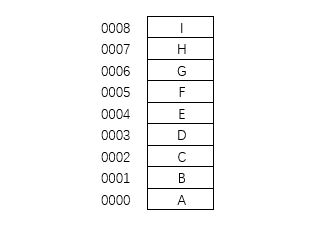

当CPU开始访问地址0020h时,假设cache已经被完全被设定无效了(invalidated),即没有cache line包含有效数据。

2018-09-09 10:39:57 7601

7601 当你读写文件的时候,Linux内核为了提高读写性能与速度,会将文件在内存中进行缓存,这部分内存就是Cache Memory(缓存内存)。即使你的程序运行结束后,Cache Memory也不会自动释放。

2019-04-26 15:49:14 1085

1085 。 本文简介了Cache的概念、原理、结构设计以及在PC及CPU中的实现。 Cache的工作原理 Cache的工作原理是基于程序访问的局部性。 对大量典型程序运行情况的分析结果表明

2019-04-02 14:38:30 1951

1951 文件 Cache 管理是 Linux 内核中一个很重要并且较难理解的组成部分。本文详细介绍了 Linux 内核中文件 Cache 管理的各个方面,希望能够对开发者理解相关代码有所帮助

2019-04-02 14:38:49 344

344 那么什么是 cache?如何利用这一新特性编写高性能的程序?又有什么要注意的地方吗?

2019-05-07 15:24:52 7920

7920

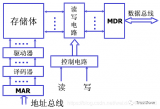

更详细的讲,cache的结构其实和内存的结构类似,也包含地址和内容,只是cache的内容除了存的数据(data)之外,还包含存的数据的物理内存的地址信息(tag),因为CPU发出的寻址信息都是针对

2019-06-03 14:24:13 10854

10854

page)即为页缓存(page cache)。块缓存(buffer cache),则是内核为了加速对底层存储介质的访问速度,而构建的一层缓存。

2021-07-02 14:25:13 2299

2299

CACHE基础 对cache的掌握,对于Linux工程师(其他的非Linux工程师也一样)写出高效能代码,以及优化Linux系统的性能是至关重要的。简单来说,cache快,内存慢,硬盘更慢

2021-07-26 15:18:58 1507

1507

Linux内核文件Cache机制(开关电源技术与设计 第二版)-Linux内核文件Cache机制

2021-08-31 16:34:54 4

4 微软内核构架之Cache管理器(实用电源技术手册磁性元器件分册pdf)-微软内核构架之Cache管理器

2021-08-31 16:39:58 10

10 作者:Spongecaptain https://spongecaptain.cool/SimpleClearFileIO/ 1. Page Cache 1.1 Page Cache

2021-10-20 14:12:41 5320

5320

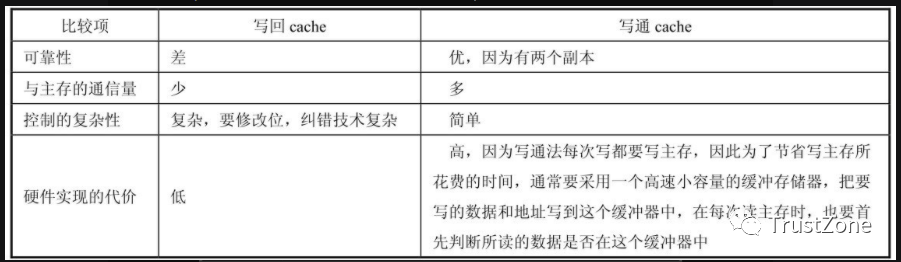

关于cache,大概可以从三个方面进行阐述:内存到cache的映射方式,cache的写策略,cache的替换策略。 映射方式 内存到cache的映射方式,大致可以分为三种,分别是:直接映射

2021-11-21 11:09:50 2127

2127 关于Cache的其它内容 上面我们所描述情况,在访问cache前,已经将虚拟地址转换成了物理地址,其实,不一定,也可是是虚拟地址直接访问cache,倒底是使用物理地址还是虚拟地址,这就是翻译方式

2021-11-21 11:12:14 2075

2075 Bbuffer 与 Cache 非常类似,因为它们都用于存储数据数据,被应用层读取字节数据。

2022-07-01 10:44:24 2651

2651 电子发烧友网站提供《SALELF 2 MCU Flash Cache指南.pdf》资料免费下载

2022-09-26 15:12:00 0

0 本文会从结构,原理以及应用方面对 MPU 和 Cache 进行分析,主要目的是希望读者对 Cache 有基本的了解,在具体的实际应用中,使用带有一级 cache 的 MCU 时,避免常见的错误。

2022-09-28 11:05:20 0

0 对cache的掌握,对于Linux工程师(其他的非Linux工程师也一样)写出高效能代码,以及优化Linux系统的性能是至关重要的。简单来说,cache快,内存慢,硬盘更慢。在一个典型的现代CPU中比较接近改进的哈佛结构,cache的排布大概是这样的:

2022-10-18 09:01:12 1195

1195 CPU register的速度一般小于1ns,主存的速度一般是65ns左右。速度差异近百倍。在硬件上,我们将cache放置在CPU和主存之间,作为主存数据的缓存。

2022-11-16 11:17:32 589

589 由于写入数据和读取指令分别通过 D-Cache 和 I-Cache,所以需要同步 D-Cache 和 I-Cache,即复制后需要先将 D-Cache 写回到内存,而且还需要作废当前的 I-Cache 以确保执行的是 Memory 内更新的代码

2022-12-06 09:55:56 1163

1163 现代CPU,通常L1 cache的指令和数据是分离的。这样可以实现2条高速公路并行访问,CPU可以同时load指令和数据。当然,cache也不一定是一个core独享,现代很多CPU的典型分布是这样的,比如多个core共享一个L3。比如这台的Linux里面运行lstopo命令:

2022-12-06 10:38:50 458

458 当CPU想要访问主存中的元素时,会先查看Cache中是否存在,如果存在(称为Cache Hit),直接从Cache中获取,如果不存在(称为Cache Miss),才会从主存中获取。Cache的处理速度比主存快得多。

2022-12-12 09:17:51 469

469 L1 Cache和L2 Cache通常和处理器是在一块实现的。在SoC中,主存和处理器之间通过总线SYSBUS连接起来。

2023-01-08 10:56:03 566

566 占用非常大的面积,大概在一半以上,而且一个好的 Cache 的设计复杂度非常高,可能比较 CPU 的 Pipeline 还要复杂。这里要考虑成本,设计复杂度,或者其他方面的考虑。你知道 L1

2023-01-11 09:34:49 837

837 所以在linux初级开发者接触cache时,脑海里会不自觉的思考:硬件行为,都是被ICer设计好的;所以他们也并没有深究cache的层次结构,也没有继续挖掘cache和驱动软件的千丝万缕的关系,脑海里想象的拓扑图,大致是这样:

2023-03-02 10:34:48 556

556 Cache被称为高速缓冲存储器(cache memory),是一种小容量高速的存储器,属于存储子系统的一部分,存放程序常使用的指令和数据。

2023-03-06 15:05:31 2879

2879 Cache存储器也被称为高速缓冲存储器,位于CPU和主存储器之间。之所以在CPU和主存之间要加cache是因为现代的CPU频率大大提高,内存的发展已经跟不上CPU访存的速度。在2001 – 2005

2023-03-21 14:34:53 755

755

在学习Spring Cache之前,笔者经常会硬编码的方式使用缓存。

2023-05-11 17:40:23 350

350

按照数据关系划分:Inclusive/exclusive Cache: 下级Cache包含上级的数据叫inclusive Cache。不包含叫exclusive Cache。举个例子,L3 Cache里有L2 Cache的数据,则L2 Cache叫exclusive Cache。

2023-05-30 16:02:34 418

418

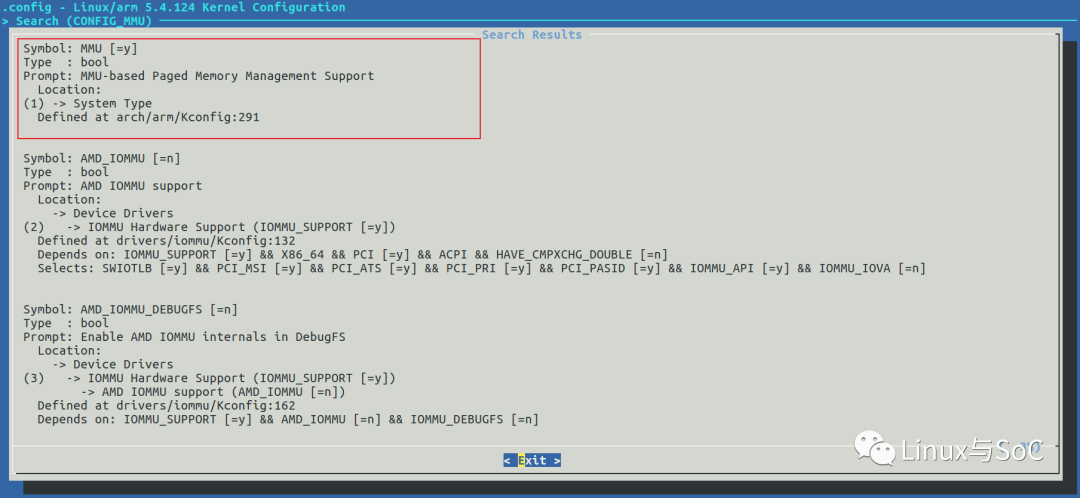

build_mem_type_table()函数的功能是获取当前CPU的CACHE类型,据此初始化mem_type。

2023-06-05 15:03:49 816

816

CACHE 的一致性 Cache的一致性有这么几个层面 1. 一个CPU的icache和dcache的同步问题 2. 多个CPU各自的cache同步问题 3. CPU

2023-06-17 10:38:26 911

911

Cache对性能的影响首先我们要知道,CPU访问内存时,不是直接去访问内存的,而是先访问缓存(cache)。 当缓存中已经有了我们要的数据时,CPU就会直接从缓存中读数据,而不是从内存中读。 CPU

2023-10-04 15:31:00 395

395

LRU(Least Recently Used)算法:该算法会跟踪每个cache line的age(年龄)情况,并在需要时替换掉近期最少使用的cache line。

2023-10-08 11:10:05 433

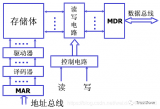

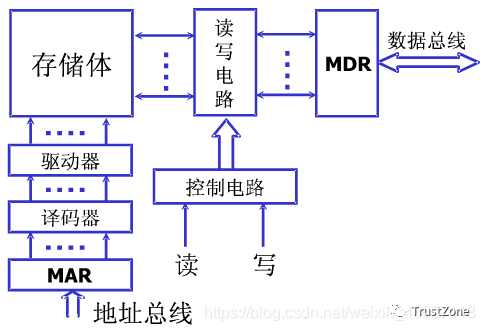

433 Cache是位于CPU与主存储器即DRAM(Dynamic RAM,动态存储器)之间的少量超高速静态存储器SRAM(Static RAM),它是为了解决CPU与主存之间速度匹配问题而设置的,不能由用户直接寻址访问。

2023-10-17 10:37:47 451

451

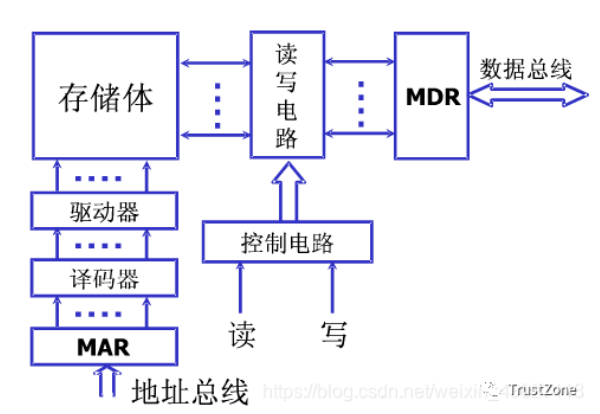

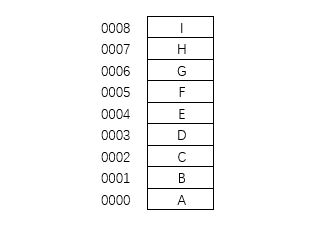

在cache存储系统中,把cache和主存储器都划分成相同大小的块。 主存地址由块号B和块内地址W两部分组成,cache地址由块号b和块内地址w组成。 当CPU访问cache时,CPU送来主存地址

2023-10-31 11:21:36 453

453 根据不同的分类标准可以按以下3种方法对Cache进行分类。 •1)数据cache和指令cache •● 指令cache:指令预取时使用的cache。 •● 数据cache:数据读写时使用的cache

2023-10-31 11:26:31 371

371

“锁定”在cache中的块在常规的cache替换操作中不会被替换,但当通过C7控制cache中特定的块时,比如使某特定的块无效时,这些被“锁定”在cache中的块也将受到相应

2023-10-31 11:31:21 314

314 具有Cache的计算机,当CPU需要进行存储器存取时,首先检查所需数据是否在Cache中。如果存在,则可以直接存取其中的数据而不必插入任何等待状态,这是最佳情况,称为高速命中; 当CPU所需信息不在

2023-10-31 11:34:46 403

403

提高高速缓存命中率的最好方法是尽量使Cache存放CPU最近一直在使用的指令与数据,当Cache装满后,可将相对长期不用的数据删除,提高Cache的使用效率。 为保持Cache中数据与主存储器中数据

2023-10-31 11:43:37 532

532 Cache和存储器一样具有两种基本操作,即读操作和写操作。当CPU发出读操作命令时,根据它产生的主存地址分为两种情形:一种是需要的数据已在Cache中,那么只需要直接访问Cache,从对应单元中读取

2023-10-31 11:48:08 560

560 使用Cache的必要性 所谓Cache即高速缓冲存储器,它位于CPU与主存即DRAM之间,是通常由SRAM构成的规模较小但存取速度很快的存储器。 目前计算机主要使用的内存为DRAM,它具有价格

2023-10-31 11:53:54 334

334

正在加载...

电子发烧友App

电子发烧友App

评论