由RISC-V和开源硬件的领导者SiFive公司主办,灿芯半导体和《中国集成电路》杂志社联合承办的SiFive 2018上海技术研讨会成功召开。会后,SiFive CEO Naveed Sherwani博士、首席架构师Krste Asanovic 博士(Krste同时是UC Berkeley教授和RISC-V基金会主席),运营副总裁Shafy Elthouky博士和产品副总裁Jack Kang接受了半导体行业观察的专访,深入分享了RISC-V发展趋势、生态系统及SiFive的商业模式、市场前景。

开源架构的发展如火如荼,RISC-V更是炙手可热,放眼全球,已然掀起一场市场化驱动、发烧友助推的产业变革:

全球第一大硬盘产商西部数据(Western Digital)将以每年10亿到20亿颗的预期来推动RISC-V,逐步完成全线产品迁移到RISC-V定制架构;

MicroSemi提供基于Risc-V+Linux+CNN加速器的AI解决方案;

印度政府则大力资助基于RISC-V的处理器项目,使RISC-V成为了印度的事实国家指令集;

RISC-V基金会的会员已经增加到150多个,大学、科研院所和企业大量使用或评估基于RISC-V的应用,参与度之高,覆盖面之广,盛况空前;

指令集架构的生态链正在成长和完善,工具链、RTOS/Linux操作系统的移植等工作都取得关键突破。

那么,RISC-V的魅力究竟何在?

无论模块化指令集“能屈能伸”,还是甩掉向后兼容历史包袱“无病一身轻”,再到40多条基本指令“大道至简”,且使用BSD License开源协议彻底开放,RISC-V的种种优势,宛如指令集纷繁万象中的一股春风。

一.碎片化?在质疑中快速成长

然而,正如Intel主宰数据中心领域,ARM在移动领域一骑绝尘,针对不同应用端的处理器架构和生态系统,RISC-V作为后起之秀,需要证明其应用和市场前景,先得回答几个问题:

1.RISC-V开源架构是否会遇到碎片化引起的兼容性问题?

Asanovic博士指出,从RISC-V设计之初,就采用了基础指令集与扩展指令集的方式, 求同存异,只标准化最通用场景,以兼顾“简单高效”和“灵活多变”。

基础指令集只包含40多条指令,但已经可以用于实现一个具备定点运算和特权模式等基本功能的处理器。扩展指令集则提供了一些常用的原子操作指令、浮点运算指令等,用户也可以需要自身需求进行自定义。

在应用端趋于碎片化的物联网时代,我们需要多样化的定制处理器和芯片;而需求越差异化,指令集碎片所带来的影响也越小。并且,RISC-V基金会制定了一系列规范来保证兼容性,据Asanovic博士透露,想要使用RISC-V商标的公司必须先通过兼容性测试,且当某项功能变得非常通用,提出的公司可以向基金会申请标准化,从而避免不必要的指令分叉和重复开发浪费。

2.RISC-V的设计水平或者说Silicon Performance到底如何?

指令集,是软件和硬件的接口,在兼容性层面来说是重要的一环;但是从性能来讲,越是复杂和高性能的处理器,指令集优劣所带来的影响就越小。多年来的经验和事实告诉我们,指令集架构本身和性能的关系并不大。

Esperanto公司创始人David Ditzel也曾经评估过RISC-V的性能,最后的评测的结果是,和ARM/MIPS/SPARC相比,毫不逊色,benchmark的结果差距在1%之内。

芯片是一个紧密耦合环环相扣的系统工程,指令集架构、RTL、物理实现、制造、封装,只有这其中每一个环节都能得到重视和优化,才能保证最终产品的性能。所以当大家讨论RISC-V的性能,更多是要看有没有足够多的公司投入,足够强的设计团队在这个生态中有所探索。

“对于小公司来说,RISC-V实施简单,这样就使得开启许多不同的RISC-V内核成为可能,也带来了市场上的多样性。”Sherwani博士告诉半导体行业观察,处理器设计工程团队可以从多个供应商(甚至是开放源码)中找到一个符合他们需求的版本,在此基础上可以进行定制,整个设计流程也大大加速。

过去,指令集架构的生态系统的成长是个很复杂和漫长的过程,堪称“十年磨一剑”。同时,还需要强有力的领跑者带动市场,就像x86有了Windows,x86才真正建立起生态系统,然后是Linux; Arm有谷歌Android才能造就现在的成功。

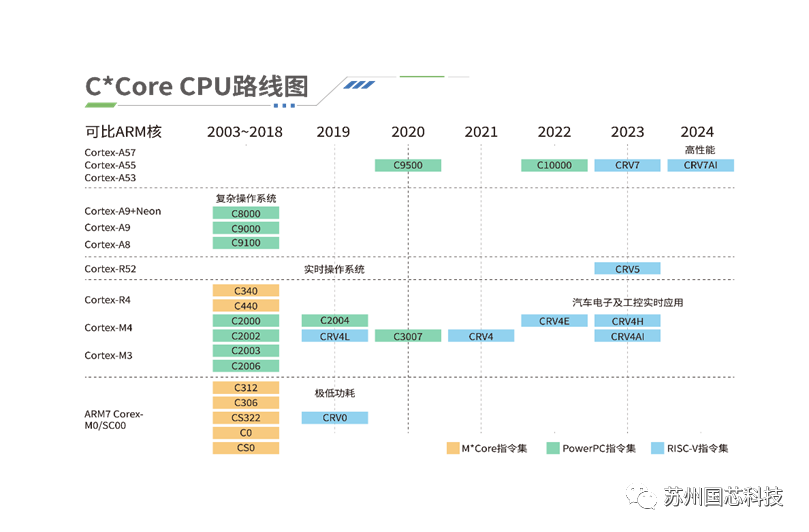

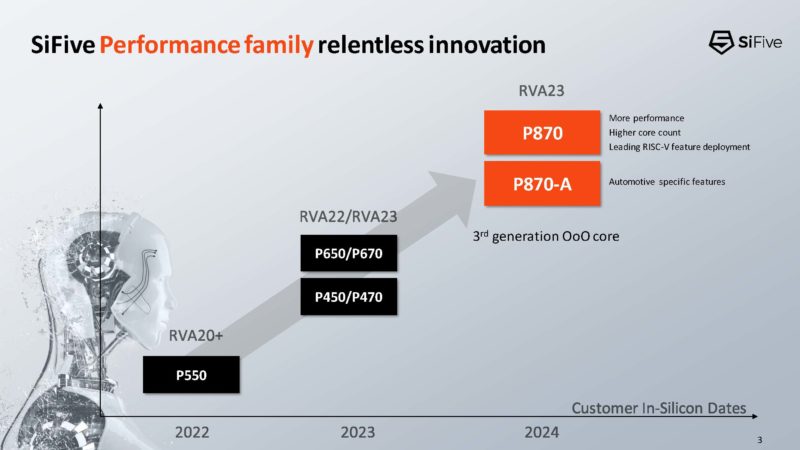

对于RISC-V而言,并非一切都已构建完备,Asanovic博士补充道,但是RISC-V的发展速度之快超出想象。ARM在2004年推出首个Cortex核,经过14年的发展才形成了整个Cortex 核系列;RISC-V在2到3年的短短时间内,将达到Cortex 核的覆盖度。

Sherwani博士同时也认为, 开源硬件和传统硬件完全可以并肩共存,各自面向不同的应用场景。 ARM、x86、RISC-V仍然会长期共存,但高墙会被抹平。

二、芯片设计方法的变革

当目标是10,000次流片,怎样才能实现Mission Impossible?

Sherwani博士回顾他在芯片行业摸爬滚打数十年的经历,他告诉半导体行业观察,坦率而言,能够精通很多复杂的工具的工程师,其实并不多。假设,我们想在中国进行10,000次流片,如果每次流片都需要30位资深工程师花费数月,实现这个目标的可能性就微乎其微。

为了突破这一资源瓶颈,SiFive为我们设想了这样一种可能,设计一款芯片,但不必搭建服务器,不用安装EDA工具,不需FPGA验证,甚至不需要版图和验证团队!如果那一天真的到来,对于目前的设计流程和工作方式都将是一种颠覆。

而SiFive就在引领这样一场革命。

Kang指出,很多客户是从应用端出发,由于最终想要做成一款终端产品,为此定制一款芯片。他们其实并不想专门成立一个设计团队,并学习如何去使用各种复杂的CAD工具。他们更想要的其实是在GUI界面上,通过几个简单的按键操作,就能够敏捷开发一款芯片,快速评估芯片的性能、面积和功耗。

SiFive SCS是运行在云端的软件和服务, 跳出了单纯计件卖IP的窠臼,提供基于“云”进行IP授权和芯片定制化的SaaS平台。通过图形化网页交互界面,客户可以在线选择CPU核的配置,选择合适的IP, 生成前端代码,进行验证,开展后端设计,tapeout, 产生文档等等; 这一切,都在云端实现。 Elthouky博士介绍,通过“Design Share”策略,SiFive整合第三方IP供应商将IP数据“上云”,同时整合开源/商业EDA软件上云,在云端完成芯片实现chisel到RTL的流程。

客户可以按月、按季度付费使用这个SaaS平台,可快速生成数个不同的IP。这种云模式,有望解决服务器、存储、EDA软件、IP的整合、知识产权的保护、软件集成等多个问题,针对小公司和初创芯片公司而言,成本上有可能出现巨大的优势。

通过云端的芯片定制流程进行快速验证后,实际上还有很多需要解决的问题,包括IP集成、制造、封装和测试等等。为了让客户能够很快地拿到一些样片,然后再导入量产,SiFive还特别提出了“设计工厂” (Design Factory)的理念,通过软件概念上的Template(物理实现可能会非常不同),结合验证、综合、PR等自动化流程,快速实现设计。为了向客户交付快速样片,SiFive将制造、封装、测试甚至物流等产业链必备环节服务也考虑在内,但就现状来看,这部分需要投入的资源较多,预期需要引入更多的合作伙伴。

三.SiFive在中国

在谈及SiFive的市场战略时,Sherwani博士强调,SiFive的目标并非与市面上的某一种或几种核进行竞争,而在于针对客户的需求,提供优质、灵活的处理器核,和相应的定制化服务。

那么,长远来看,SiFive的核心盈利来源是什么?

Sherwani博士和Asanovic博士均认为, SiFive的长期盈利点来自于终端芯片销售。

我们看到,IP市场的体量,只占全球半导体销售额中很小的一部分。SiFive选择终端芯片销售作为长期赢利点,也正是源于此考量。客户看到的价格,并不区分单独IP或者说单独SaaS服务,而是整个芯片的价格。尽管芯片的起量需要一个缓慢的过程,但一旦达到投资回报甜蜜点,预期将带来可观的利润。

SiFive同时宣布,SiFive将对全世界的大学以及世界上最贫穷的50个国家免费提供处理器核。作为一家商业机构,Sherwani博士指出,SiFive以盈利为目的,但在盈利之上有更高层次的追求。SiFive认为世界上的所有国家都有权拥有自主可控的CPU,RISC-V作为开源指令集是一个很好的选择。而就中国市场而言,SiFive在这里看到了足够大的市场,同时也希望能够为中国今后十年、二十年所需要的处理器,搭建好基础设施。

在我们的邻国印度,RISC-V已经成为了印度的事实国家指令集。印度于2011年开始实施处理器战略计划,在全国范围资助2-3个研制处理器的项目,研制多款基于RISC-V指令集的开源处理器核,累计获超过上亿美元的经费支持。

此前,中科院计算所包云岗教授曾多次呼吁政府重视和支持RISC-V研究。对此,Sherwani博士也对未来中国政府将在RISC-V领域加大投入,持非常乐观的态度。

Sherwani博士同时还透露了计划在中国建立一家合资公司的规划。他提出,和SiFive在美国的融资组合类似,这家合资公司会从多方获取资金来源,以确保以相对去中心化的方式来运作,也能够让不同的玩家一起加入,共同协作,一起成长。

电子发烧友App

电子发烧友App

评论