1 CPUCPU(Central Processing Unit),是一台计算机的运算核心和控制核心。CPU由运算器、控制器和寄存器及实现它们之间联系的数据、控制及状态的总线构成。主要功能是解释

2021-11-02 07:06:45

1.CPU(Central Processing Unit),是一台计算机的运算核心和控制核心。CPU由运算器、控制器和寄存器及实现它们之间联系的数据、控制及状态的总线构成。差不多所有的CPU的运作

2021-11-11 08:29:27

CPU、MPU、MCU、SOC之间有什么联系?区别是什么?

2021-09-26 06:08:49

CPU和GPU之间有什么区别?

2021-11-05 07:58:29

cpu与外部设备之间如何通信?

2021-12-06 06:31:47

按照手侧中的描述,禁止比较器延迟采样功能,然后选择对应的比较器输出到测试引脚,使能PWM和和比较器,手动转动电机使比较器值翻转,测量PWM输出和比较器输出延迟。我通过使用U上和V下,然后打开W通道

2022-11-08 14:18:36

测量中断响应延迟

2022-12-12 06:00:51

你好,我知道其他一些人要求这个旧版本,但我希望它现在正在工作。我需要测量两个通道之间的延迟。我可以在前面板上执行此操作,然后我可以将其设置为SCPI,但我无法测量SCPI的延迟并返回测量值。我发送

2018-10-09 15:04:43

TI专家,各位朋友:

我想把OMAPL138 CPU核心电压由1.2V提高到1.3V我该怎么做呢?这个可以修改寄存器直接配置吗?我翻了下手册,没找到这方面的内容。

2018-06-21 05:23:34

想用PWM调节CPU的核心电压,请问有谁知道图里的R3,R4,R5和C1的计算方法?

2019-03-11 10:30:25

STM32F103C8T6核心板 ARM 32位 Cortex-M3 CPU 22.62X53.34MM

2023-06-13 18:18:05

ZYNQ核心板 DEVB_45X60MM 5V

2023-03-28 13:06:25

iMX6UL核心板和开发板之间的以太网RMII接口,将CPU的ENET1_TX_CLK信号直接连到PHY芯片(KSZ8081RNB)的X1管脚了,此处未使用外部时钟;我有个疑问,这里CPU的ENET1_TX_CLK信号是可以配置成50Mhz时钟输出吗?

2022-01-11 07:27:22

)//*******************************************************************************************//DelayMs使用核心定时器//void DelayMs(WORD延迟

2019-08-29 06:31:44

STemWin522_CM3_Keil.libSTemWin522_CM3_OS_Keil.libSTemWin522_CM3_IAR.aSTemWin522_CM3_OS_IAR.a同样核心的不同库文件之间有什么区别?

2020-03-23 04:36:58

是否可以控制核心之间的GPIO? 在 CYT2CL 中,有两个核心 CMO 和 CM4。 我需要在两个内核之间切换一个 GPIO 引脚。

2024-03-06 07:15:17

我在设计中需要iodelay1块,但是从模拟开始,我在ny datain和dataout之间的延迟并不像预期的那样。它显示没有我的cnt值的延迟。请帮我解决这个问题。

2020-06-16 07:02:13

你好我想知道很多核心电压我可以达到没有我的CPU损坏。我目前正在使用它在1.39 v(visibile in cpuz)i7 965 EXTREME(co)on asus p6t deluxe

2018-10-19 14:19:34

我想在两个STM32之间来回发送消息。可能是STM32F407VET6,但如果我能尝试一些简单的东西(STM32F103C8T6),那就太好了。我的要求:往返延迟时间:对于有效载荷大约为8字节

2018-09-28 13:49:00

如何使用VHDL仿真器确定输入变化与输出相应变化之间的最大延迟?

2020-03-27 10:09:54

我想在输出'b'和'a'之间插入一个延迟。这样我就能看到范围内这两个信号之间的100ns时移。我该如何编写时序约束?谢谢,-n以上来自于谷歌翻译以下为原文Consider the code below

2019-01-11 11:19:36

大家好,我是 STM32 MCU 的新手。我正在尝试生成 PWM 并尝试即时修改并且它有效。但我的要求是在两个脉冲之间有一个时间延迟,并且它不应该在任何边沿上相互对齐。请查看照片以了解预期的输出

2022-12-23 09:27:44

地计算出两个天线之间的延迟,但是我不清楚当滤波器具有以1575 MHz为中心的窄带宽时如何测量延迟 - 当可用带宽很大时,只能使用时域选项狭窄。可以使用端口扩展吗?我怀疑没有,因为他们认为延迟是50

2018-11-01 11:48:21

在ESG或MXG上,如何调整基带和RF输出的IQ波形之间的时序延迟?我希望能够将这些调制波形与它们之间的指定延迟同步。 以上来自于谷歌翻译 以下为原文On either the ESG

2019-07-23 16:22:11

对于群延迟测量(PNA-X N5242A),平滑开启和将平滑点设置为3并将群延迟温度点设置为3之间的区别是什么? TIA 以上来自于谷歌翻译 以下为原文For a group delay

2019-04-30 09:47:14

本文从精简结构,同时兼顾精度的角度出发,提出一种基于时间测量芯片TDC-GP2来精确测量IGBT导通延迟时间系统,用于测量IGBT的导通延迟时间,实现简单且成本低的一种较为理想的测量方案。

2021-05-14 06:07:09

的ISERDESE2,除以8,NETWORKING模式。然后我将内部逻辑“仅”运行在125 MHz,这似乎更易于管理。我不太确定的是通过所有ISERDES的500 MHz时钟路由。在所有输入之间的时钟偏差/相位延迟

2020-08-14 09:11:32

检测时,可通过测量亮度延迟线输入端与输出端之间的电阻值是否正常来判断其是否损坏。用万用表R×10 kΩ档测量亮度延迟线输入端与输出端之间的电阻值(正常值为30~40 Ω)。若测得阻值为无穷大,则表明

2021-05-24 07:43:48

我刚刚下载了不确定度计算器并绘制了三种不同Sii的群延迟精度。我想看看不匹配的终端如何影响群延迟测量的准确性:它们似乎几乎没有差别。不确定性计算器绘制了组延迟的精度(ns)与孔径(MHz)的关系曲线

2018-11-05 10:40:15

核心板与底板之间有好的连接柱推荐吗?谢谢有现成的淘宝店最好

2019-06-21 09:58:12

我在目前的文档中没有找到明确的答案:是每个核心都有独立的FPU,还是核心之间共享?

2023-03-01 08:33:56

请问主板与CPU之间对应的关系是什么?

2021-10-25 09:27:31

高温55°试验时,温枪测量eMMC表面温度90~95°,CPU表面85°,使用中温度太高了,且使用中会有板子因高温死机的情况。请问如何降低功耗。

2022-01-05 07:10:37

PIC16F1459:我需要从同一信道(如AN3)读取许多10位ADC:我的问题是在读取ADC之间需要延迟的最小uS是多少?我设置TAD= 1U。什么是典型的采样开关(SS)的行动当

2020-04-29 12:22:20

嗨,大家好,我向时钟向导提供50 Mhz输入,并使用MMCM方案生成80 MHz方案。在模拟中,我看到输入时钟和生成的时钟之间存在延迟。这种延迟是什么?有什么办法可以控制这种延迟吗?任何建议都会非常

2019-04-26 13:01:43

测量,CPU0 - http 服务器,连接到 wifi 等.数据测量目标 - 10 kHz,无抖动,测量时间 - 单核 RAM 消耗的 20-30% 左右,MAX 优先级(数据测量不能被任何

2023-04-13 07:13:41

产品简介:采用Intel Tiger Lake-U 系列处理器,支持双通道DDR4 SO DIMM内存,最大容量可达64GB,配备CONN1+CONN2两个高速接口,可实现一专多能,核心板专搭载

2021-11-19 14:21:23

产品简介:采用Whiskey Lake - U系列处理器,支持双通道DDR4 SO DIMM内存,最大容量可达64GB,配备CONN1+CONN2两个高速接口,可实现一专多能,核心板专搭载嵌入式

2021-11-19 15:08:12

cpu温度测量软件:一个测试软硬件系统信息的工具32位的底层硬件扫描使它可以详细的显示出PC硬件每一个方面的信息.支持上千种(3400+)主板支持上百种(360+)显卡支持对

2008-07-21 15:18:09 94

94 CPU核心 核心(Die)又称为内

2009-12-17 10:52:08 323

323 什么是CPU核心

核心(Die)又称为内核,是CPU最重要的组成部分

2009-12-17 10:57:07 1067

1067 CPU核心工作性能

CPU核心概述

2009-12-17 10:59:24 321

321 双核cpu

双核就是2个核心,核心(Die)又称为内核,是CPU最重要

2009-12-17 11:01:49 923

923 英特尔CPU核心 Tualatin 这也就是大名鼎

2009-12-17 16:57:13 328

328 AMD CPU核心 Athlon XP的

2009-12-17 17:02:51 774

774 CPU双核心简介

&

2009-12-17 17:07:52 678

678 CPU核心技术 核心(Die)又称为内核,是CPU最重要的组

2009-12-18 09:54:16 1229

1229 CPU核心类型 核心(Die)又称为内核,是CPU

2009-12-24 09:58:03 507

507 Intel CPU核心简介

2009-12-24 10:00:44 942

942 AMD CPU核心简介 Athlon

2009-12-24 10:08:00 833

833 CPU双核心类型有哪些? &nbs

2009-12-24 10:09:42 944

944 基于对群延迟测量方法优化的目的,采用数字信号处理的方法,设计了计算群延迟的计算机算法,将一部分测量工作转化为计算机的计算工作,从而简化了测量方法,提高了测试效率。

2012-04-19 17:46:57 21

21 一种利用高精度时钟测量中断延迟的方法_贺俊

2017-03-19 11:46:13 1

1 OK,关联性介绍到这里,回到我们的主题。CPU的单核工作模式不用小编啰嗦了,一个人干活,与别人无关。干得快慢,好坏只与自己有关(工作的主频,缓存大小,CPU架构,总线频率,内存大小,磁盘IO快慢等)。

2018-07-18 12:40:00 6851

6851 这又是一次比拼核心数量的游戏。然而这次,这种竞争已经达到了两位数。当台式机及笔记本 CPU 仍然在四核心悠哉游哉之时,AMD及其对手Intel正在服务器及企业市场大展拳脚。就在Intel宣扬了其定于

2018-06-07 17:13:00 1679

1679 核心又称为内核,是CPU最重要的组成部分。CPU中心那块隆起的芯片就是核心,是由单晶硅以一定的生产工艺制造出来的,CPU所有的计算、接受/存储命令、处理数据都由核心执行。各种CPU核心都具有固定的逻辑结构。

2018-02-12 10:42:26 36866

36866

你知道单片机、ARM、DSP都是CPU吗,它们之间又有什么不同,小编进行了整理和编辑。

2018-11-02 17:38:39 12864

12864 CPU核心数多有两个好处:一是可以在多任务同时运行时降低CPU的占用率,提升负载能力,减少卡顿的发生;二是可以对支持多线程的程序进行大幅度的提速,比单纯的提高频率要强得多。但是这并不是说CPU核心

2019-01-21 17:08:15 41838

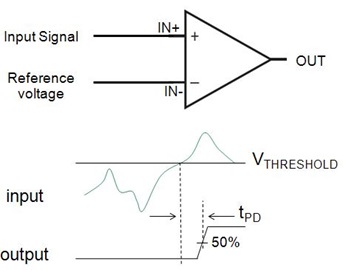

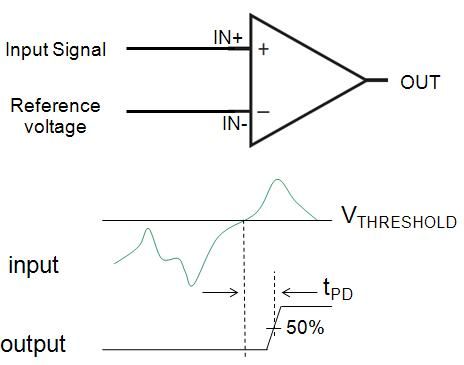

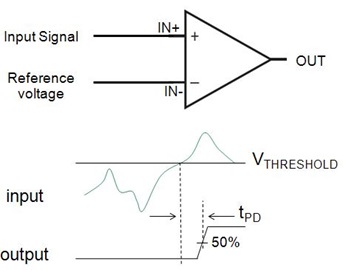

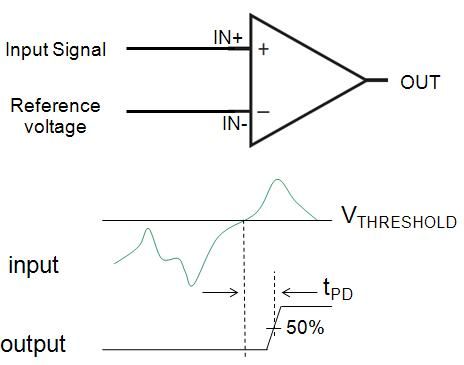

41838 达输出之前通过内部电路传播(传播)时存在延迟。重要的是要注意传播延迟定义为输出达到输出值的50%而不是完整值的点。此指定与输出负载相结合,是导致电路测量延迟时间长于预期延迟时间的几个因素之一。

2019-04-09 09:19:00 16007

16007

CPU有这么多系列,不同系列之间的性能差别又这么明显,那么它们的差别究竟在哪呢?其实就在核心和线程的数量。

2019-11-19 15:31:06 12352

12352 在AMD的财务分析日上,AMD 透露将会升级其Infinity Fabric总线,不仅支持CPU-CPU以及GPU-GPU之间的连接,而且还将支持CPU-GPU之间的连接。

2020-03-09 14:24:31 2387

2387 CPU是中央处理器,是电脑的核心,所有需要在电脑中运行的软件都需要经过CPU的调度才能正常工作,经过多年的发展,CPU的核心数越来越多了,那么是不是核心数越多的CPU就越好呢?

2020-03-15 16:54:00 23592

23592 CPU核心供电电路为CPU提供核心工作电压,电路采用PWM脉宽调制的方式,而且是多相供电,因为CPU核心模块需要的工作电流比较大,多路供电可以满足CPU不同负荷的工作情况。同一芯片组的主板可以支持

2020-04-28 08:00:00 11

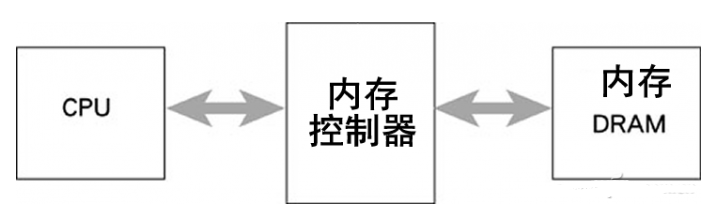

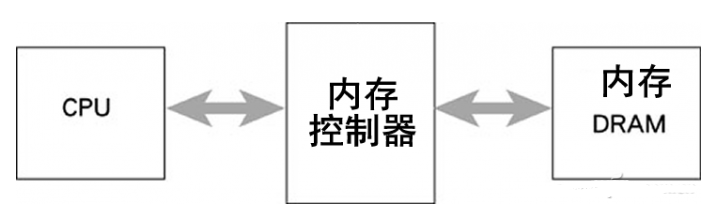

11 ,小编这就来解释一下。 内存就像一张草稿纸,里面写满了CPU、显卡、声卡等配件需要或者生成的数据,让这些配件可以随时取用。它的延迟也很好理解,就是这些数据从生成到写在内存上的间隔。不过咱们今天说的延迟不是内存自己的能

2020-09-09 10:53:06 7740

7740

前言:现在的CPU或SoC基本都是在单芯片中集成多个CPU核心,形成通常所说的4核、8核或更多核的CPU或SoC芯片。为什么要采用这种方式?多个CPU 核心在一起是如何工作的?CPU核心越多就一定

2021-01-06 11:35:12 14415

14415

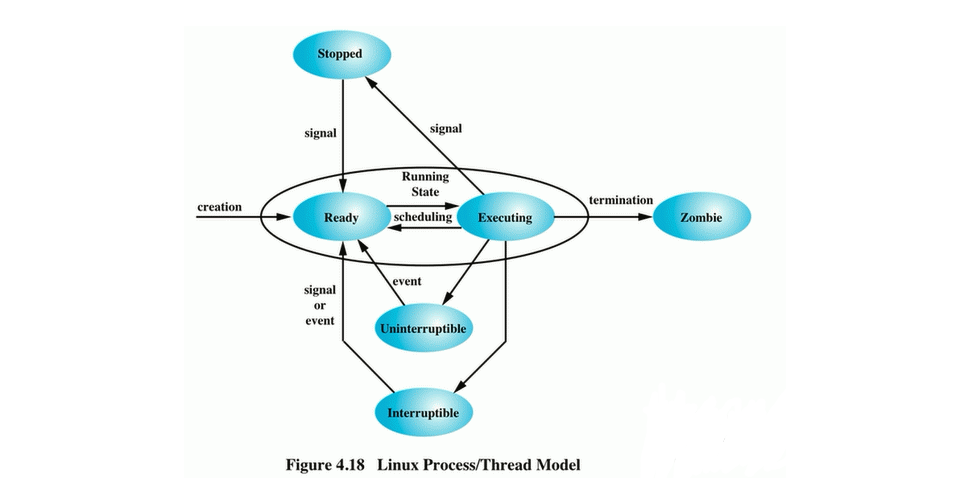

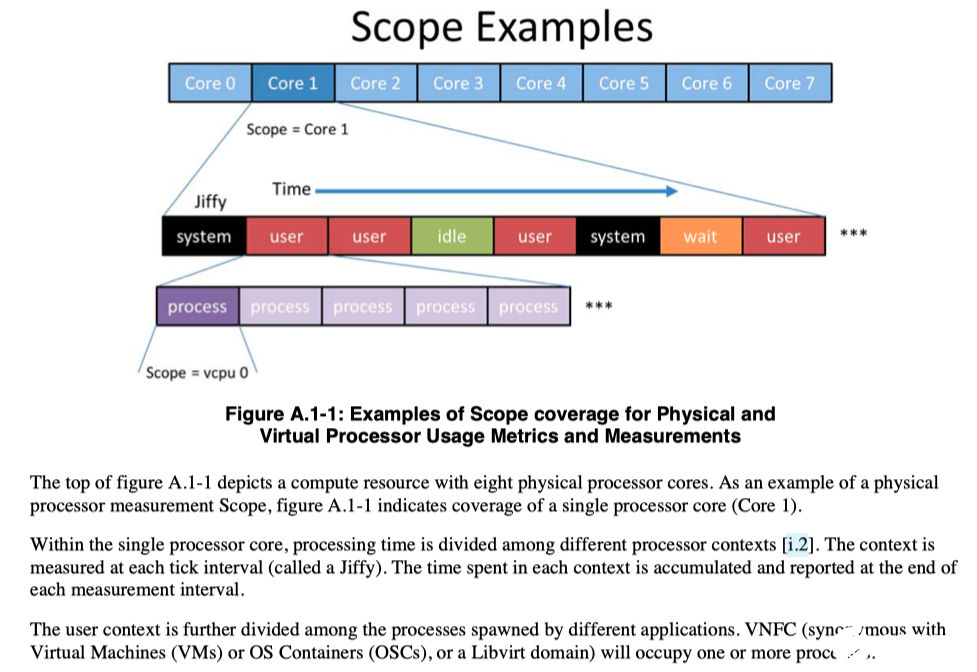

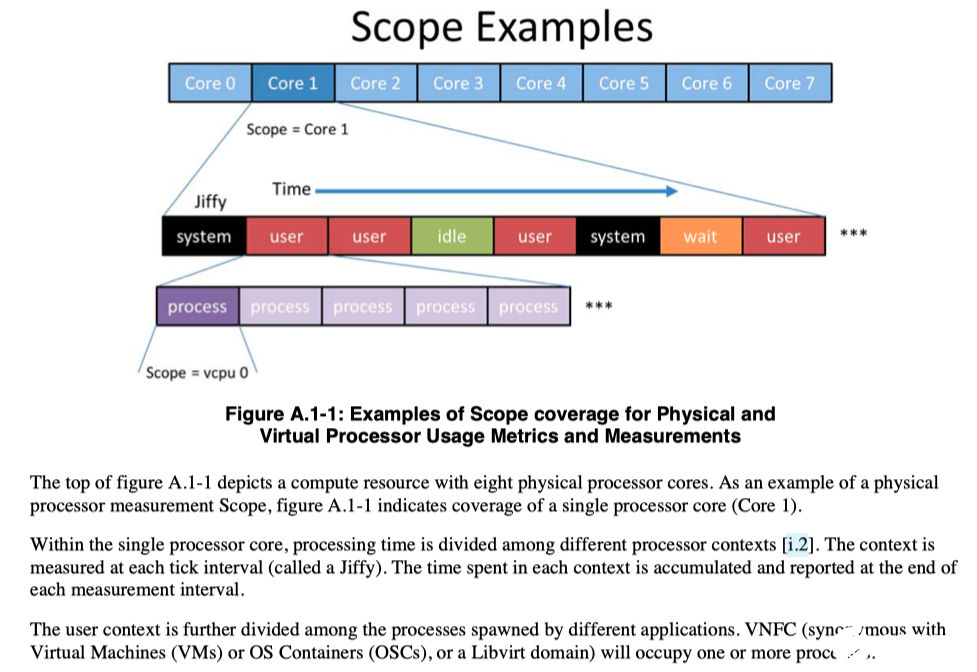

上面的图和文字摘自ETSI GS NFV-TST 008,呈现的是一个物理CPU注1能够被测量的几个资源维度和他们之间的对应关系。

2021-01-22 09:09:12 9229

9229

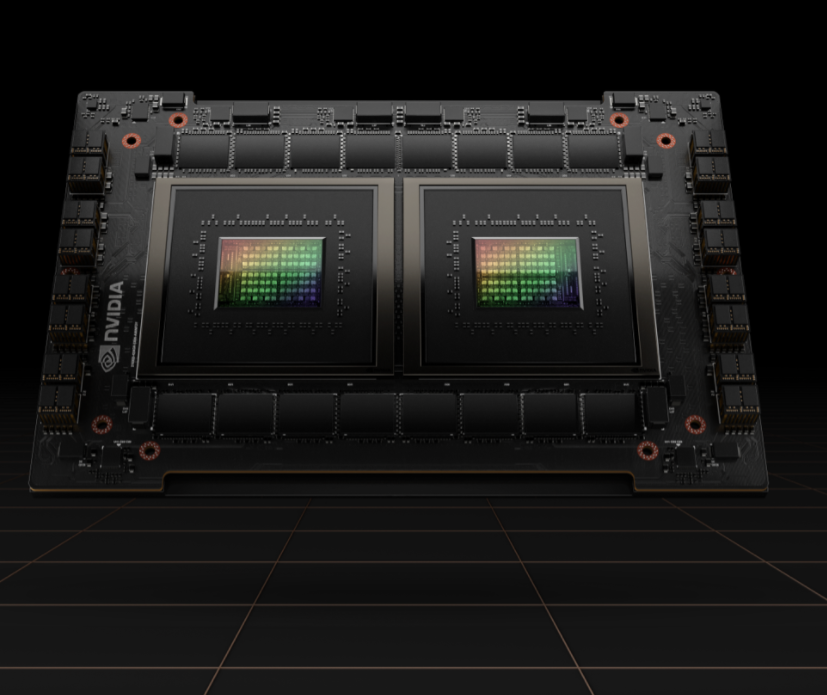

CPU缓存与内存延迟测试,相信大家都有所耳闻,但是GPU同样的测试却几乎没人做过。 ChipsAndCheese就做了一次特别的测试,对比考察了AMD、NVIDIAGPU架构的缓存、显存

2021-04-21 13:51:20 1701

1701 S7-300_CPU之间的PROFIBUS主从通讯配置说明。

2021-04-25 10:30:25 19

19 AN102-精确测量I/Q调制器中的相位和延迟误差

2021-04-25 19:04:28 8

8 (Central Processing Unit),是一台计算机的运算核心和控制核心。CPU由运算器、控制器和寄存器及实现它们之间联系的数据、控制及状态的总线构成。差不多所有的CPU的运...

2021-10-28 14:06:02 21

21 它们之间的关系CPU是最基本的存在,因为某些原因,在CPU的外部又包裹了部分附加功能,和CPU一起共同构成MCU、DSP、SOC等这些芯片,因此它们都是从CPU的基础上扩展而来,基本关系我们可以

2021-10-28 15:51:14 35

35 工控机CPU有单核、双核、四核、六核、八核等几种常见类型,下面派勤电子主要给大家讲讲工控机双核CPU和四核CPU两种类型之间有什么区别: 双核CPU:将两个物理处理器核集成到一个核中,这样做的优点

2021-12-03 11:47:09 1373

1373 NVIDIA Grace™ CPU 超级芯片由两个 CPU 芯片组成,它们之间通过NVLink®-C2C互连在一起。NVLink®-C2C 是一种新型的高速、低延迟、芯片到芯片的互连技术。

2022-03-23 11:25:41 1860

1860

MPU是Micro Processor Unit的缩写,指微处理器(这里要注意不是微控制器,很多人会把微处理器和微控制器混淆),微处理器通常代表功能强大的CPU(可理解为增强型的CPU),这种芯片往往是计算机和高端系统的核心CPU。

2022-07-05 10:50:41 3265

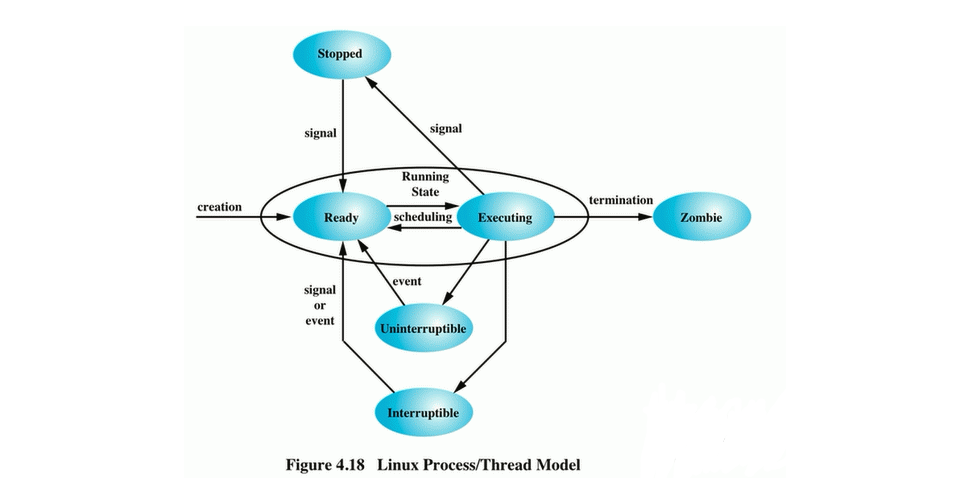

3265 本次圈定的性能指标是调度延迟,那首要的目标就是看看到底什么是调度延迟,调度延迟是保证每一个可运行进程都至少运行一次的时间间隔,翻译一下,是指一个 task 的状态变成了 TASK_RUNNING,然后从进入 CPU 的 runqueue开始,到真正执行(获得 CPU 的执行权)的这段时间间隔。

2022-08-01 11:08:11 2217

2217 每一个 CPU 核心都会有一个 idle 进程,idle 进程是当系统没有调度 CPU 资源的时候,会进入 idle 进程,而 idle 进程的作用就是不使用 CPU,以此达到省电的目的。

2022-10-14 09:28:09 1500

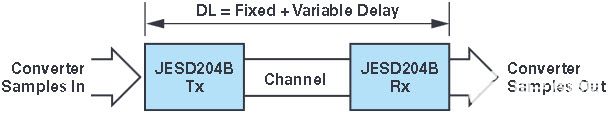

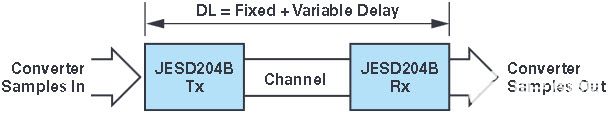

1500 JESD204B标准将确定性延迟定义为基于帧的样本到达串行发射器与基于帧的样本从串行接收器输出之间的时间差。延迟在帧时钟域中测量,并且必须以至少与帧时钟周期一样小的增量进行编程。延迟必须在上电周期之间以及任何重新同步事件之间重复。该定义如图 1 所示。

2022-12-21 11:11:20 2610

2610

内部电路(传播)时,存在延迟。需要注意的是,传播延迟定义为输出达到输出值的50%的点,而不是完整值。此名称与输出负载相结合,是可能导致电路测量的延迟时间长于预期延迟时间的几个因素之一。

2023-01-08 10:30:00 1968

1968

GPU是什么和CPU的区别?CPU是计算机的中央处理单元,可以以最小的延迟执行算术和逻辑运算。相比之下,GPU是一种嵌入式或外部图形处理单元,可以执行浮点运算以在高分辨率图像和视频中渲染多边形坐标。下面,小编将和大家一起讨论CPU和GPU之间的区别。

2023-05-25 17:23:14 1854

1854 以下是以表格形式提供的 CPU 和 GPU 之间的一些区别。

2023-06-06 15:51:34 627

627 1.概念CPU(CentralProcessingUnit)CPU(CentralProcessingUnit),是一台计算机的运算核心和控制核心。CPU由运算器、控制器和寄存器及实现它们之间联系

2022-09-30 09:51:32 11303

11303

CPU是电脑运行的核心部件,为避免其温度过高而配置了散热器,但由于两者之间存在间隙无法更好进行热量传递,因此它们之间需要有一个介质来解决这一问题,而芯片导热硅脂作为一项优异导热材料,使用它来作为CPU和散热器的中间介质非常合适。

2023-06-30 17:02:04 366

366 性能优化大师Brendan Gregg曾说:“性能问题可能来源于任何地方,包括系统中因你一无所知而不曾检查的地方”,CPU电源管理就是在性能优化过程中经常被忽略的地方。在这篇文章中,我们从一个简单的ping延迟出发,以小见大,一起了解CPU电源管理。

2023-07-07 15:08:32 488

488

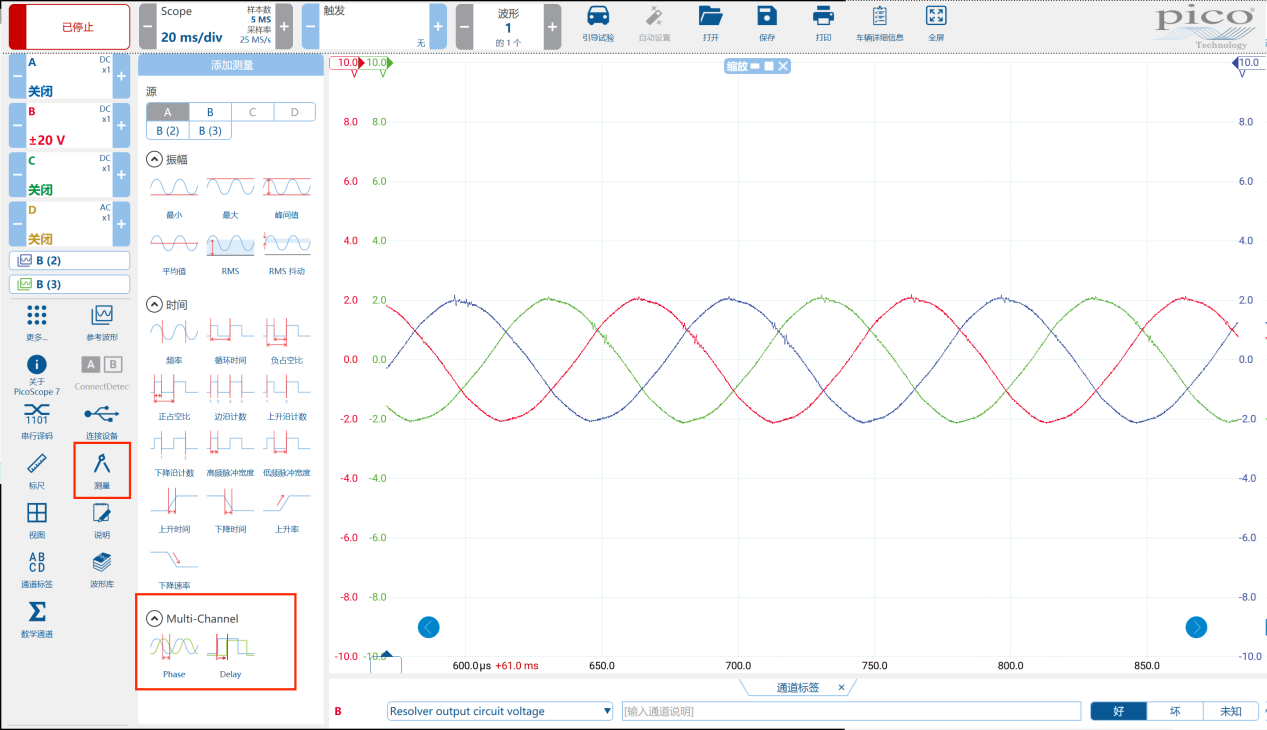

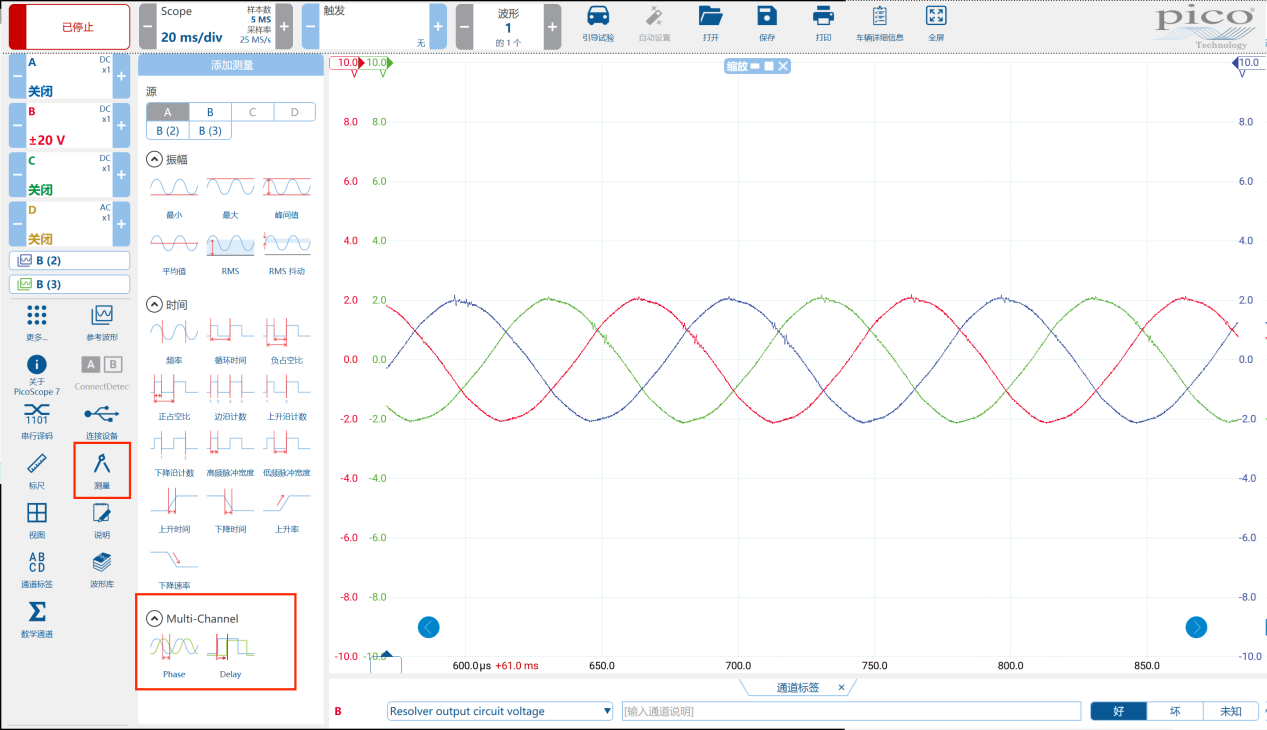

PicoScope 7 (PS7)软件增添了新的测量功能——测量相位之间的角度和延迟时间(图1)。 注:Phase- 相位;Delay - 延迟。 图1 相位测量 点击“Phase”,选择需要测量

2023-10-08 10:30:17 292

292

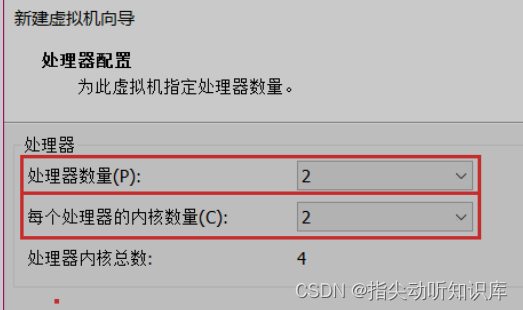

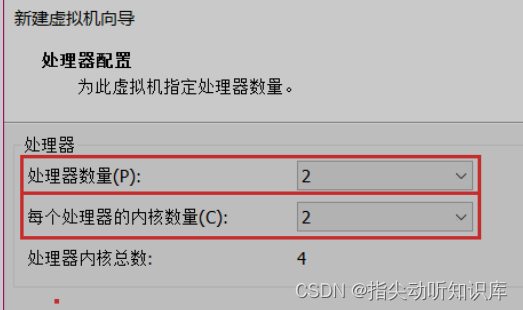

1 概念 1.1 背景 当看到以下一些名词,你是否感到过疑惑:他们之间到底有什么关系? CPU核心数、线程数、处理器数量、每个处理器的内核数量、处理器内核总数、逻辑核数… 在安装linux虚拟机

2023-11-24 16:22:01 549

549

以下是以表格形式提供的CPU和GPU之间的一些区别:中央处理器图形处理器CPU代表中央处理器。GPU代表图形处理单元。CPU是通用处理器。GPU是专用处理器。CPU更灵活,指令集更大,可以执行广泛

2023-12-14 08:28:03 318

318

CPU与GPU与TPU之间有什么区别? CPU(Central Processing Unit,中央处理器)是一种通用处理器,被用于各种计算任务,如操作系统运行、数据处理、算法运算等。它是计算机系

2023-12-15 10:10:27 2308

2308 如何测量差分探头的传播延迟呢? 差分探头的传播延迟指的是信号从输入端到输出端的传输时间。测量差分探头传播延迟的过程可以分为两个主要步骤:校准和测量。 一、校准差分探头 差分探头的传输延迟可以由同一

2024-01-17 11:32:17 238

238 CPU的主频和外频是计算机中两个重要的频率指标,它们分别代表了CPU内部和与外部组件之间的数据传输速率。这两个频率指标之间有着密切的关系,对计算机的性能和稳定性有着重要的影响。 首先,我们来具体了解

2024-02-03 16:50:13 642

642 CPU核心作为CPU(中央处理单元)的主要处理单元。该组件从计算机内存中读取并执行指令。每个核心一次只能运行一项任务,因此具有多个核心的 CPU 可以同时执行多个任务。这对于多任务处理和运行需要高处理能力的应用程序特别有利。

2024-03-04 17:09:23 224

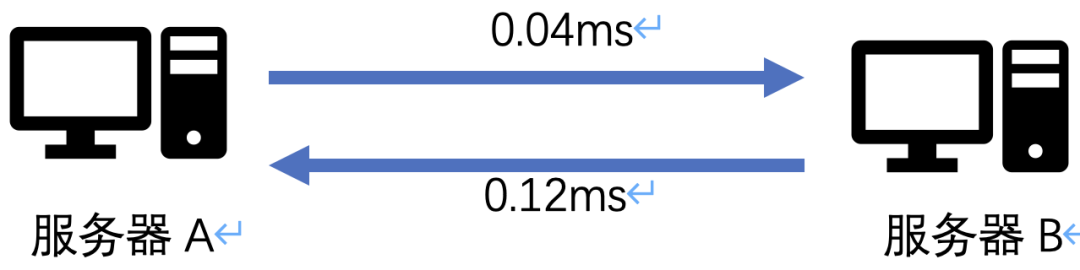

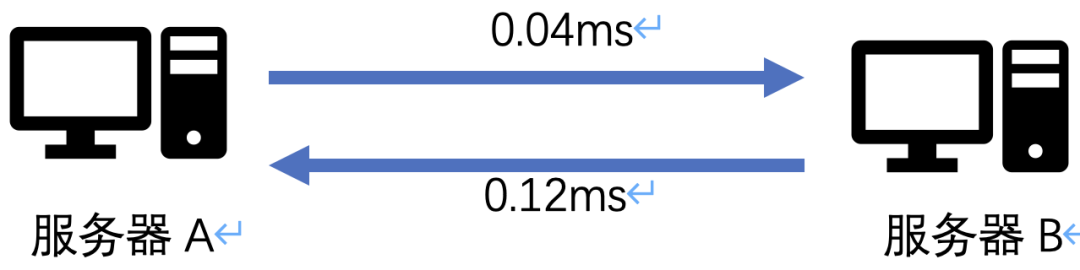

224 延迟其实就是你在请求后需要等待的时间,就像等待快递送到家门一样。来看个例子,更容易理解它是怎么运作的。

2024-03-07 11:38:04 366

366

电子发烧友App

电子发烧友App

评论