本帖最后由 一只耳朵怪 于 2018-6-22 09:54 编辑

大家好:138上DSP的ram里L1P,L1D,L2都分别有两个,个人理解L1P,L1D默认作高速缓存,L2为程序存储,关键是

2018-06-21 00:37:03

那样的话,L1 直接和 CCI 交互会很慢吧

2023-01-02 17:27:35

了中断通知core1,数据还在core0的L2,core1访问core0的L2来完成数据传输。我的疑问是:我的理解是对的吗?core1为什么可以访问core0的L2 RAM?

2018-06-25 06:16:40

您好,在2 级和3 级(L2 和L3)互连子系统中,提到“基本功能性的软件测试”,强烈建议使用基本功能性的引导时间软件测试,我查看Cortex-R4的手册,貌似没有L3系统啊,请问“基本功能性的引导时间软件测试”是怎么实现的呢?

2018-08-08 08:36:03

对于其它外设不会修改,即只有CPU进行读写的数据,有两种配置方案:1.将L2 Cache配置为SRAM,数据存于L2 Cache,即数据直接放置于L2 Cache中2.配置L2 Cahce全部为缓存,将数据存于DDR2中,配置此段DDR2相应的MAP寄存器以上两种方案,哪种方案更优?

2019-08-05 14:50:55

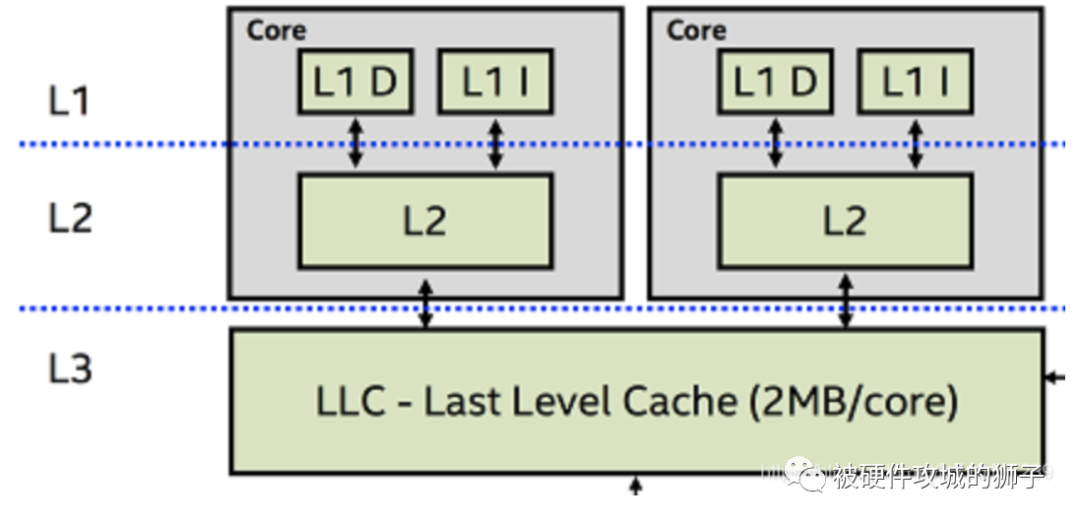

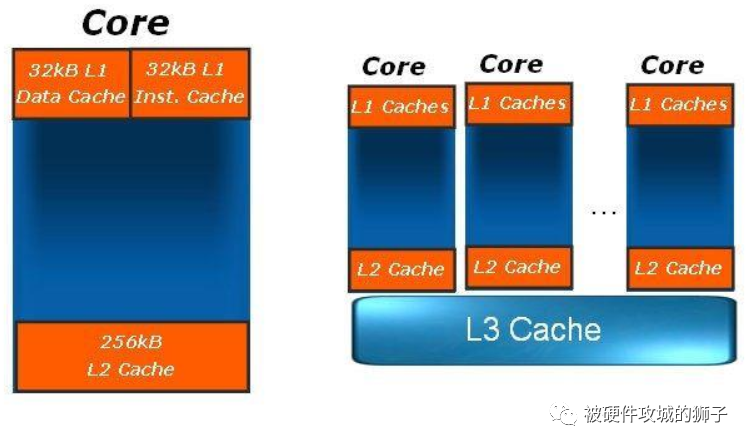

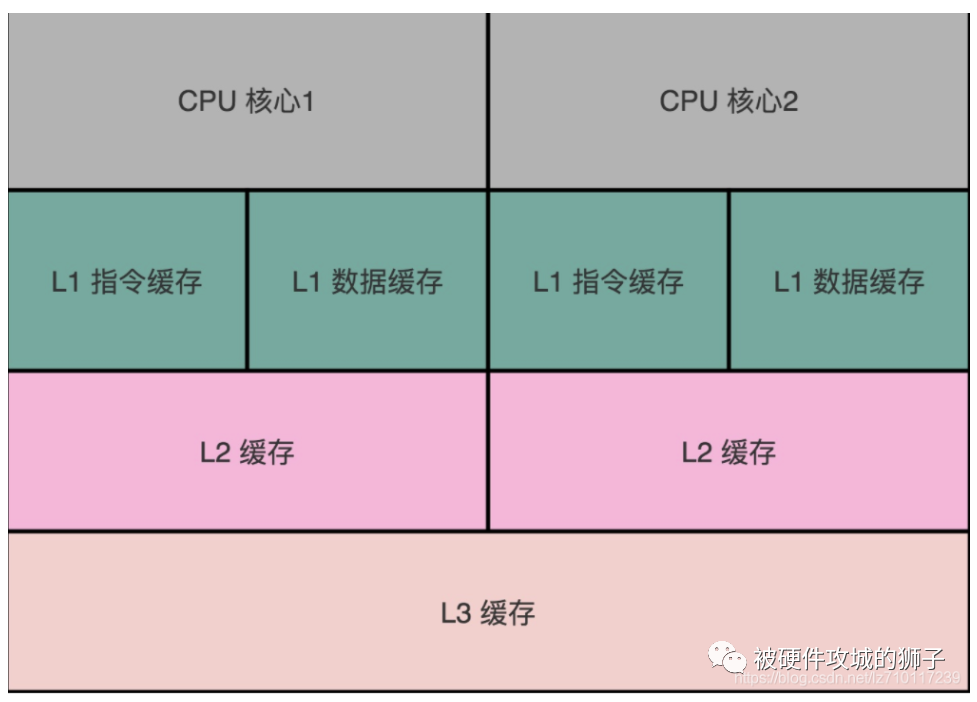

以A15为例,假设L1 cache是2way 4set的 cache type,而L2 cache的空间会比L1大很多,那么L2 cache会是什么样的结构呢?是不是需要cache line的大小一样?或者需要与L1相对应吗,比如也是4set的?

2022-08-12 11:36:49

【作者】:杨兆清;【来源】:《电声技术》2010年02期【摘要】:<正>2010年1月8日,知名音响品牌BOSE在中国推出L1 Compact音乐娱乐扩声系统。与传统

2010-04-23 11:15:00

C674xDSPL2有一个容量为1MB的L2 ROM,该ROM的功用是什么,谢谢

2018-08-01 08:53:56

目前从事DM8148平台的开发工作,想请教一个问题:

通常情况下,数据从外存通过EDMA搬移到L2 cache,然后L1 cache 命中,供CPU访问,CPU处理完数据,在通过EDMA 将处理

2018-06-22 03:35:14

]],

l1PMode:"32K",

l1DMode:"32K",

l2Mode:"128K"

]

由此可以看出L2中256K的容量

2018-06-21 04:58:12

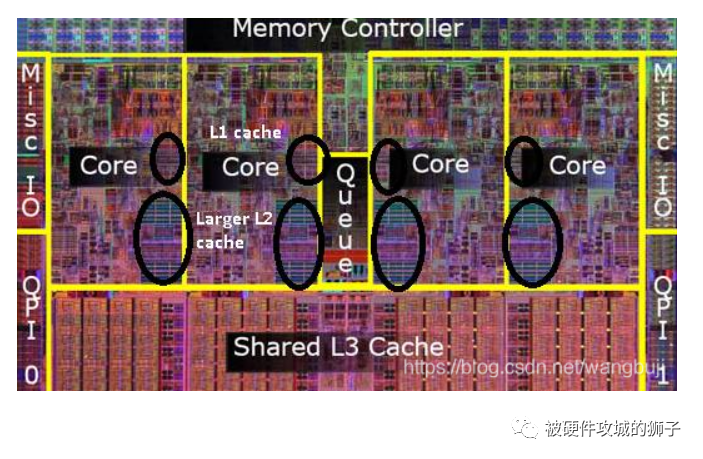

在多处理器配置中,在监听控制单元(SCU)的控制下,高速缓存相关群集中最多有八个处理器可用,该监听控制单元维护L1、L2和L3数据高速缓存一致性。

本节提供周期模型与硬件的功能比较的摘要,以及周期模型的性能和准确性

2023-08-12 07:30:35

L1和L4信号线,L2地线层,L3电源层。如果L4层上的元器件较少,是主布线层,那么将L2改为电源,L3为地,效果可能会更好些。

2019-05-24 06:01:16

L1和L4信号线,L2地线层,L3电源层。如果L4层上的元器件较少,是主布线层,那么将L2改为电源,L3为地,效果可能会更好些。 6层板:L2和L5为地线层和电源层,其它为信号层。

2019-05-21 10:19:01

嗨,U4301A PCIe 8 GT / s分析仪是否支持ASPM L1子状态L1.1和L1.2跟踪(LTSSM流程)? 以上来自于谷歌翻译 以下为原文Hi, Does U4301A PCIe 8

2018-11-02 09:39:24

L1=Link([0 0.1050 0 0 ]); %定义D-H参数L2=Link([pi/200.25-pi/20 ]);L3=Link([0 00.0350 0 ]);L4=Link([0

2019-03-22 21:20:08

最近在学习ZIGBEE的过程中产生了这么几个疑惑,望高人指点。1、图中L1的作用是什么?2、为什么要用到两个晶振?3、四脚的无源晶振怎么画原理图和PCB,图中晶振只有两个引脚而实际却是四个?

2019-04-09 04:43:16

Virtualization: #cpu支持的虚拟化技术L1d cache:#一级缓存(google了下,这具体表示表示cpu的L1数据缓存)L1i cache:#一级缓存(具体为L1指令缓存)L2 cache

2022-10-11 18:48:38

收音机接收电路(一般称为调谐电路):原理图如下:l1:接收天线l2与c:组成谐振电路l3:将选择的信号送接收电路天线线圈接收不同频率的信号,就会在l2端产生不同频的感应电动势。

2020-09-05 00:01:59

这是网上的电路图,它的解释是:L2是反馈线圈,同时也与D4、D3、C3一起组成稳压电路。当线圈L3经D6整流后在C5上的电压升高后,同时也表现为L2经D4整流后在C3负极上的电压更低,当低至约为

2018-10-25 13:53:20

配置强大、做工出色、网速超快的路由器那么建议你选择更高端的优酷路由器L2,这外观这配置简直碉堡了。京东售价69京东售价69淘宝卖家单个批发价59淘宝卖家单个批发价59L1C中秋抢购特价L1C中秋抢购特价碉堡了的优酷路由器L2碉堡了的优酷路由器L2

2016-09-18 21:42:42

大家好:我对于C6678的L2 SRAM(0x00800000)以及各个core私有的L2 SRAM(core 0::0x10800000,core1:0x11800000),存在些疑问,想请教

2019-01-09 10:48:30

诸位高手:小弟使用的是C6747,资料上说这款芯片上有好几个RAM,包括L1、L2和shared RAM,而L1、L2又分别有两块地址与之对应,不知有何区别,而shared RAM与L2又有何区别?sharedRAM 的访问速度如何,可配置为Cache么?望乞赐教。

2018-08-07 07:31:27

缓存性实际上是在内存DDR2中划定一块区域(其起始位置为baseAddr、区域长度为),只有存储在该区域的变量才能被缓存控制器读取并存储到缓存(L1、L2)中;而在该区域以外的变量则不会被缓存控制器访问

2020-05-21 07:29:59

市电整流为直流,再把直流变成几十千赫兹的 高频电流,然后用铁氧休变压器对高频、高压脉冲降压。图中R2、C1、VD5为启动触发电路。C2、C3、L1、L2、L3、VT1、VT2构成高频振荡部分。元器件选择

2008-10-07 08:58:15

原L11.2mm的漆包线在骨架上绕24T作Ll,用φ0.7mm的漆包线绕12T作L2。用φ0.4mm的漆包线绕上300T作输出线圈L3, 现在L1用2.5mm24T.L3用1.0mm400T

2019-06-21 22:35:57

WARNING L1: UNRESOLVED EXTERNAL SYMBOL

SYMBOL:_SENDCHAR

MODULE:main1051.obj (MAIN1051

2023-10-08 07:21:14

最近看6678手册知道每个核都有自己的L1 L2 SRAM ,这没问题,但是看2.3节的Memory Map Summary ,发现除了core 0 到core7的 L1,L2地址,还有一个

2018-06-21 17:19:29

的,只能输入的是偏移延迟和偏移损失。但是自定义校准套件的指令明确表明这些标准存在L0,L1,L2系数。我们想知道为什么8720ES不可能输入短标准的那些系数,或者仅仅输入偏移延迟和偏移丢失信息就足够

2019-05-20 08:02:10

关于cache配置的问题,在L1或者L2中可以配置为cache或者SRAM,请问cache的配置与什么有关?有一些参考资料么?谢谢没有搞清楚应当如何配置cache,以及配置多大的cache,求指导!!!

2018-07-25 09:24:32

各位大牛好,

在做DM8148开发过程中,需要将ARM处理器输出的数据写入DSP端的L2缓存中,以便于DSP提高算法处理的速度。目前,我们的做法:

在DSP端定义个buffer放在L2缓存中;

在ARM端根据内存分配的指针直接将数据拷贝到定义的buffer中;

2018-05-28 08:03:21

您好,我使用的芯片是C6748,使用DSP/BIOS。C6748的L1P L1D L2都可以部分配置成缓存或RAM。DSP/BIOS中默认设置L1P L1D为cache,L2全部为RAM。请问,在

2018-08-02 06:54:06

在文档EVLCMB1-90WADP中,L2是简单的电感还是变压器?如果它是变压器,那么匝数比是多少?以上来自于谷歌翻译以下为原文 In the document EVLCMB1

2019-01-23 06:08:00

/AWR1642上总共有768KB L3 RAM。这768KB L3内存按照128KB一个bank,分成了6个bank(bank6~bank1),其中bank1到bank3是专门给DSS使用的。剩下的3个

2019-03-12 06:45:10

练习:利用定时器使L1每秒闪烁(亮0.5秒灭0.5秒),L8亮五秒灭五秒。关闭蜂鸣器。#include "reg52.h"***it L1 = P0^0;***it L

2022-01-12 07:22:47

/AWR1642上总共有768KB L3 RAM。这768KB L3内存按照128KB一个bank,分成了6个bank(bank6~bank1),其中bank1到bank3是专门给DSS使用的。剩下的3个

2022-11-10 08:06:00

我想测量这3个相位线(三相到380-440V)这三个相同的50Hz频率的正弦波信号。对这三条线进行零交叉,如+VE和VE半周期。我想测量这三个信号之间的相移。相角L1相为0°,L2相为120°,L3

2019-10-18 06:45:19

:失败(1);中止(1);警告(0)]有人知道“L1C”是什么意思(上面是“DUT的父端口不支持L1C”)吗?关于如何正确管理USB2.0 LPM L1兼容性,是否有一些FX3FW示例?谢谢,达克斯

2019-06-27 09:09:50

请问,用I.MX6UL开发板OKMX6UL,使用Linux的情况下,如何获取CPU中L1/L2的Cache状态和大小;如何禁用和使能Cache?

2022-11-29 06:37:16

接L1和L3(不用区分火线和零线),然后L1C接到L1,L2C接到L3; 三相电接L1、L2和L3,然后L1C接到L1,L2C接到L3; 当然还要接地。试运行 用miniUSB...

2021-09-17 06:55:48

大家好,我想购买一台带有两个处理器的服务器,每个处理器至少支持16个核心,我还需要它们支持CMT,MBM,L3 CAT和L3 CDP,在理想的世界中它们也支持MBA。我已经读过家庭E5xxxx v4

2018-11-06 11:19:54

#include#include #define uchar unsigned char #define uint unsigned int***it L1=P3^0;***it L2=P3^1

2016-04-06 16:59:32

时间分开的法子。#include***it K1=P1^0;***it L1=P1^4;***it L2=P1^5;***it L3=P1^6;***it L4=P1^7;unsigned char

2012-09-13 20:22:05

L3);uchar ECO,u,L1,L2,L3;unsigned long num;void main(){TCL2543_CS=1;TCL2543_CLK=0;while(1){num

2016-04-20 15:13:24

描述用于 Commodore C64 BN/E 250469 的 L1 过滤器更换用于 250469 板的原始 L1 线路滤波器(可能是Tokin D-08C2)已停产。此适配器板可让您使用现代 Laird CM4545Z131B-10 作为替代品。PCB

2022-07-29 06:18:26

;***it l1=P3^4;//l1是第一竖列***it l2=P3^5;***it l3=P3^6;***it l4=P3^7;***it wela=P2^7;***it dula=P2^6;uchar

2014-03-13 16:12:23

这个图中,L3是什么元件?L1、L2、L3有什么区别?

2015-11-02 00:50:08

相序保护器和缺相保护器都是三相保护器,他们之间既有联系又有区别,众所周知,三相电的三根火线L1,:L2,L3是有方向的,相邻的两根火线相差180度,因此顺序是不能接反的,比如,L1,L2,L3

2021-09-13 09:34:07

感谢,进来的朋友。本人请教几个问题。L1,L2,L3估计是3V-5V电压的小灯.1.当电流从1线进入时,L2与L3灯会亮吗?如果不会亮,电流是否从M3(二极管)通过了,为什么不从L2、L3通过。还是

2015-11-02 22:29:27

几章习题答案一、十四章课时习题一、十四章课时习题1.某机有五个中断源L0、L1、L2、L3、L4,按中断响应的优先次序由高向低排序为L0→L1→L2→L3→L4,现要求中断处理次序改为L1→L

2021-07-26 06:44:21

目前从事DM8148平台的开发工作,想请教一个问题:通常情况下,数据从外存通过EDMA搬移到L2 cache,然后L1 cache 命中,供CPU访问,CPU处理完数据,在通过EDMA 将处理

2018-07-24 06:57:47

想把L2空间一部分设置成缓存,缓存大小为64kb,把DDR上最开始的16M设置成cacheable,我是这样配置的:L2CFG=0x2h;L2INV=1;MAR128=0XFFFFFFFFh;不知

2018-08-02 07:44:50

1 最近在学习c6678存储层次结构域cache,想问一下msmc一般推荐怎么用(就是直接作为共享的sdram,还是配置为shared L2,或者配置为shared L3)?2 关于4M 的MSM

2018-08-07 08:20:22

有哪位大神解读一下,L2当中的1M的ROM怎么使用,没有找到相关的文档!

2019-07-24 06:40:32

创龙技术支持工程师您好: 我使用C6748实现图像处理,需要完成CACHE的优化。图像处理的图片为64K,想将L2分配为128Kcache与128K 内部RAM使用。问题1:128K的内部RAM存储

2019-10-21 08:21:50

在调试6670时,发现L2的地址有0x0080 0000,每个核也有自己的L2地址,像核0 有0x1080 0000。难道每个核有自己的L2,另外有一个L2?如果是这样的话,这两种L2有什么关系吗? 谢谢啊

2019-01-04 11:30:22

各位专家好:请问在内存保护机制中 L2MPFAR 寄存器保存的是地址是不是相对于L2 SRAM的偏移地址?如果是,那么这个 L2 SRAM 是Local SRAM 还是 CorePac L2 SRAM?

2019-01-10 11:37:07

请问在C6678中,EDMA和 IDMA有什么差别呢?L1DCache能Cache外存上(如DDR3或EMIF16NOR)的数据吗?把L2作为Cache用和,把L2用作RAM再用EDMA乒乓缓存结构,那个性能会好些呢?

2018-08-07 06:08:37

DSPL2RAM o = 0x00800000 l = 0x00040000 /* 256kB L2 Internal RAM */ SHDSPL2RAM o = 0x11800000 l

2019-01-15 07:40:42

在C6655的memory map summary中这两个地址有什么区别00800000 008FFFFF1M Local L2 SRAM10800000 108FFFFF1M CorePac0 L2 SRAM还是对于单核来说就是一样的东西,而是使用的场合不一样?

2018-07-24 08:10:12

最近在TMS320F2812上实现1024点FFT,分配空间时出现了RAM不够的情况,因为段DRAMH0的可用空间不够,编译一直提示段.ebss分配失败,所以想利用L0、L1这两段空间,不知道可以?(主要是L0、L1是受CSM保护的,不知道能不能进行分配)

2018-08-20 07:23:45

28335的SRAM共有34K,L0~L3为双端口RAM,L4~L7为DMA应用RAM,这些已经占用了32K空间;而参照F28335的内存映射表(Page37,SPRS439m)时28335的CMD

2018-08-22 10:19:01

( 'd',0.525, 'a',0.15,'alpha',pi/2) ; L2 =Link( 'd',0, 'a',0.79, 'alpha',0) ; L3 =Link( 'd',0, 'a

2020-01-09 11:25:53

方法”等于L1,其中启用了PHY。1 -如果PHY禁用,CPU如何从USB总线重新唤醒?2——是否可以使用API进入L2挂起模式?这对于节省一些MW和达到2.5mA的总悬浮电流是非常有用的。谢谢达克斯

2019-10-14 07:38:23

本帖最后由 一只耳朵怪 于 2018-6-19 14:24 编辑

大家好,我用的是6678开发板,看数据手册上有这么一段To support MSMC, the L2 memory

2018-06-19 00:53:16

,L2设256KBCACHE 此时将FFT输入输出旋转因子都放在L2里,需要254933个周期。都放在MCSM需要295429个周期。都放在DDR3中要274579周期。 这是CACHE未命中miss

2018-06-25 00:01:32

小弟费解了很久的电路。 L1 L2 L3是三相电源输入端, 系统供电是由L1 L2通过变压器整流得到。4N25 是个光耦(原理图估计是抄板的来的) 。 光耦输出的信号由单片机检测。 产品是个三相电机控制系统。 那该电路到底是什么功能呢?过零检测? 相序检测?

2019-09-16 13:48:48

函数的功能就是使能L1-Cache。L1-Cache由两部分组成,L1 instruction cache与L1 data cache。可以看下面Cortex –M7的组成框图。

2016-08-12 11:55:36

通过TDA2x中datasheet提及到的“Up to 2.5MB of on-chip L3 RAM”,这部分的L3 RAM是在哪里可以设置或者查看的?

2022-05-11 18:41:09

L1可级联,信号限制器L1 信号限制器采用分立式混合设计,采用薄膜制造工艺以实现精确的性能和高可靠性。此设计使用肖特基桥式四极管和反并联二极管,可在宽带频率范围内提供一致

2023-04-19 16:54:48

Qorvo QPQ1063 L1/L2低损耗GPS SAW双工器Qorvo QPQ1063 L1/L2低损耗GPS SAW(表面声波)双工器优化用于抑制无用的GPS信号。QPQ1063为支持的波段

2024-02-26 23:23:54

Qorvo QPQ1028双用途GPS L1/L2双路滤波器Qorvo QPQ1028双用途GPS L1/L2双滤波器为低功耗发射器提供出色的功率处理能力。QPQ1028设计用于抑制杂散信号,无需

2024-02-26 23:27:17

正在加载...

电子发烧友App

电子发烧友App

评论