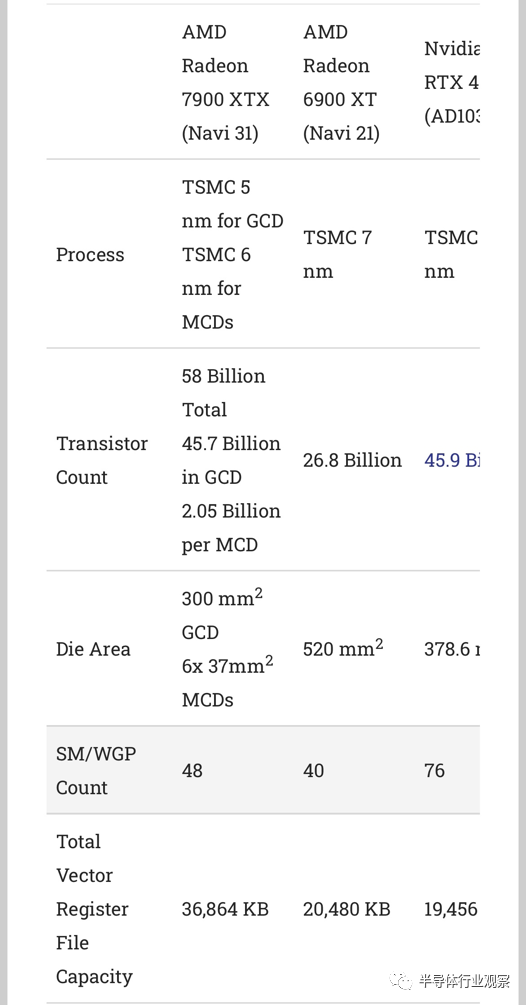

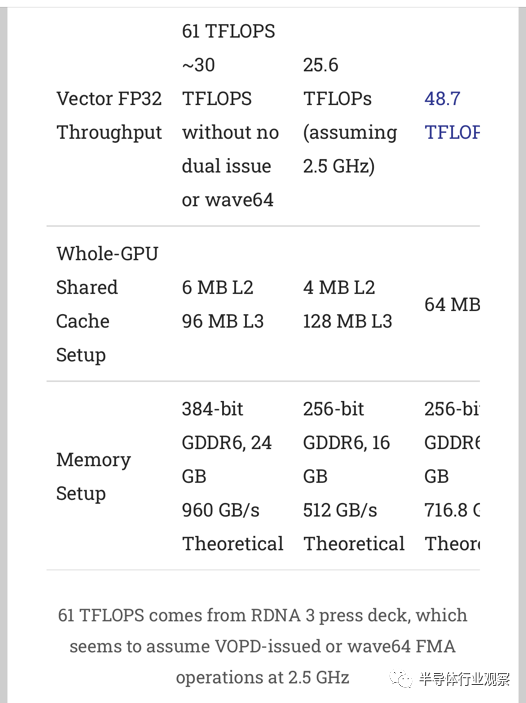

RDNA 3 代表了 AMD RDNA 架构的第三次迭代,它在其消费类图形产品线中取代了 GCN。在较高层面上,与 RDNA 2 相比,RDNA 3 的目标是大规模扩展。缓存设置在各个层面进行了调整,以提供更高的带宽。为了扩展计算吞吐量而不仅仅是添加更多 WGP,AMD 为通用指令的子集实现了双重发布功能。

在本文中,我们将对 7900XTX 进行一些微基准测试,看看与 AMD 的 RDNA 2 架构相比的差异。我们还将结合Nemes 的 GPU 微基准测试套件的结果。虽然我对 CPU 微基准测试有相当多的了解,但我无法将几乎那么多的时间投入到我的 OpenCL bsaed 测试中。Nemes 在她基于 Vulkan 的 GPU 测试套件上取得了很好的进展,她的测试在某些领域提供了更好的覆盖。

内存延迟

测试缓存和内存延迟让我们可以很好地了解 RDNA 3 的缓存和内存设置。延迟测试在后 GCN AMD 图形架构上也很复杂,因为全局内存层次结构可以通过标量或矢量数据路径访问,它们具有不同的一级缓存。如果编译器确定加载的值在整个波前(wavefront)是恒定的,它可以告诉 GPU 使用标量数据路径。因为标量路径用于延迟敏感的东西,比如计算波前负载的内存地址,延迟是相当不错的(对于 GPU)。在访问全局内存时,AMD 大量使用矢量和标量端。确切的比例会因工作量而异,但通常两者都很重要。

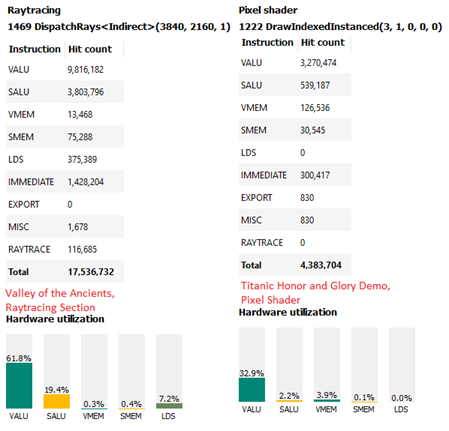

Radeon GPU Profiler 的统计数据显示了在 RDNA 2 上运行的几个工作负载上执行的指令混合。SMEM(标量路径)和 VMEM(矢量路径)都用于命中全局内存。

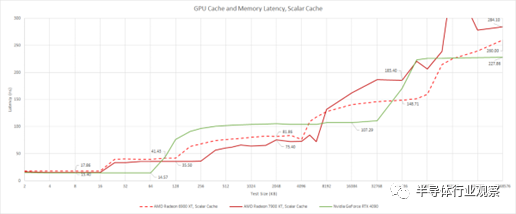

让我们从标量方面开始。与 RDNA 2 一样,RDNA 3 具有 16 KB、4 路组关联标量缓存。此缓存的加载到使用延迟非常好,RDNA 3 为 15.4 ns,RDNA 2 为 17.4 ns。RDNA 3 的延迟优势至少部分归功于更高的时钟速度。Nvidia 的 Ada Lovelace 在到达 SM 的 L1 时的延迟稍好一些,考虑到 Nvidia 缓存的大小,这令人印象深刻。我们在这里看到 64 KB 的 L1 缓存容量,但 Ada Lovelace 实际上有一个 128 KB 的 SRAM 块,可以在 L1 和共享内存 (LDS) 使用之间灵活分区。

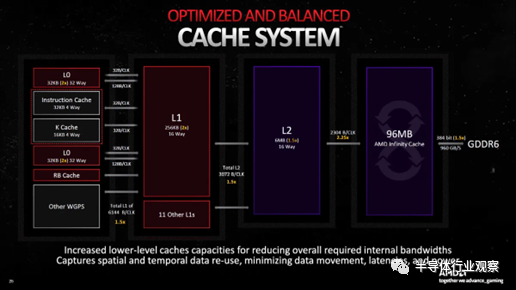

AMD 还增加了 L1 和 L2 中级缓存的容量,以便更好地处理更大 GPU 的带宽需求。RDNA 2 有一个 128 KB、16 路集关联 L1,在着色器阵列中共享。RDNA 3 将容量翻倍至 256 KB,同时保持 16 向结合性。L2 缓存容量增加到 6 MB,而 RDNA 2 上为 4 MB,同时还保持 16 路关联性。尽管容量有所增加,但 RDNA 3 在 L1 和 L2 上都提供了可测量的延迟改进。

AMD 的幻灯片描述了 RDNA 3 的缓存系统

然而,RDNA 3 的 Infinity Cache 有所退步。容量从 128 MB 减少到 96 MB,同时延迟增加。这并不奇怪,因为 RDNA 3 的 Infinity Cache 是在单独的内存控制器芯片上实现的。但这也不应该是一个大问题。RDNA 3 可能能够通过其片上 L2 为更多内存访问提供服务,而不必经常访问 Infinity Cache。

为了减少内存带宽需求,Nvidia 选择大规模扩展 L2 而不是添加另一级缓存。与 AMD 最近的 GPU 相比,这稍微提高了 L2 延迟,但确实提供了比 Ada Lovelace 更优越的延迟特性,以应对数十兆字节范围内的内存占用。RTX 4090 的 L2 容量为 72 MB,比芯片上实际存在的 96 MB SRAM 有所缩减。

与 RDNA 2 相比,RDNA 3 上的 VRAM 延迟略有上升。Nvidia 在该领域具有优势,部分原因是 AMD 在前往 DRAM 的途中检查额外级别的缓存时会产生额外的延迟。

矢量延迟

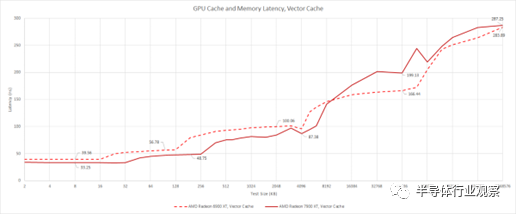

当然,矢量路径的延迟也很重要,因此我修改了测试以防止编译器确定加载的值在整个波前保持不变。从矢量方面来看,AMD 发现延迟增加了,但矢量访问对延迟的敏感度应该较低。向量缓存的设计也发挥了作用——与 4 路标量缓存相比,它在 RDNA 2 和 RDNA 3 上都是 32 路组关联。在一次查找中检查 32 个标签可能会比检查四个标签产生更高的延迟。

尽管如此,与 RDNA 2 相比,RDNA 3 设法减少了 L0 向量缓存延迟,同时将容量翻了一番,达到每个 CU 32 KB。

在缓存层次结构的下方,延迟特性主要反映标量端的特性,尽管绝对延迟当然更高。当我们从矢量端进行测试时,RDNA 2 的 VRAM 延迟优势也会降低。这两种架构在 1 GB 的测试大小下结束了几纳秒,这基本上没有。

内存带宽

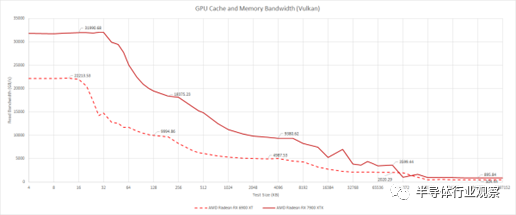

Radeon 7900 XTX 比 6900 XT 拥有更多的 WGP。同时,每个 WGP 都有更多的计算吞吐量,因此必须加强内存子系统来满足它们的需求。因此,RDNA 3 在内存子系统的每个级别都看到了巨大的带宽增加。L1 和 L2 缓存的增益尤其显着,与 RDNA 2 相比,带宽大约翻了一番,尽管它们的容量也有所增加。

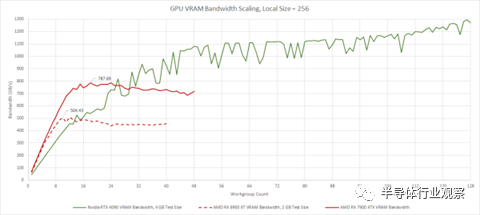

使用 Nemes 的带宽测试,因为它比我的更干净地溢出缓存级别

Infinity Cache 带宽也有大幅增加。使用纯读取访问模式,我们无法获得理论上可能实现的 2.7 倍带宽增长。尽管如此,1.8 倍的带宽提升并不是开玩笑的。考虑到 Infinity Cache 在不同的小芯片上物理实现,带宽优势令人印象深刻,而 RDNA 2 将 Infinity Cache 保留在芯片上。

AMD 还为 7900XTX 配备了更大的 GDDR6 设置,使其带宽比 6900XT 高得多。事实上,它的 VRAM 带宽更接近 GA102 的带宽。这可能使 AMD 能够保持高性能,同时减少末级缓存的数量,从而允许使用更小的内存控制器芯片。

占用率较低时的带宽

现代 GPU 旨在利用大量显式并行性。但是一些工作负载没有足够的并行性来填充所有可用的计算单元。顶点着色器,我在看着你。Nemes 的测试套件目前没有为较低的工作组数量提供结果,所以我在这里使用 OpenCL 结果。

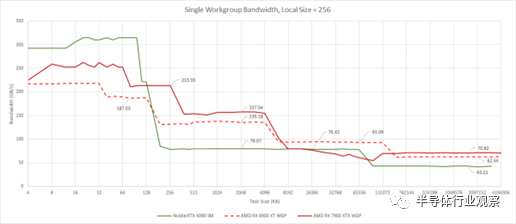

让我们从单个工作组的带宽开始。运行单个工作组将我们限制在 AMD 上的单个 WGP,或 Nvidia 架构上的 SM。这是我们可以在 CPU 上获得的最接近单核带宽的值。与 CPU 上的单核带宽一样,此类测试并不特别代表任何现实世界的工作负载。但它确实让我们从单个计算单元的角度了解了内存层次结构。

同样,我们可以看到 RDNA 3 更大的片上缓存。从单个 WGP 的角度来看,所有这三个缓存级别都提供了更高的带宽。Nvidia 有一个非常大和快速的一级缓存,但在那之后,只要它可以服务于 L1 或 L2 的访问,AMD 就有优势。

从 Infinity Cache 来看,RDNA 3 的日子更难过,这可能是因为单个 WGP 没有获得足够的内存级并行能力增加来吸收 Infinity Cache 延迟的增加。事实上,一个 WGP 的 Infinity Cache 带宽与 RDNA 2 中的带宽相比有所下降。当我们使用 VRAM 时,情况再次翻转,RDNA 3 领先。

带宽缩放

共享缓存很好,因为可以更有效地使用它们的容量。共享缓存可以存储数据一次并为来自多个计算单元的请求提供服务,而不是在多个私有缓存之间复制共享数据。然而,共享缓存很难实现,因为它必须能够处理所有客户端的带宽需求。

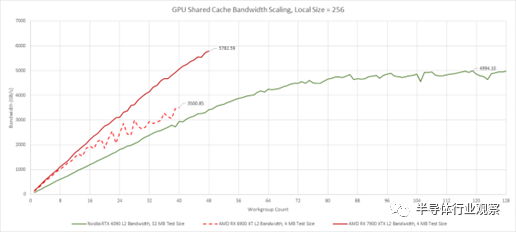

我们将从 L2 带宽开始,因为 L0 和 L1 带宽几乎呈线性扩展。L2 缩放更难实现,因为单个 6 MB L2 缓存必须为 GPU 上的所有 48 个 WGP 提供服务。考虑到这一点,RDNA 3 的 L2 在扩展方面做得非常好,可以满足所有这些 WGP 的带宽需求。随着 WGP 数量的增加,RDNA 3 的 L2 带宽开始远离 RDNA 2。

与 Nvidia 的 Ada Lovelace 相比,这两种 AMD 架构都能够为匹配的工作组数量提供更多的 L2 带宽。但是,RTX 4090 具有更大的一级缓存,应该可以减少 L2 流量。Ada Lovelace 的 L2 也起着稍微不同的作用,兼作某种 Infinity Cache。考虑到其非常大的容量,Nvidia 的 L2 表现非常出色。如果我们与具有相似容量的 RDNA 3 的 Infinity Cache 进行比较,Ada 的 L2 在低占用率下保持相似的带宽。当 Ada 的所有 SM 都发挥作用时,Nvidia 将享有巨大的带宽优势。当然,AMD 的 Infinity Cache 不需要提供那么多的带宽,因为 L2 缓存通常会吸收相当比例的 L1 未命中流量。

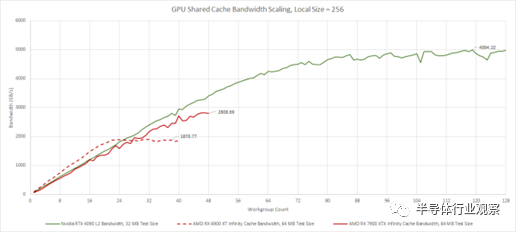

与 RDNA 2 相比,RDNA 3 的 Infinity Cache 的提升速度稍慢,并且加载不到其 WGP 的一半处于劣势。但是,当工作负载扩展到填满所有 WGP 时,RDNA 3 的 Infinity Cache 显示出比 RDNA 2 更大的带宽优势。

4090 夸大了其最大内存带宽,因为我们的测试无法完全击败 4090 上的读取组合

从 VRAM 来看,两种 AMD 架构都以低占用率享有非常好的带宽。

RDNA 3 从一个小优势开始,随着更多 WGP 发挥作用而变得更大。从另一个角度来看,RDNA 2 的 256 位 GDDR6 设置可能仅用 10 个 WGP 就可以饱和。RDNA 3 更大的 VRAM 子系统可以满足更多需要全带宽的 WGP。如果仅加载少量 SM,Nvidia 在 VRAM 带宽方面会遇到更多麻烦,但在占用率较高时处于领先地位。

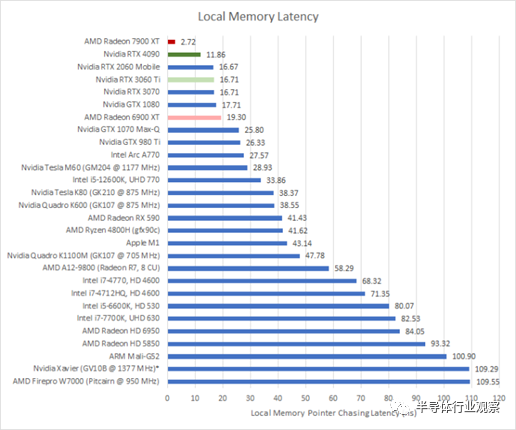

本地内存延迟

除了常规的全局内存层次结构之外,GPU 还具有快速暂存器内存。OpenCL 调用这个本地内存。在 AMD GPU 上,相应的结构称为本地数据共享 (LDS)。Nvidia GPU 称之为共享内存。与缓存不同,软件必须明确分配和管理本地内存容量。一旦数据在 LDS 中,软件就可以期望有保证的高带宽和低延迟访问该数据。

与前几代 RDNA 一样,每个 RDNA 3 WGP 都有一个 128 KB 的 LDS。LDS 内部构建有两个 64 KB 块,每个块都隶属于 WGP 中的一个 CU。每个 64 KB 块包含 32 个存储区,每个存储区可以处理 32 位宽的访问。这使得 LDS 可以在每个周期为波前范围的负载提供服务。我们目前没有针对 LDS 带宽的测试,但 RDNA 3 似乎具有非常低的延迟 LDS。

*Xavier 结果可能不准确,因为该 GPU 上的时钟斜坡非常慢

由于架构改进和更高的时钟速度相结合,RDNA 3 大大改善了 LDS 延迟。Nvidia 的本地内存延迟略高于 AMD 的架构,但 RDNA 3 改变了这一点。当 RDNA 3 处理光线追踪时,低 LDS 延迟可能非常有用,因为 LDS 用于存储 BVH 遍历堆栈。

作为比较,RDNA 2 的 LDS 具有与其标量缓存大致相同的加载到使用延迟。它仍然非常有用,因为它可以比从 L0 向量缓存中更快地将数据放入向量寄存器。我检查了这个测试的编译代码,它正在使用向量寄存器,即使工作组中除了一个线程之外的所有线程都被屏蔽了。

WGP 计算特性

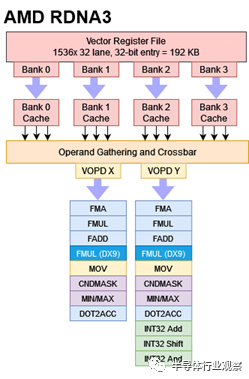

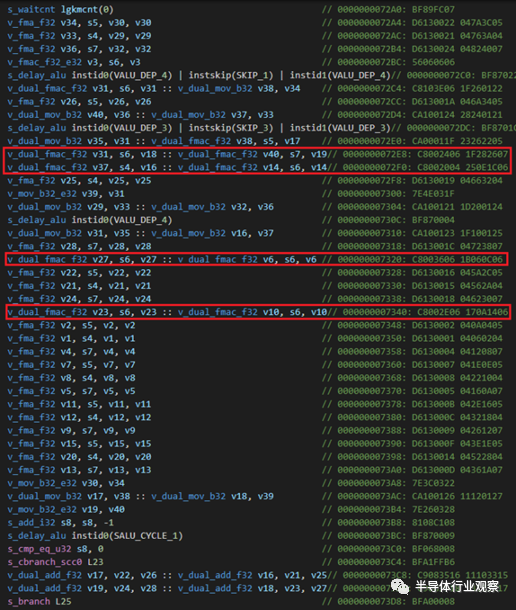

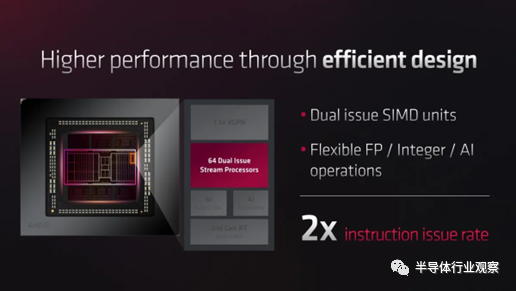

相比RDNA 2,RDNA 3在计算吞吐量上明显有很大优势。毕竟,它具有更高的 WGP 计数。但计算吞吐量的潜在增长不止于此,因为 RDNA 3 的 SIMD 获得了有限的双重发布能力。在 wave32 模式下,某些常用操作可以打包到单个 VOPD(向量操作,对偶)指令中。在 wave64 模式下,SIMD 自然会尝试在单个周期内开始执行 64 宽波前,前提是指令可以双重发出。

RDNA 3 VOPD 指令以八个字节编码,并支持两个操作中的每一个的两个源和一个目标。这不包括需要三个输入的操作,例如通用的融合乘加操作。双重发行机会进一步受到可用执行单元、数据依赖性和寄存器文件带宽的限制。

同一位置的操作数不能从同一寄存器组(register bank)读取。早些时候我们推测这是handling bank 冲突的局限性。然而,AMD 的 ISA 手册明确指出,每个存储体实际上都有一个寄存器缓存,其中包含三个读取端口,每个端口都与一个操作数位置相关联。来自相同源位置的相同存储体的两次读取将超额订阅寄存器高速缓存端口。另一个限制适用于目标寄存器,它不能同时是偶数或奇数。

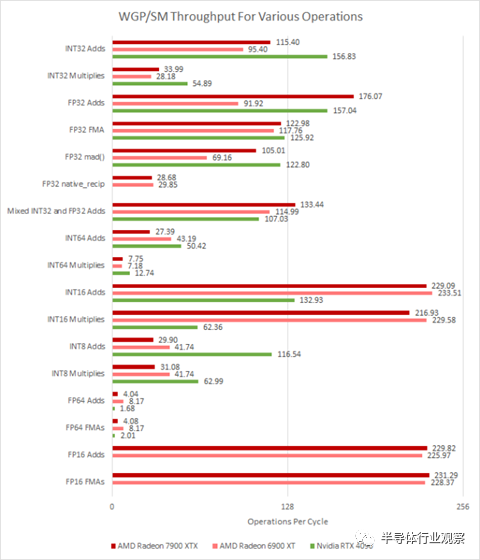

在此测试中,我们运行单个工作组以将测试保持在 WGP 的本地。由于最近 GPU 上的提升行为变化很大,我们将时钟锁定到 1 GHz 以深入了解每个时钟的行为。

我的测试肯定高估了 Ada 的 FP32 和 INT32 添加,或者 2.7 GHz 时钟速度的假设已关闭

不幸的是,通过 OpenCL 进行测试很困难,因为我们依赖编译器来寻找双重问题机会。我们只看到 FP32 添加令人信服的双重问题行为,其中编译器发出 v_dual_add_f32 指令。混合 INT32 和 FP32 加法测试看到了一些好处,因为 FP32 加法是双重发出的,但由于缺少用于 INT32 操作的 VOPD 指令,因此无法为 INT32 生成 VOPD 指令。用于计算 GPU 的标题 TFLOPs 数的融合乘加看到很少发出双重问题指令。两种架构都可以双倍速率执行 16 位操作,尽管这与 RDNA 3 的新双发射功能无关。相反,16 位指令受益于以压缩数学模式发出的单个操作。在其他主要类别中,吞吐量与 RDNA 2 基本相似。

为融合乘加测试生成的 RDNA 3 代码,双问题对标记为红色

我猜 RDNA 3 的双发模式影响有限。它在很大程度上依赖于编译器来寻找 VOPD 的可能性,而编译器在看到非常简单的优化时愚蠢得令人沮丧。例如,上面的 FMA 测试对两个输入使用一个变量,这应该使编译器能够满足双重问题约束。但显然,编译器并没有让它发生。我们还使用 clpeak 进行了测试,并在那里看到了类似的行为。即使编译器能够发出 VOPD 指令,只有在计算吞吐量成为瓶颈而不是内存性能时,性能才会提高。

从 AMD 的新闻稿中幻灯片,注意到新的双重发行能力

另一方面,VOPD 确实留下了改进的潜力。AMD 可以通过用手动优化的程序集替换已知的着色器来优化游戏,而不是依赖于编译器代码生成。与编译器所希望的相比,人类更善于发现双重问题机会。Wave64 模式是另一个机会。在 RDNA 2 上,AMD 似乎将许多像素着色器编译为 wave64 模式,在这种模式下,双重问题可能会在编译器没有任何调度或寄存器分配智能的情况下发生。

一旦 AMD 有更多时间优化架构,看看 RDNA 3 的性能将会很有趣,但他们绝对有理由不将 VOPD 双问题功能作为额外的着色器来宣传。通常,GPU 制造商使用着色器计数来描述他们的 GPU 每个周期可以完成多少 FP32 操作。理论上,VOPD 将使每个 WGP 的 FP32 吞吐量翻倍,除了额外的执行单元外,硬件开销非常小。但它是通过将繁重的调度责任推给编译器来实现的。AMD 可能意识到编译器技术无法胜任这项任务,而且不会很快达到目标。

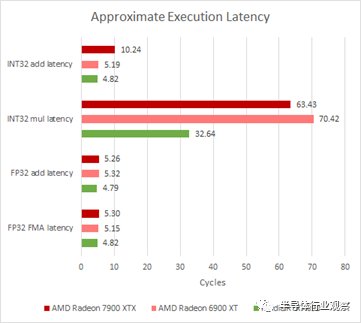

在指令延迟方面,RDNA 3 与之前的 RDNA 架构相似。常见的 FP 操作以 5 个周期的延迟执行。Nvidia 在这方面略有优势,能够以 4 个周期的延迟执行常见操作。

GPU 不进行分支预测,也不像 CPU 那样具有强大的标量执行能力,因此循环开销通常会导致延迟被高估,即使在展开时也是如此

从图灵开始,Nvidia 也实现了非常好的整数乘法性能。整数乘法在着色器代码中似乎极为罕见,而且 AMD 似乎也没有针对它进行优化。32 位整数乘法的执行速度约为 FP32 的四分之一,而且延迟也相当高。

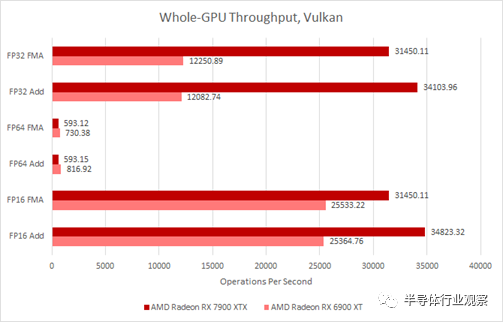

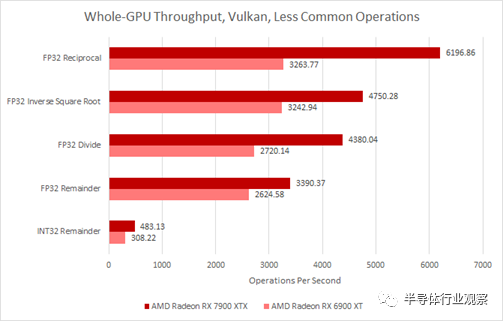

全 GPU 吞吐量——Vulkan

在这里,我们使用 Nemes 的 GPU 基准测试套件来测试完整的 GPU 吞吐量,其中考虑了所有 WGP 处于活动状态时的加速时钟。RDNA 3 通过 VOPD 指令、更高的 WGP 计数和更高的时钟速度实现更高的吞吐量。奇怪的是,AMD的编译器非常愿意将Nemes的测试代码序列转化为VOPD指令。

为了从每秒操作中获得 FLOP 数,将 FMA 数乘以 2,这为 FP32 和 FP16 FMA 计算提供了 62.9 TFLOP。

结果是 FP32 吞吐量大幅增加。FP16 的吞吐量增加较小,因为 RDNA 2 能够使用打包的 FP16 执行,以及 v_pk_add_f16 等指令。这些指令将每个 32 位寄存器解释为两个 16 位元素,从而使吞吐量翻倍。RDNA 3 做同样的事情,但不能双重发出这样的打包指令。奇怪的是,RDNA 3 实际上在 FP64 吞吐量上倒退了。我们之前已经在 OpenCL 中看到了这一点,其中一个 RDNA 2 WGP 每个周期可以执行八个 FP64 操作。RDNA 3 将吞吐量减半,这意味着 WGP 可以执行四次 FP64 操作——可能每个周期每个 SIMD 一个。

两个 GPU 上特殊操作的吞吐量都较低。倒数通常用作避免昂贵的除法运算的一种方式,并且在两种体系结构上都以四分之一的速率运行。除法甚至更慢,对整数运算进行模块化运算与进行 FP64 一样慢。

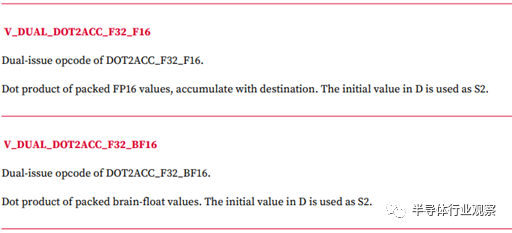

现在,让我们谈谈 AMD 声称的 123TFLOP FP16 数字。虽然这在技术上是正确的,但这个数字有很大的局限性。查看 RDNA3 ISA 文档,只有一个 VOPD 指令可以同时发出打包的 FP16 指令和另一个可以使用打包的 BF16 数字的指令。

这些是可以使用压缩数学的 2 条 VOPD 指令。

这意味着标题 123TF FP16 数字只会在非常有限的场景中看到,主要是在 AI 和 ML 工作负载中,尽管游戏已经开始更频繁地使用 FP16。

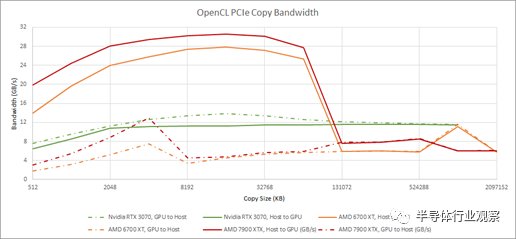

PCIe链路

Radeon 7900 XTX 通过 PCIe 4.0 x16 链接连接到主机。与 RDNA 2 一样,AMD 的新图形架构在将数据移动到 GPU 时表现非常出色,尤其是在中等大小的块中。从 GPU 获取数据时传输速率较低。

使用 Smcelrea 的 6700 XT 结果是因为我的 6900 XT 没有设置可调整大小的 BAR,这似乎会影响 OpenCL 带宽结果。

Nvidia 处于中间位置,在所有副本大小和方向上都具有不错的传输速度。在大拷贝尺寸下,Nvidia 似乎比 AMD 在 PCIe 传输带宽方面具有优势。

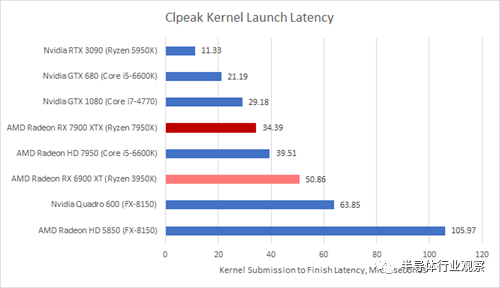

内核启动延迟

在这里,我们使用clpeak来估计 GPU 启动内核并报告其完成所需的时间。Clpeak 通过向 GPU 提交极少量的工作并测试完成所需的时间来做到这一点。

Terascale 2 在这里做什么?5850怎么还活着?不要质疑它......

结果似乎相差很大,我们无法将平台与我们的测试模型相匹配。然而,我们可以看出 RDNA 3 没有任何异常。Nvidia 的 GPU 内核启动速度可能稍快一些,但由于我们无法匹配平台,因此很难得出任何结论。

最后的话

AMD 的 RDNA 2 架构使该公司的 GPU 与 Nvidia 的最佳性能相差无几,这标志着 AMD 与 Nvidia 最高端卡的距离达到了另一个例子。

RDNA 3 希望通过扩大 RDNA 2 来推进这一点,同时引入旨在提高性能的架构改进,而不仅仅是添加 WGP。AMD 采用多管齐下的策略来实现这一目标。

在物理实现方面,AMD 转向了台积电更先进的 5 纳米工艺节点。5 nm 允许更高的晶体管密度,并在没有膨胀区域的情况下改进 WGP。因此,WGP 获得了增加的寄存器文件大小和双重发布能力。Chiplet 技术通过将 Infinity Cache 和内存控制器移动到单独的芯片上,可以实现更小的 5 纳米主芯片。这有助于通过在图形芯片上使用更少的区域来实现 VRAM 连接,从而实现更高带宽的 VRAM 设置。

更高的带宽是支持更大 GPU 的关键,而 AMD 超越了 VRAM 带宽。缓存带宽在每个级别都会增加。AMD 还增加了片上缓存的容量,因为即使在片之间有中介层,片外访问也更耗电。即使采用小芯片设置,AMD 也需要最大限度地提高面积效率,dual issue 就是一个很好的例子。VOPD 指令允许 AMD 为最常见的操作添加额外的执行单元,但在其他地方的额外开销很少。AMD 还增加了矢量寄存器文件容量,这应该有助于提高占用率。而且,它们极大地减少了 LDS 延迟。光线追踪似乎是这一变化的明显受益者。

结果是 GPU 的性能非常接近 Nvidia 的 RTX 4080。根据Hardware Unboxed,7900 XTX 在 1440p 时慢 1%,在 4K 时快 1%。AMD 没有使用非常大的 WGP/SM 数量,而是通过提高每个 WGP 的吞吐量来实现其性能。他们还专注于为 WGP 提供更复杂的内存层次结构。与上一代相比,最后一级缓存的总容量有所下降,因为 384 位内存总线意味着 RDNA 3 不需要那么高的缓存命中率来避免带宽瓶颈。

AMD 和 Nvidia 因此做出不同的权衡以达到相同的性能水平。通过将缓存和内存控制器放在单独的 6 纳米芯片上,小芯片设置帮助 AMD 在领先的工艺节点中使用比 Nvidia 更少的芯片面积。作为交换,AMD 必须支付更昂贵的封装解决方案费用,因为简单的封装走线在处理 GPU 的高带宽要求方面表现不佳。

Nvidia 将所有东西都放在一个更大的芯片上,采用尖端的 4 纳米节点。这使得 4080 的 VRAM 带宽和缓存比 7900 XTX 更少。它们的晶体管密度在技术上低于 AMD,但这是因为 Nvidia 更高的 SM 数量意味着与寄存器文件和 FMA 单元相比它们具有更多的控制逻辑。每个 SM 更少的执行单元意味着 Ada Lovelace 将更容易让这些执行单元得到满足。

Nvidia 还具有更简单的缓存层次结构的优势,它仍然提供相当大的缓存容量。

无论如何,很高兴看到 AMD 和 Nvidia 在 Nvidia 多年无可置疑的领先优势之后继续正面交锋。希望这会导致未来 GPU 价格下降,以及双方更多的创新。

编辑:黄飞

电子发烧友App

电子发烧友App

评论