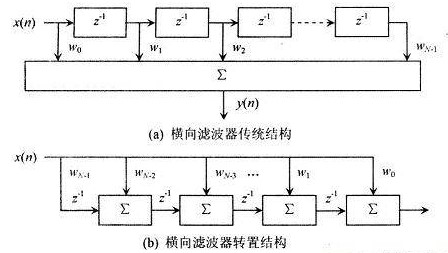

FIR 滤波器广泛应用于数字信号处理中,主要功能就是将不感兴趣的信号滤除,留下有用信号。##全并行FIR滤波器结构

2014-06-27 10:02:56 8178

8178 FIR 滤波器广泛应用于数字信号处理中,主要功能就是将不感兴趣的信号滤除,留下有用信号。##脉动型(Systolic)FIR滤波器设计

2014-06-30 09:47:40 1872

1872 在Matlab/Simulink环境下,采用DSP Builder模块搭建FIR模型,根据FDATool工具对FIR滤波器进行了设计,然后进行系统级仿真和ModelSim功能仿真,其仿真结果表明

2013-10-08 13:39:06 8661

8661

169数字FIR滤波器

2010-04-07 14:44:08

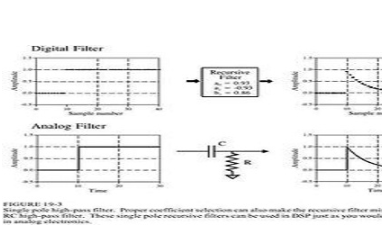

1、FIR 滤波器是在数字信号处理(DSP)中经常使用的两种基本的滤波器之一,另一个为IIR滤波器。 2、FIR代表有限冲激响应(Finite Impulse Response)的简称。 3

2011-09-24 16:05:53

,所以经济而效率高。但是这个高效率是以相位的非线性为代价的。选择性越好,则相位非线性越严重。相反,FIR滤波器却可以得到严格的线性相位,然而由于FIR滤波器传输函数的极点固定在原点(输出只与有限项输入

2018-03-12 13:21:07

,所以经济而效率高。但是这个高效率是以相位的非线性为代价的。选择性越好,则相位非线性越严重。相反,FIR滤波器却可以得到严格的线性相位,然而由于FIR滤波器传输函数的极点固定在原点(输出只与有限项输入

2016-08-08 08:49:32

输入数据和历史输入数据,IIR的滤波输出取决于当前输入数据、历史输入数据和历史输出数据。以基于FPGA硬件的数字滤波器为例,FIR在处理信号时不需等待前一个信号的滤波输出,只需要考虑输入数据便可实时

2019-06-27 04:20:31

FIR滤波器的实现方法有哪几种?基于Verilog HDL的FIR数字滤波器设计与仿真

2021-04-09 06:02:50

数字滤波器的类型有FIR(有限长冲击与IIR(无限长。离散数字系统中,滤波器的表述为差分方程。FIRFIR基本特性:FIR 滤波器永远是稳定的(系统只有零点);FIR 滤波器的冲激响应是有限长序列

2021-08-17 06:19:17

第一个问题的基础上,我是设置unsigned还是signed?3、滤波器的设计,我要给他什么样子的输入,仿真看得出什么样子的结果?部分代码如下

2017-05-09 14:18:17

使用iir滤波器相对fir滤波器可以在使用更小的阶数的情况下实现更好的效果。实验证明,可能20阶的iir效果堪比500阶左右的fir滤波器效果。首先放出iir的matlab仿真代码:%本程

2021-12-22 08:29:40

fpga实现滤波器fpga实现滤波器在利用FPGA实现数字信号处理方面,分布式算法发挥着关键作用,与传统的乘加结构相比,具有并行处理的高效性特点。本文研究了一种16阶FIR滤波器的FPGA设计方法

2012-08-12 11:50:16

。本文研究了一种16阶FIR滤波器的FPGA设计方法,采用Verilog HDI语言描述设计文件,在Xilinx ISE 7.1i及ModelSim SE 6.1b平台上进行了实验仿真及时序分析,并探讨了实际工程中硬件资源利用率及运算速度等问题。

2012-08-11 18:27:41

CIC抽取滤波器MATLAB仿真和FPGA实现(1)设计理想滤波器目标:1、滤波器在有效频段内纹波满足设计要求。2、抽取或内插处理后在有效频段内不产生混叠。3、滤波器实现简单,需要资源较少。这个

2021-08-17 08:27:40

最近在做一个FPGA的课程设计,遇到一个比较烦人的问题,希望大神们可以指点迷律。一个16阶的FIR滤波器,采用分布式算法实现的,采样率1M,fc=100K,频率到了30K以上时就会出现那些尖刺,很

2018-02-25 19:25:50

FIR滤波器如何定义?为什么要使用FIR滤波器?

2021-04-06 07:48:45

设计了一个基于FPGA的FIR滤波器,用的是分布式算法,在波形仿真时出现了以下问题,请大牛们指点一下,谢谢!代码太多不方便放上来,希望有遇到相同情况或者知道如何解决的大神指点一下

2018-02-22 20:10:50

最近进行FPGA学习,使用FIR滤波器过程中出现以下问题:使用FIR滤波器IP核中,输入数据为1~256,滤波器系数为,coef =-1469,-14299 ,-2185,10587

2018-11-02 17:17:57

基于FPGA的FIR滤波器IP仿真实例 AT7_Xilinx开发板(USB3.0+LVDS)资料共享 腾讯链接:https://share.weiyun.com/5GQyKKc 百度网盘链接

2019-07-16 17:24:22

里面详细的说明了FIR原理,以及在MATLAB上仿真和在FPGA上实现FIR的过程。

2019-07-22 11:52:43

设计要求: 利用所学知识,采用VHDL语言完成FIR滤波器的设计仿真。要求用VHDL编程设计底层文件,顶层文件可任意(可用原理图方式或文本方式);完成仿真文件(包括MATLAB和QUARTUSII

2015-09-18 14:54:46

DSPBuilder设计了一个4阶FIR滤波器,并用QuartusII进行硬件仿真,仿真结果表明设计FIR滤波器的正确性。同时使用IPCore开发基于FPGA的FIR数字滤波器,利用现有的IPCore在FPGA器件上实现滤波器设计。

2012-08-11 15:32:34

基于FPGA的FIR数字滤波器的优化设计

2012-08-17 23:55:09

(FIR)滤波器和无限脉冲响应(IIR)滤波器两种。其中FIR数字滤波器具有严格的线性相位,而且非递归结构也保证了运算的稳定性。

2019-09-29 07:45:43

基于FPGA的fir滤波器实现

2017-08-28 19:57:36

本帖最后由 eehome 于 2013-1-5 09:59 编辑

基于FPGA的高阶FIR滤波器设计

2012-08-20 18:42:15

本帖最后由 eehome 于 2013-1-5 09:50 编辑

基于fpga的fir滤波器的实现

2012-08-17 16:42:33

Programmable Gate Array,现场可编程门阵列)基于查找表的结构和全硬件并行执行的特性,如何用FPGA 来实现高速FIR 数字滤波器成了近年来数字信号处理领域研究的热点。目前,全球两大PLD 器件供应商都提供了加速FPGA 开发的IP(IntelligentProperty,知识产权)核。

2019-09-05 07:21:15

系统兼具实时性和灵活性,而现有设计方案(如DSP)则难以同时达到这两方面要求。而使用具有并行处理特性的FPGA实现FIR滤波器,具有很强的实时性和灵活性,因此为数字信号处理提供一种很好的解决方案。

2019-11-04 08:08:24

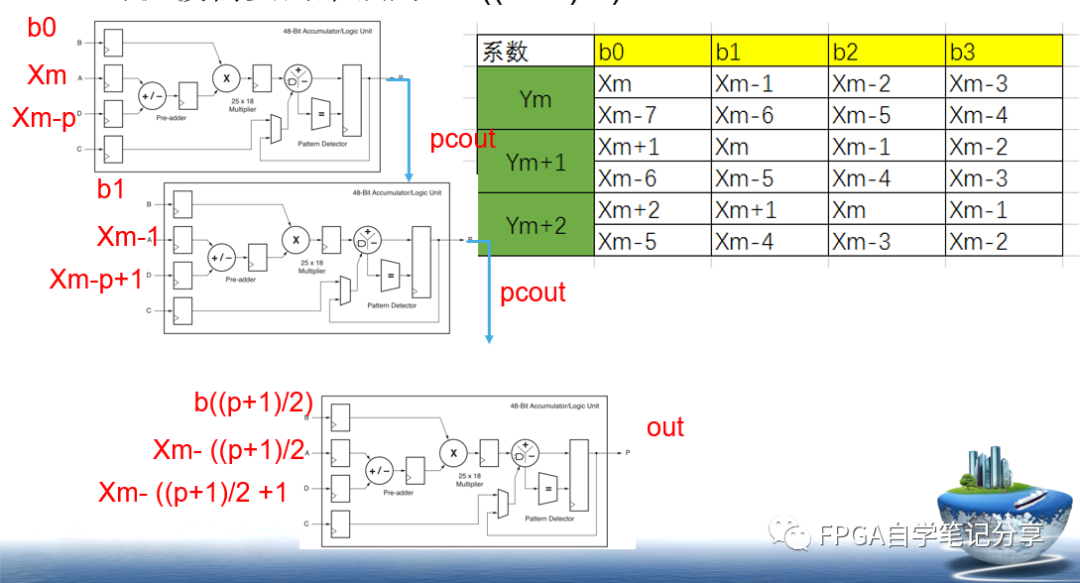

本文首先介绍了FIR滤波器和脉动阵列的原理,然后设计了脉动阵列结构的FIR滤波器,画出电路的结构框图,并进行了时序分析,最后在FPGA上进行验证。结果表明,脉动阵列的模块化和高度流水线的结构使FIR

2021-04-20 07:23:59

此示例显示如何设计低通FIR滤波器。这里介绍的许多概念可以扩展到其他响应,如高通,带通等。FIR滤波器被广泛使用,因为它们具有强大的设计算法,以非递归形式实现时的固有稳定性,可以轻松实现线性

2018-08-23 10:00:16

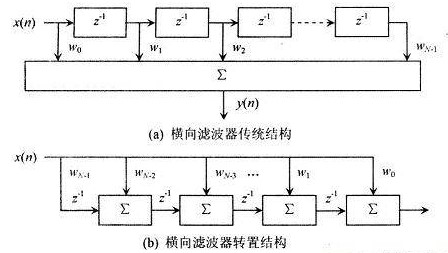

FIR滤波器的原理及结构是什么基于分布式算法的FIR滤波器的实现

2021-05-08 08:39:41

宽的运算步进浪费资源而且也没有必要。在MATLAB中将滤波器系数量化为指定位宽,会改变滤波器的频率特性,因此需要做好仿真,确定量化后的系数也能满足FIR的设计需求。由上节可知FPGA最方便实现的是直接

2020-09-25 17:44:38

并行流水结构FIR的原理是什么基于并行流水线结构的可重配FIR滤波器的FPGA实现

2021-04-29 06:30:54

目前FIR滤波器的硬件实现的方式有哪几种?怎么在FPGA上实现FIR滤波器的设计?

2021-05-07 06:03:13

本文以实现抽取率为2的具有线性相位的3阶FIR抽取滤波器为例,介绍了一种用XC2V1000型FPGA实现FIR抽取滤波器的设计方法。

2021-05-07 06:02:47

相对无限冲击响应(IIR)滤波器,有限冲击响应(FIR)能够在满足滤波器幅频响应的同时获得严格的线性相位特性,而数据通信、语音信号处理等领域往往要求信号在传输过程中不能有明显的相位失真,所以FIR

2019-08-23 06:39:46

相对无限冲击响应(IIR)滤波器,有限冲击响应(FIR)能够在满足滤波器幅频响应的同时获得严格的线性相位特性,而数据通信、语音信号处理等领域往往要求信号在传输过程中不能有明显的相位失真,所以FIR

2019-08-27 07:16:54

最近在学习全相位滤波器,请问有人做过全相位FIR滤波器吗?能不能用matlab程序来比较一下全相位FIR滤波器与传统方法设计的FIR滤波器有什么区别??希望有人能帮我解答。。。感激不尽。。。。

2011-05-10 15:34:03

要做毕设,用proteus仿真,单片机实现的fir数字滤波器,我已经用matlab设计出来了fir滤波器的系数,怎么用单片机语言实现,还有用proteus仿真?求大神们指导啊,马上就答辩了,还没有做出来仿真。

2014-05-22 11:27:55

的滤波输出取决于当前输入数据、历史输入数据和历史输出数据。以基于FPGA硬件的数字滤波器为例,FIR在处理信号时不需等待前一个信号的滤波输出,只需要考虑输入数据便可实时滤波;IIR需要等待上一个信号

2023-05-29 16:47:16

AD9361的FIR滤波器是否可以配置成RRC滤波器?只能用作低通滤波器吗?另外,FIR滤波器的2/4倍插值是对原信号进行补0吗?

2019-01-07 11:31:53

FIR滤波器是什么?DSPBuilder是什么?FIR数字滤波器的DSPBuilder设计

2021-04-30 07:14:19

、FIR滤波器的FPGA实现好了,matlab仿真成功,剩下的就需要在FPGA上实现了,在FPGA上实现什么呢?前面我们已经得到了滤波器的系数,只要有了滤波器系数,剩下的不就是乘积累加了么,所以,我们需要

2015-06-16 19:25:35

用窗函数设计FIR滤波器一、实验目的1、熟悉FIR滤波器设计的基本方法。2、掌握用窗函数设计FIR数字滤波器的原理及方法,熟悉相应的计算机高级语言编程。3、熟悉线性

2009-05-10 10:02:15 97

97 本文提出了一种采用现场可编程门阵列器件 FPGA 实现FIR 字滤波器硬件电路的方案,该方案基于只读存储器ROM 查找表的分布式算法。并以一个十六阶低通FIR 数字滤波电路在ALTERA 公

2009-08-31 16:47:47 44

44 本文介绍了能高效实现固定常数乘法的分布式算法原理,给出了在FPGA 中用查找表实现FIR滤波器的算法设计,并以一个16 阶低通滤波器为例说明了设计过程。该设计通过Altera 公司的EP

2009-09-02 10:10:02 10

10 基于FPGA对称型FIR滤波器的设计与实现:在基于FPGA的对称型FIR数字滤波器设计中,为了提高速度和运行效率,提出了使用线性I相位结构和加法树乘法器的方法,并利用Altera公I司的FPG

2009-09-25 15:38:38 30

30 :FIR 数字滤波器由于具有诸多优点,因而在数字信号处理中得到了十分广泛的应用。介绍了MATLAB 环境下FIR 数字滤波器的设计、仿真和基于TMS320VC5416DSP 硬件平台的实现。详细描述

2009-12-16 13:31:22 58

58 分析了FIR数字滤波器的基本原理,在MATLAB环境下利用窗函数设计FIR低通滤波器,实现了FIR低通滤波器的设计仿真。将设计的符合要求的滤波器在TI公司DSPTMS320LF2407A上实现。通过

2009-12-18 15:53:56 101

101 什么是fir数字滤波器

Part 1: Basics1.1 什么是FIR滤波器?FIR 滤波器是在数字信号处理(DSP)中经常使用的两种

2008-01-16 09:42:22 16243

16243 基于流水线技术的并行高效FIR滤波器设计

基于流水线技术,利用FPGA进行并行可重复配置高精度的FIR滤波器设计。使用VHDL可以很方便地改变滤波器的系数和阶数。在DSP中采用

2009-03-28 15:12:27 737

737

如何用用FPGA实现FIR滤波器

你接到要求用FPGA实现FIR滤波器的任务时,也许会想起在学校里所学的FIR基础知识,但是下一步该做什么呢?哪些参数是重

2009-03-30 12:25:45 4503

4503

摘要: 针对在FPGA中实现FIR滤波器的关键--乘法运算的高效实现进行了研究,给了了将乘法化为查表的DA算法,并采用这一算法设计了FIR滤波器。通过FPGA仿零点验证

2009-06-20 14:09:36 677

677

FIR 滤波器FAQ (基本知识问答)

1.1 什么是FIR滤波器?

FIR 滤波器是在数字信号处理(DSP)中经常使用的两种基本的滤波器之一

2009-10-30 08:06:45 1301

1301

FIR带通滤波器的FPGA实现

引 言 在FPGA应用中,比较广泛而基础的就是数字滤波器。根据其单位冲激响应函数的时域特性可分为无限冲击响应(Infinite

2009-11-13 09:55:18 6564

6564

目前FIR滤波器的一般设计方法比较繁琐,开发周期长,如果采用设计好的FIR滤波器的IP核,则开发效率大为提高。本方案基于Altera公司的Cyclone II系列芯片EP2C8Q208C8N,首先利用MATLAB中的滤

2011-05-06 16:01:30 84

84 基于流水线技术,利用FPGA进行并行可重复配置高精度的 FIR滤波器 设计。使用VHDL可以很方便地改变滤波器的系数和阶数。在DSP中采用这种FIR滤波器的设计方法可以充分发挥FPGA的优势。

2011-07-18 17:09:28 63

63 充分利用有限冲击响应数字滤波器(Finite Impulse Response digital filter ,FIR)系数的对称特性,借助于MATLAB语言和现场可编程门阵列(FPGA)实现了一种高效的 低通滤波器 。设计过程中通过

2011-08-05 14:23:07 82

82 目前数字滤波器的硬件实现方法通常采用专用DSP芯片或FPGA,本文从FIR滤波器的系数考虑,采用CSD编码,对FIR数字滤波器进行优化设计。

2011-08-16 10:54:41 3632

3632

本文首先对CIC、HB、FIR滤波器的原理及设计作了简单的说明,最后用Matlab结合System generator对本文所设计的DDC滤波器作了一个仿真。

2012-08-06 15:34:48 10298

10298

数字滤波器是数字信号处理领域内的重要组成部分。FIR滤波器又以其严格的线性相位及稳定性高等特性被广泛应用。本文结合MATLAB工具软件介绍了FIR数字滤波器的设计方法,并在Xilinx的

2012-09-25 11:34:08 120

120 描述了基于FPGA的FIR滤波器设计。根据FIR的原理及严格线性相位滤波器具有偶对称的性质给出了FIR滤波器的4种结构,即直接乘加结构、乘法器复用结构、乘累加结构、DA算法。在本文中给

2012-11-09 17:32:37 121

121 fir滤波器的有关资料 fir_滤波器sourc.rar

2015-12-14 14:12:56 24

24 基于matlab和fpga的FIR滤波器设计,有兴趣的同学可以下载学习

2016-04-27 15:51:58 56

56 基于FPGA的FIR滤波器设计与实现,下来看看

2016-05-10 11:49:02 38

38 基于MATLAB的FIR滤波器设计与滤波。

2016-12-14 22:08:25 63

63 基于FPGA实现变采样率FIR滤波器的研究

2017-01-08 15:59:09 19

19 数字滤波器广泛应用于硬件电路设计,一般分为FIR滤波器和IIR滤波器。那么FIR滤波器和IIR滤波器有什么区别呢?本文通过几个例子做一个简单的总结。

2017-05-03 11:36:31 19

19 研究了一种采用FPGA实现32阶FIR滤波器硬件电路方案;讨论了窗函数的选择、滤波器的结构以及系数量化问题;研究了FIR滤波器的FPGA实现,各模块的设计以及如何优化硬件资源,提高运行

2017-11-10 16:41:57 15

15 针对传统的FIR 滤波器的缺点,介绍了一种基于FPGA 乘法器的FIR 滤波器设计方法,该滤波器利用FPGA 自带的18位乘法器MULT18 × 18SIO 进行乘法计算,利用寄存器对相乘结果进行

2017-11-22 07:39:45 2735

2735

本文针对快速、准确选择参数符合项目要求的滤波器设计方法的目的,通过系统的介绍有限脉冲响应( Finite Impulse Response,FIR)滤波器的原理、结构形式以及几种FIR滤波器设计方法

2017-12-21 14:53:14 14

14 文介绍了FIR抽取滤波器的工作原理,重点阐述了用XC2V1000实现FIR抽取滤波器的方法,并给出了仿真波形和设计特点。

2018-04-19 11:34:00 1846

1846

用FPGA实现抽取滤波器比较复杂,主要是因为在FPGA中缺乏实现乘法运算的有效结构,现在,FPGA中集成了硬件乘法器,使FPGA在数字信号处理方面有了长足的进步。本文介绍了一种采用Xilinx公司的XC2V1000实现FIR抽取滤波器的设计方法。

2018-04-28 11:50:00 1073

1073

基于灵活自适应的空口波形技术FOFDM(Filtered OFDM)是现代通信技术的研究热点,设计并实现可调FIR滤波器是实现该技术的核心工作之一。本文设计的基于FPGA的可调节FIR滤波器系数

2018-07-23 17:21:00 2372

2372

在数字信号处理领域,滤波器无疑是个非常重要的环节。而在数字滤波器中,有限脉冲响应(FIR)滤波器因为其线性相位的特点,应用尤为广泛。实际应用中FIR滤波器分为常系数FIR滤波器和变系数FIR滤波器

2019-04-22 08:07:00 5006

5006

用FPGA实现抽取滤波器比较复杂,主要是因为在FPGA中缺乏实现乘法运算的有效结构,现在,FPGA中集成了硬件乘法器,使FPGA在数字信号处理方面有了长足的进步。本文介绍了一种采用Xilinx公司的XC2V1000实现FIR抽取滤波器的设计方法。

2020-09-25 10:44:00 3

3 你知道FIR滤波器与IIR滤波器的不同点吗?它有有什么特点?滤波器是工程师工作中必不可少的器件,滤波器分为很多种,本文详细介绍一下FIR滤波器与IIR滤波器之间的区别。

2020-08-09 14:15:00 31385

31385

本文档的主要内容详细介绍的是使用DSP设计和仿真FIR滤波器包括了:dsp builder profile和基本设计流程和fir的设计过程及注意事项

2020-09-01 16:02:00 12

12 提出一种新的高阶FIR滤波器的FPGA实现方法。该方法运用多相分解结构对高阶FIR滤波器进行降阶处理,采用改进的分布式算法来实现降阶后的FIR滤波器。设计了一系列阶数从8到1 024的FIR滤波器

2021-03-23 15:44:54 30

30 数字滤波器从实现结构上划分,有FIR和IIR两种。FIR的特点是:线性相位、消耗资源多;IIR的特点是:非线性相位、消耗资源少。由于FIR系统的线性相位特点,设计中绝大多数情况都采用FIR滤波器。

2022-04-24 14:40:16 2492

2492 1.根据冲激响应的不同,将数字滤波器分为有限冲激响应(FIR)滤波器和无限冲激响应(IIR)滤波器。对于FIR滤波器,冲激响应在有限时间内衰减为零,其输出仅取决于当前和过去的输入信号值。对于IIR

2022-12-30 23:45:05 2276

2276 本文介绍了设计滤波器的FPGA实现步骤,并结合杜勇老师的书籍中的串行FIR滤波器部分进行一步步实现硬件设计,对书中的架构做了简单的优化,并进行了仿真验证。

2023-05-24 10:56:34 552

552

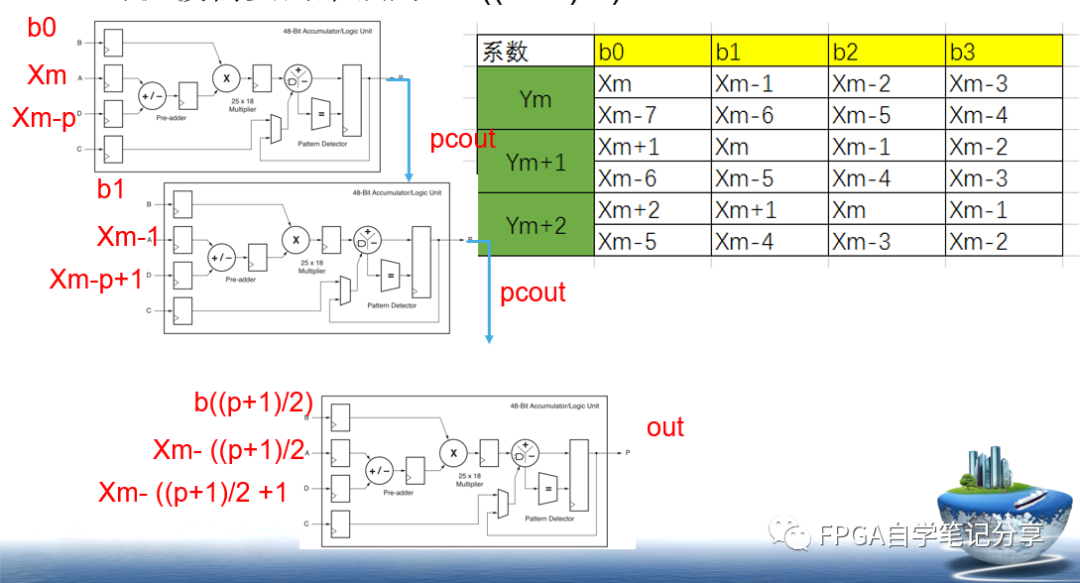

本文介绍了设计滤波器的FPGA实现步骤,并结合杜勇老师的书籍中的并行FIR滤波器部分进行一步步实现硬件设计,对书中的架构做了复现以及解读,并进行了仿真验证。

2023-05-24 10:57:36 653

653

点击上方 蓝字 关注我们 本文将回顾对称 F IR 滤波器 的高效 FPGA 实现的注意事项。 本文将推导对称 FIR 滤波器的模块化流水线结构。我们将看到派生结构可以使用 Xilinx

2023-05-26 01:20:02 441

441

上文 FPGA数字信号处理之滤波器2_使用dsp48e1的fir滤波器设计完成了结构设计。

2023-06-02 12:36:22 718

718

数字滤波器是数字信号处理中最常用的一种技术,可以对数字信号进行滤波、降噪、增强等处理,其中最常见的两种数字滤波器是IIR滤波器和FIR滤波器。本文将从IIR滤波器和FIR滤波器的原理、特点和应用等方面进行详细介绍,以便更好地理解两种滤波器的区别。

2023-06-03 10:21:43 12909

12909 电子发烧友网站提供《如何使用HLS加速FPGA上的FIR滤波器.zip》资料免费下载

2023-06-14 15:28:49 1

1 FIR(Finite Impulse Response,有限脉冲响应)滤波器是一种数字滤波器,其输出信号仅由输入信号和滤波器的冲激响应决定。FIR滤波器的名称源于其冲激响应是一个有限长度的序列。

2023-06-20 11:26:04 787

787

电子发烧友App

电子发烧友App

评论