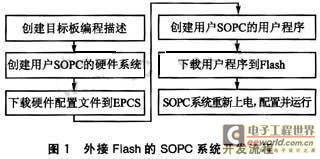

摘要 讨论Intel StrataFlash 3V Memory系列的JS28F128J3D75并行NOR Flash在基于Xilinx MicroBlaze的SOPC开发中的4种不同用途。J3D Flash可以用于存储FPGA配置比特流、可引导的软处理器代码、可直接执行的软处理器代码,以及非易失的数据或参数。本文给出了这4种用途的应用方法与技巧,指出了应该特别注意的技术细节,这些方法与技巧可以直接应用到SOPC项目开发中。

关键词 StrataFlash并行NOR FlashSOPCMicroBlazeJS28F128J3D

引言

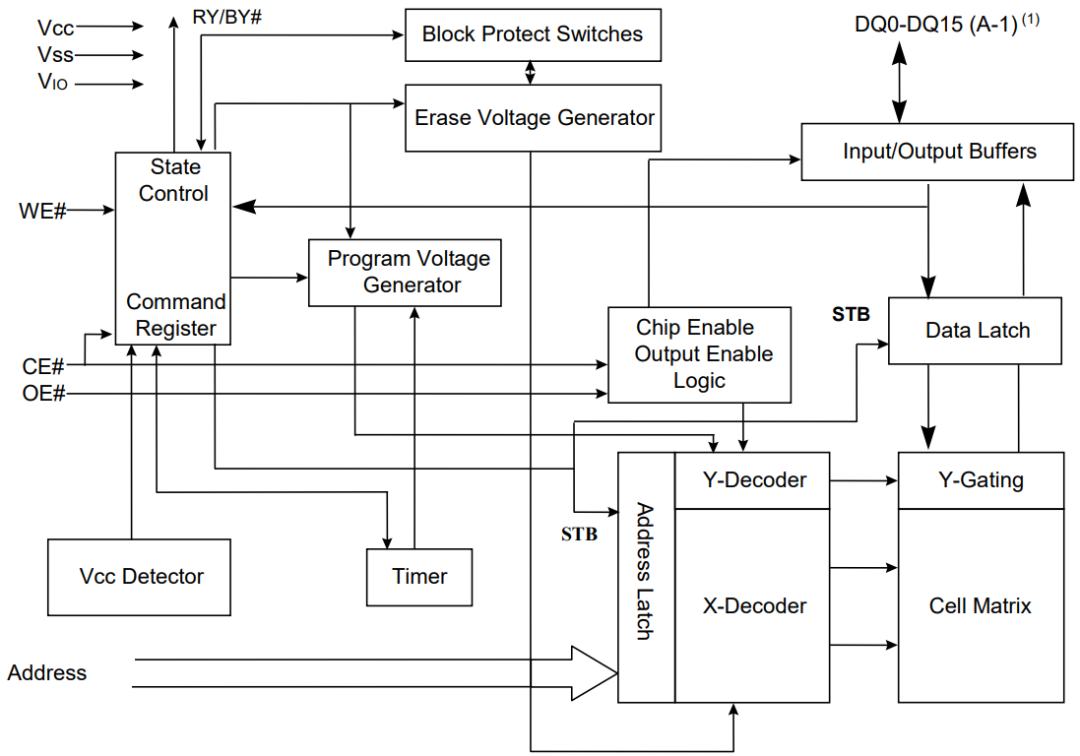

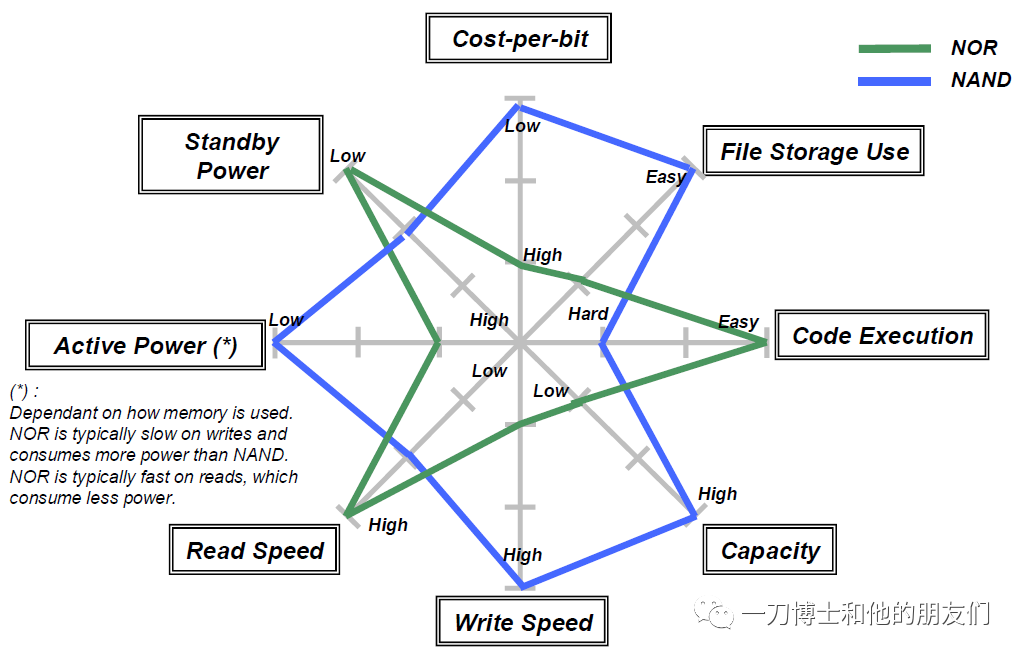

随着FPGA技术的发展,出现了一种新概念的嵌入式系统,即SOPC(System On Programmable Chip)。SOPC技术融合了SoC和FPGA的优点,将处理器、片上总线、片上存储器、内部外设、I/O接口以及自定义逻辑集成在同一片FPGA中,而且软硬件可裁剪、可升级、可修改,具有软硬件在系统编程能力,在保证高性能的同时具有非常高的灵活性。由于大部分功能部件在FPGA内实现,外部只需要很少的器件,如大容量的RAM、Flash、DAC、ADC等。在系统需要脱离计算机独立运行时(绝大部分情况如此),非易失的存储器件Flash是必不可少的。Flash可以用来存储配置比特流、代码、数据或参数等重要信息。本文以Intel StrataFlash 3V Memory系列的JS28F128J3D75并行NOR Flash(简称“J3D”)和Xilinx FPGA Spartan3E系列的XC3S1600E(简称“1600E”)为背景,在结合项目开发经验和参阅相关文献的基础上,介绍了并行NOR Flash在SOPC开发中的4种不同应用。

1 存储FPGA配置比特流

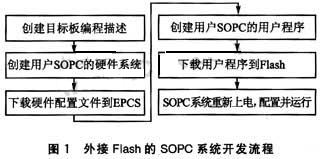

1600E工作在BPI(Bytewide Peripheral Interface)配置模式时,通过专门的引脚与J3D连接,这些引脚在配置完成后可以作为用户I/O使用。连接时,大部分引脚参考1600E的数据手册直接连接即可,但有些引脚需要特别注意。J3D有×8(数据总线宽度为8位)和×16(数据总线宽度为16位)两种工作模式。配置时应工作在×8模式,配置完成后,根据需要可以设置为×8或×16模式。图1为1600E与J3D引脚连接示意图。

若配置后需要切换至×16模式,则需综合考虑1600E的HSWAP脚。HSWAP接高电平时,1600E所有用户I/O的内部上拉电阻禁用,HDC通过4.7 kΩ电阻接高电平,LDC2通过4.7 kΩ电阻接地,LDC1和LDC0通过4.7 kΩ电阻接高电平,同时这3个信号应分别连到J3D的BYTE#、OE#、CE0脚。这样上电后的瞬间,J3D工作在×8模式,且因CE0脚被拉高而处于非选中状态,不会导致对J3D的误操作;然后在1600E的控制下进入配置状态,配置结束可通过控制LDC2输出高电平而将J3D切换为×16模式。HSWAP接低电平时,1600E所有用户I/O的内部上拉电阻使能,LDC1、LDC0和HDC无需外接上拉电阻;而LDC2应接340 Ω的下拉电阻,以使上电后J3D工作在×8模式,从而顺利进入配置状态,配置结束后可将J3D切换为×16模式。

图1 1600E与J3D引脚连接示意图

若配置后工作在×8模式,则J3D的BYTE#脚接低电平,1600E的LDC2悬空。当HSWAP接高电平时,LCD1和LCD0分别连至OE#、CE0脚,同时应通过4.7 kΩ电阻上拉;HSWAP接低电平时,LCD1和LCD0不用上拉。

配置比特流文件首先通过iMPCT转换成MCS文件,再通过PicoBlaze NOR Flash Programmer(http://www.xilinx.com/products/boards/s3estarter/files/

s3esk_picoblaze_nor_flash_programmer.zip)下载到J3D中。

J3D可以同时配置多块FPGA,也可对同一块FPGA进行多比特流配置。例如先配置一个诊断测试比特流,测试成功后,再重新配置应用比特流。

2 存储可引导的软处理器代码

首先利用Xilinx嵌入式开发工具箱EDK创建一个嵌入式工程,包括MicroBlaze硬件平台和相应的软件工程。在EDK界面下,用鼠标选中创建的软件工程,右击并在弹出的菜单中选择Generate Linker Script...项,进入Generate Linker Script对话框。将Sections、Heap和Stack指定到BRAM或外部RAM(一般将Heap和Stack指定到BRAM,代码和数据段指定到外部RAM),并指定输出脚本文件名及路径,如图2所示。

双击相应软件工程下的Compiler Options选项,进入Set Compiler Options对话框,设定Link Script项为刚才产生的脚本文件,并指定Output ELF File项的路径与名称。现在可以编译相应的软件工程,产生相应的可执行ELF文件,设为Bootable.elf。

图2 Generate Linker Script对话框

在EDK主界面下,用鼠标选择Device Configuration → Program Flash Memory,进入Program Flash Memory对话框,并按图3进行设置。单击OK按钮,会把Bootable.elf文件自动转为SREC格式,并下载到J3D的指定地址处,同时产生名为bootloadr_0的软件工程。bootloadr_0工程编译后产生的可执行文件executable.elf用来执行引导装载功能,应将其合并到系统比特流system.bit,从而生成dowload.bit。dowload.bit经iMPCT转为MCS文件后下载到配置PROM中(若使用同一片J3D,注意不能与Bootable.elf发生地址空间冲突)。这样,系统上电后,首先对FPGA进行配置,然后引导加载J3D中的代码至相应的BRAM或SDRAM中(具体映射位置已在Generate Linker Script对话框中设定)。

图3 Program Flash Memory对话框

3 存储可直接执行的软处理器代码

这里仍然使用上面创建的EDK工程,由于J3D具有类似SRAM的接口,上电后可以直接像SRAM一样进行读操作,但却不能直接进行写操作。因此,应将只读段.code、.rodata、.sdata2、.sbss2指定到J3D中,其余段指定到BRAM中,这可以在Generate Linker Script对话框中完成。重新编译后生成新的Bootable.elf文件。此时,Bootable.elf仍是一个整体,需要将其在物理上分为2个文件: 一个存放只读段,另一个存放其余段。具体可以通过下面的操作实现。

① 创建存储在BRAM中的镜像volatile.elf。在XPS中,选择Project → Launch EDK Shell,并执行下列命令:

$ mbobjcopy \

--set-section-flags .text=alloc,readonly,code \

--set-section-flags .init=alloc,readonly,code \

--set-section-flags .fini=alloc,readonly,code \

--set-section-flags .rodata=alloc \

--set-section-flags .sdata2=contents \

--set-section-flags .sbss2=contents \

./TestApp_Memory/Bootable.elf\

./TestApp_Memory/volatile.elf

② 创建存储在Flash中的镜像J3D.bin。在XPS中,选择Project → Launch EDK Shell,并执行下列命令:

$ mbobjcopy O binary

-j .text \

-j .init \

-j .fini \

-j .rodata \

-j .sdata2 \

-j .sbss2 \

./TestApp_Memory/Bootable.elf \

./TestApp_Memory/J3D.bin

将volatile.elf合并到系统配置比特流system.bit,生成dowload.bit,再经iMPCT转为MCS格式后下载到配置PROM中。再将J3D.bin通过Program Flash Memory对话框下载到J3D中。这样系统上电并完成配置后,J3D中的代码无需引导便可以直接执行。

4 存储非易失数据或参数

有时候系统需要存储非易失的数据或参数,这就需要通过编写程序直接对J3D进行读/写操作。当然,前提是先要在EDK中为J3D添加一个XPS MCH EMC接口。这个接口对并行NOR Flash和SRAM来说都是适用的,如果用于SRAM则可以直接读/写,不需要驱动,而用于并行Flash则需要自己编写相应的驱动程序。下面为自行编写的一个执行块擦除、单字写、单字读操作的程序。需要注意的是: 写操作前一定要先进行擦除操作,写命令或写数据之后一定要对状态寄存器进行判断是否完成相应操作;读操作则很简单,像SRAM的读/写一样。

Xuint16 data=0xF0F0;

Xuint16 Status,ReadData;

/*块擦除程序*/

XIo_Out16(XPAR_FLASH_16MX8_MEM0_BASEADDR,0x2020 );//指定地址块的擦除设置

XIo_Out16(XPAR_FLASH_16MX8_MEM0_BASEADDR,0xD0D0 );//指定地址块的擦除确认

do{

Status = XIo_In16(XPAR_GENERIC_EXTERNAL_MEMORY_MEM0_BASEADDR);

}while ((Status & 0x0080) != 0x0080);//读状态寄存器直至块擦除完成

/*单字写程序*/

XIo_Out16(XPAR_FLASH_16MX8_MEM0_BASEADDR,0x4040 );//指定地址处单字写操作设置

XIo_Out16(XPAR_FLASH_16MX8_MEM0_BASEADDR,data );//向指定地址处写入一个字长的数据

do{

Status = XIo_In16(XPAR_GENERIC_EXTERNAL_MEMORY_MEM0_BASEADDR);

}while ((Status & 0x0080) != 0x0080);//读状态寄存器直至写操作完成

/*单字读程序*/

ReadData=XIo_In16(XPAR_FLASH_16MX8_MEM0_BASEADDR );//读相应地址处的数据

还有一种情况是在系统运行前就把数据写入Flash中。首先,把数据写入一个二进制文件中。注意,MicroBlaze的存储格式是BigEndian(即高字节数据保存在低地址,低字节数据保存在高地址),PC机的存储格式则是LittleEndian(即高字节数据保存在高地址,低字节数据保存在低地址),因此如果是用VC++产生的二进制文件,一定要进行高、低字节交换。在Matlab中生成数据文件则可以在相应的文件操作函数中添加参数'b'(表示以BigEndian格式存储),如FileID=fopen('data.bin','w+','b')。产生的二进制文件可以通过Program Flash Memory对话框下载到J3D中,注意不要选中Auto?convert file to SREC format when programming flash和Create Flash Bootloader Application选项。

结语

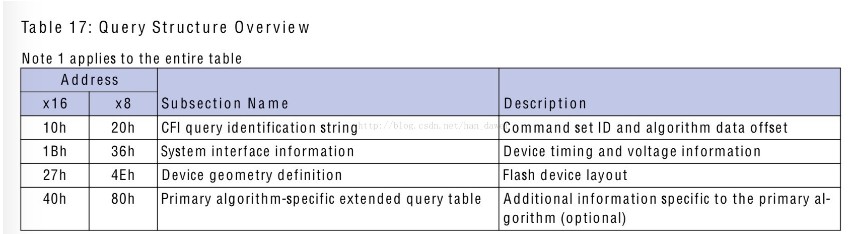

本文讨论了在以Xilinx Spartan XC3S1600E为基础的SOPC设计中,Intel J3D并行NOR Flash的4种不同用途及其使用方法与技巧,尤其对一些技术关键问题予以详细的阐述,其中融入了笔者在项目开发中的实际经验,具有较高的参考价值。J3D既可以用于存储FPGA配置比特流,又可以存储软处理器程序代码,也可以存储非易失的数据和参数,甚至三者可以并存于同一片J3D中。本文只是以Intel J3D并行NOR Flash为例讨论其在SOPC开发中的用法,这些方法同样适用于其他厂家具有CFI(Common Flash Interface)接口的并行NOR Flash。灵活地综合运用这些方法,对于SOPC开发具有重要意义。

电子发烧友App

电子发烧友App

评论