高速收发器(SERDES)的运用范围十分广泛, 包括通讯、计算机、工业和储存,以及必须在芯片与芯片/模块之间、或在背板/电缆上传输大量数据的系统。但普通高速收发器的并行总线设计已无法满足现在的要求。将收发器整合在FPGA中,成为解决这一问题的选择办法。

高速设计用FPGA

具备嵌入式数Gb收发器的低功耗FPGA架构,它能让设计人员利用高生产率的EDA工具提供实体层和逻辑层建构模块,研发出低成本的小型系统,使得设计师能够快速解决协议和速率的变化问题,以及为了提高性能和增加新功能时,必须进行设计修改所面临的重新编程问题,这些迫切需求的灵活性无法在ASIC和ASSP方案中获得。FPGA提供了一种单芯片解决方案,克服了多芯片方案中的互通作业、布线和功率问题。FPGA中的收发器在克服讯号完整性问题的同时,也能工作在一系列不同的系统或协议环境中。

收发器选择考虑

收发器的选择对于要获得所需的功能设计而言相当关键。设计师必须在设计初期阶段就分析收发器的功能和性能,并融合频宽需求、协议、多媒体类型、EMC和互通作业性所决定的设计准则指导选择。收发器的选择应该包括规格的符合性验证;针对抖动、噪音、衰减和不连续性等不利条件下的免疫能力或补偿能力;以及应用中的传输媒介的类型。根据目前多数组件存在的收发器错误纪录,不难发现将混合讯号收发器整合在数字电路FPGA中仅取得了有限的成功。因此,系统设计师在验证市场需求时要特别小心,要紧盯着制程、电压、温度、核心以及I/O端口,还有硅芯片生产能力等各方面的验证工作。

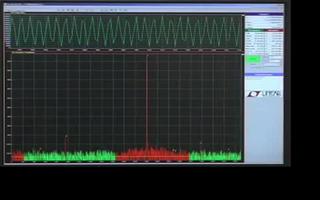

评估收发器发射性能的重要工具是眼图。这是建构在一系列分层PRBS周期上的发射机波形图量度。透过利用眼状模板,眼图可用来显示特定指针的符合性。如果波形没有侵占眼图模板的张开区,通常意味着它符合抖动、噪音和幅度指针。另外,为确保采用随机性较高的PRBS序列,并将在示波器上撷取的波形采样数量减到最少,以便它们不会被错误地表征较差的PRBS性能,需要一个非常谨慎的方案。

在决定生产制程时,收发器眼图性能更显重要。在选择正确组件时还有下述许多其它因素要考虑。

讯号完整性

对芯片内或芯片与模块间的通讯来说,无论通讯是透过背板、电缆还是同一电路板上的直接连接,具有嵌入式收发器的FPGA都是理想的选择。用串行收发器取代平行高速总线可简化系统设计。在速度高时,并行总线容易遭受干扰和串扰,使得布线相当复杂,有时甚至无法实现。而极具强韧性的串行收发器能简化布局设计,减少零组件和连接器数量,还能减少PCB层数。在具有相同的总线频宽时,串行接口的功耗也比并行端口小。

但收发器的更高数据率意味着非理想的传输线效应会使布线更加困难。人们普遍采用FR4板进行PCB设计,因为FR4的制造通常采用玻璃纤维和环氧材料,因此具有容易制造、阻燃、易钻孔、低成本等特点。遗憾的是,当数据率较高时,各层中的铜线会产生‘趋肤效应’,高频讯号掠过导体的表面,减少了传导区域,增加了讯号衰减。FPGA设计师通常对数Gb讯息信道中传送的讯号频率点了解较少,由于FR4介电材料本身对衰减的影响就极大,在只有几Gb的数据率上,衰减有可能超过20dB。为了克服这些问题,具有收发器的Stratix II GX FPGA包含了发射机和接收机内部的一些功能,可继续使用便宜的FR4 PCB材料。

预加重

在数Gb速率时,设计师无法简单地透过放大讯号解决讯号损失问题,因为这将增大功耗并引起眼图的闭合。眼图闭合可能是由发射缓冲的阻抗变坏所引起。在布局上或连接器中,反射能量的强度呈现出近端的不连续性。预加重透过加重任何讯号变化后的第一个数据符号来对发射讯号进行预失真处理,消除讯息信道中脉冲响应的前端过冲和后沿拖尾。

Stratix II GX收发器提供可程序的预加重功能,允许用户根据传输媒介和驱动能力,在3个抽头中选取每个抽头13级中的任意一级。最大的预加重为500%,这对张开1.25m Molex GbX背板上速率为6.25Gbps的眼图来说已经足够。

接收机均衡

预加重是克服传输线损耗的有效方法,不过较高的驱动强度将产生电磁干扰(EMI),并且会使系统容易遭受近场的串扰。张开接收机眼图的一种替代方案或互补方案是利用接收机均衡技术。在许多应用中利用均衡技术来克服损耗并实现误码性能改善是可能的。FPGA中的接收均衡透过在接收机端放大讯号中的高频分量来补偿传输损耗,而低频分量保持不变,这将有效地使讯息信道的s-21插入损耗曲线反转,使得总讯息信道的频率响应变得最平坦。均衡技术还可以与预加重技术一起使用,来补偿具有特殊挑战性的链路。

Stratix GX II收发器是完全可编程的,无论在设计或应用阶段,都能在系统工作过程中进行编程,并能与远距设备及在工作条件很差的环境下实现互通作业性。这使用户得以配置均衡器,使其在各种讯息信道长度上工作。最大的均衡水平是17dB,采用4级峰值放大器来实现。这确保了所配置的系统能实现组件速率高达6.375Gbps条件下的最佳讯号完整性,而且还省去了极易传递误码、功耗大并基于DFE的外来接收机架构。

在设计背板时需考虑的重要因素是收发器的输出驱动能力,因为最佳讯号完整性设置会由于背板布局、背板插槽数量以及发射卡和接收卡的整体位置不同而变化。由于这种收发器优越的讯号完整性性能,使FPGA能以6.375Gbps的速率在具有连接器的52英寸FR4背板上工作。这种可编程能力和极具强韧性的设计加上低功耗特性,使FPGA可工作在最具挑战性的背板、电缆、芯片或模块以及数Gb互连设备中。

可编程驱动能力

某些传输线损耗可透过增强差分输出驱动器的驱动能力,以及在接收机里放大讯号电平来克服。Stratix II GX架构允许设计师在4mA~16mA范围内选择驱动能力。实际的Vod输出驱动电压电平取决于终端电阻值,对50Ω的传输线来说,标准阻值范围是100Ω。

功率

在所有的高密度背板应用中,功率耗散都是一个主要问题。这些应用的空间有限,功耗和发热问题必须减到最小,以确保组件温度在没有风力冷却和电源供给情况下仍能保持在所要求的工作范围内。

为了降低收发器功耗,Stratix II GX采用了专利的PCNL输出缓冲器技术,该技术使90奈米的PMA(实体媒体连接)层的最大功耗较具备收发器的65奈米FPGA低20%。在40寸FR4串行链路上,工作速率达3.1875Gbps时,每四分之一收发器(四个收发器中的一个)所需的功耗为每通道125mW,而工作速率达6.375Gbps时的功耗则为每通道225mW。每四分之一收发器可由1~2个独立的频率源来驱动,并具有各自独立的频率分配器。频率和分频器的结合,能在每四分之一收发器中支持四个不同的数据率,这将大幅降低功耗。利用信道的基本配置能分别判断信道上的发射机或接收机,进一步节省Stratix II GX收发器的功率。

协议支持

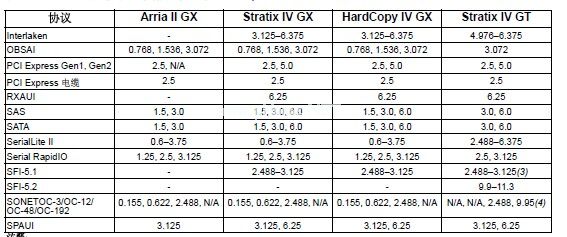

先进的FPGA设计方法能大幅甚至彻底省去设计和验证FPGA与收发组件间数据信道所需的工作和时间。为了使收发器在满足特定协议标准时还能具有一定的余量,并能在614Mbps到6.375Gbps的数据速率范围内正常工作,Stratix II GX收发器经过了精心设计,可提供经验证的良好性能。支持的协议标准包括PCI Express、串行数字接口(SDI)、XAUI、Gigabit以太网络、HiGig+、Interlaken、SerialLite II、Serial RapidIO(SRIO)、光纤信道,以及常用的6Gbps长距和短距电界面(CEI-6G-LR/SR)。FPGA基本协议模式能让架构师在全速率范围内建构任何符合当地需求或具有知识产权的协议。Stratix II GX系列能满足严格的SONET/SDH OC48/STM16光抖动标准,能整合FPGA的数字和协议功能,以及具备线路接口功能、背板功能、低功耗、低抖动、协议兼容的收发器。

来源同步和平行I/O支持

多数应用要求高速来源同步和并行接口提供数据平衡和管线作业。来源同步I/O(SSIO)是一种允许频率和数据被分别(即使用LVDS讯号)发送的FPGA界面。作为一种链路层接口,SSIO用于将数据从收发器传送到系统进行处理。来源同步I/O必须支持一个足够高的数据频宽,以确保能向收发器连续不断地提供数据。来源同步I/O部份包含动态相位对齐(DPA)电路,该电路将接收机频率讯号复制到变化的相位讯号中,并将最近的频率讯号与进来的数据对齐。DPA能够使来源同步接口支持更高的数据率,支持增强型数据信道开销,进一步提高数据率,并实现纠错、加密和线路编码。

SSTL和HSTL中具有大量可提供标准I/O连接的平行I/O,适合高性能内存接口、PCI接口等应用。具有收发器的FPGA面临的挑战是如何在具有平行I/O、SSIO和FPGA数字逻辑、且收发器所有埠在工作和被评估时可同时切换的验证标准一致性,以及抗噪音能力和强韧的抖动性能。

FPGA高速收发器设计原则

- FPGA(591969)

相关推荐

赛灵思演示28nm工艺FPGA:80个最大13.1Gbit/秒高速串行收发器

美国赛灵思(Xilinx)2012年4月5日使用28nm工艺制造的FPGA “Virtex-7 X690T”演示了有线通信系统(背板)。该FPGA配备有80个以最大13.1Gbit/秒的速度工作的高速串行收发器“GTH”,已于2012年

2012-04-09 11:13:59 2848

2848

2848

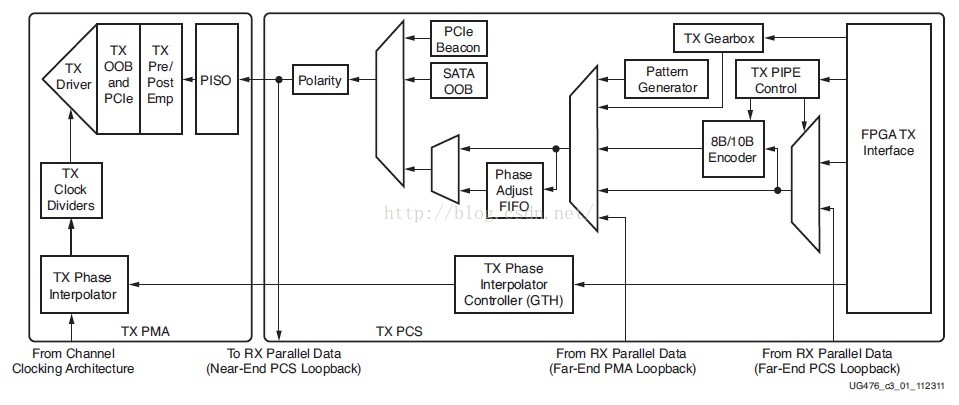

2848FPGA高速收发器的GTX发送端解析

每一个收发器拥有一个独立的发送端,发送端有PMA(Physical Media Attachment,物理媒介适配层)和PCS(PhysicalCoding Sublayer,物理编码子层)组成

2020-11-20 11:27:39 5566

5566

5566

5566

FPGA设计之GTP、GTX、GTH以及GTZ四种串行高速收发器

xilinx的7系列FPGA根据不同的器件类型,集成了GTP、GTX、GTH以及GTZ四种串行高速收发器,四种收发器主要区别是支持的线速率不同,图一可以说明在7系列里面器件类型和支持的收发器类型以及

2020-11-20 12:08:15 17712

17712

17712

17712

7系列收发器与时钟的关系是什么?

嗨,我想了解7系列收发器的Kintex xc7k325tffg900-2 FPGA。https://www.xilinx.com/support/documentation/user_guides

2020-05-11 08:09:08

FPGA GTP收发器设计指导

本帖最后由 QQ3511836582 于 2017-3-29 15:42 编辑

疑问描述测试表明,Spartan-6 FPGA的GTP收发器有可能受到临近bank中用户管脚的干扰。因此,赛灵思

2017-03-21 14:34:27

FPGA GTP收发器设计指导

FPGA GTP收发器设计指导疑问描述测试表明,Spartan-6 FPGA的GTP收发器有可能受到临近bank中用户管脚的干扰。因此,赛灵思针对bank0和bank2中管脚的使用提出了一些新的建议

2016-08-25 09:46:38

FPGA高速收发器设计要遵循哪些原则?

高速收发器(SERDES)的运用范围十分广泛,包括通讯、计算机、工业和储存,以及必须在芯片与芯片/模块之间、或在背板/电缆上传输大量数据的系统。但普通高速收发器的并行总线设计已无法满足现在的要求。将收发器整合在FPGA中,成为解决这一问题的选择办法。FPGA高速收发器设计时,我们需要注意哪些事项呢?

2019-08-07 06:26:42

FPGA固件开发-设备收发器模块的数据访问状态实现

数据访问状态的功能简单地说就是中断监测和数据收发。每次系统复位后 FPGA 会自动配置 PDIUSBD12 器件,配置完成之后设备收发器模块会处于空闲状态(TS_IDLE)。PDIUSBD12 器件

2018-11-27 09:20:08

收发器

、体积小、无中继、传输距离长等优点得到了广泛的应用,光纤收发器正是利用了光纤这一高速传播介质很好的解决了以太网在传输方面的问题。那么,我们对这个名词也来做个解释吧。光纤收发器,是一种将短距离的双绞线

2014-04-30 17:28:08

收发器的每项参数与其在实际应用中的意义

CAN收发器是连接CAN控制系统与CAN总线网络的桥梁,当选型CAN收发器时应该注意哪些参数?本文将带大家深入的了解收发器的每项参数与其在实际应用中的意义。

2020-12-18 07:16:27

高速CAN收发器MCP2551电子资料

概述:MCP2551是MACROSHIP生产的一款高速CAN收发器。可作为CAN协议控制器和物理总线接口。MCP2551可为CAN协议控制器提供差分收发能力,它完全符合ISO-11898标准,包括能满足24V电压要求...

2021-04-20 06:50:57

CAN收发器有什么特点?

在CAN通信中,收发器起到了十分相当特别的作用。目前市面的收发器型号也是不计其数,本文则是根据收发器的发展,简单介绍几款收发器的特点。很多年前,NXP的CAN收发器几乎在每一个CAN节点上都看的到,当时最常见的型号就是PCA82C250。

2019-09-03 06:04:44

Cyclone IV 收发器体系结构

在低成本的 FPGA 中,Cyclone® IV GX 器件内嵌多达八个全双工收发器,运行在 600Mbps 到 3.125 Gbps 的串行数据速率上。 表 1-1 列出了 Cyclone IV GX 收发器通道所支持的串行协议信息。

2017-11-14 10:54:41

DA PHS射频收发器芯片怎么设计?

微电子(RDA)公司开发出基于全新RF收发结构的单芯片收发器及集成天线开关的高效率功放模块。本文介绍RDA PHS射频收发器芯片的设计方法。

2019-09-20 07:46:19

GTX收发器,读取速度低于500Mbps怎么办?

嗨,我们计划在不同线路速率的高速收发器线路上接收数据,最低为400Mbps。接收器规范提供的最小线速率为500 Mbps。有没有办法使用400Mbps流使用收发器(例如通过过采样,减少时钟分频器)?目前我们在收发器外使用过采样,但这阻止我们使用内部8b10b解码器和逗号对齐逻辑。谢谢,马蒂亚斯

2020-08-12 06:39:36

RS-485自动收发型收发器工作原理揭秘

RS-485总线是半双工的通信总线,因此通常需要MCU控制RS-485收发器的收发状态。为节省MCU的I/O资源,RS-485自动收发型收发器应运而生,但该类收发器或多或少会遇到一些应用问题,这一类问题该如何解决?本文将从工作原理为你揭晓。

2019-07-12 07:37:06

SFP收发器向导怎么设置?

我需要能够使用SFP收发器。我想使用收发器向导,但我不知道选择哪些选项。我不确定我的转账率是多少。我知道我需要使用的时钟大约是600MHz。我还需要能够从此收发器恢复时钟。收发器是否有输出时钟?谢谢你的帮助。

2020-04-07 14:39:32

WiFi收发器的电源和接地设计

。考虑到实际设计中PLL杂散信号对于电源耦合、接地和滤波器元件的位置非常敏感,本文着重讨论了有关PLL杂散信号抑制的方法。为便于说明问题,本文以MAX2827 802.11a/g收发器的PCB布局作为参考设计。WiFi收发器的电源和接地设计:[hide] [/hide]

2011-12-06 16:28:08

XILINX收发器问题的解决

我正在研究使用高速收发器接收部分的定制电路板。所有四个接收器的参考时钟相同,为125 MHz。我从焦平面阵列(FPA)接收数据并使用8 / 10b编码。我可以让FPA重复显示空白行(字符1FFD

2020-05-05 11:39:41

什么是用于RF收发器的简单基带处理器?

挑战。这些收发器可为模拟RF信号链提供数字接口,允许轻松集成到ASIC或FPGA,进行基带处理。基带处理器(BBP)允许在终端应用和收发器设备之间的数字域中处理用户数据。

2019-09-19 06:20:59

介绍Xilinx 7系列FPGA收发器硬件设计主要注意的一些问题

引言:本文我们介绍Xilinx 7系列FPGA收发器硬件设计主要注意的一些问题,指导硬件设计人员进行原理图及PCB设计。本文介绍以下内容:GTX/GTH收发器管脚概述GTX/GTH收发器时钟

2021-11-11 07:42:37

使用一个收发器的Txoutclk为两个收发器配备Txusrclock吗?

嗨,我有2个静态配置的GTX收发器用于HD-SDI操作。我可以使用一个收发器的Txoutclk为两个收发器配备Txusrclock吗?通过这种方式,我可以只用1个Txusrclock为FPGA逻辑

2020-08-19 07:43:50

关于FPGA如何连接CAN收发器?

我之前在CSDN上查到的资料都显示FPGA需要连接一个独立CAN控制器,如SJA1000再去连CAN收发器。请问我能直接把FPGA的引脚直接连在CAN收发器的TX、RX上吗?如果不能原因又是什么?

2018-10-10 09:25:39

具有高速CAN收发器的MC33907电源系统基础芯片的应用

具有高速CAN收发器的MC33907电源系统基础芯片的典型应用。 33907_8器件是多输出,电源,集成电路,包括HSCAN收发器,专用于汽车市场

2020-05-22 15:58:32

利用IBERT核对GTX收发器板级测试

和GTX收发器的动态重新配置端口属性,还包括通信逻辑,以允许设计在运行时通过JTAG进行访问。

IBERT工具用于对Xilinx FPGA芯片的高速串行收发器进行板级硬件测试。通过IBERT可以获取误码率

2023-06-21 11:23:12

如何在FPGA和ASIC设计中结合高速USB功能

ASIC系统。 使用USB协议栈知识产权(IP)及外部收发器 在第一种方法中,我们可以在FPGA或ASIC中实现SIE(见图3)。图3 FPGA + USB协议栈IP + USB收发器 SIE IP

2012-11-22 16:11:20

如何选择合适的FPGA千兆位收发器?

选择合适的千兆位收发器(GT)是通信和实时处理领域尤其需要重点考虑的设计事项,但特定的市场领域可能会存在太多的标准、协议或使用模型。有时针对某一种应用就会涉及到好几种标准,为了选择最适合的千兆位收发器,必须对各种协议的最新发展情况了如指掌。

2019-10-31 06:57:54

展望未来英特尔FPGA设计,介绍新型224G PAM4收发器

`FPGA 的全称是“现场可编程门阵列”,而能够以较低的功耗、将信号高速引入或推出的收发器,将是该领域在未来很长一段时间内的一个主战场。据悉,FPGA 有望迎来一个可充编辑逻辑的终极功能世界,通过

2020-09-02 18:55:07

常见CAN收发器分为哪几种

是S32K116的FlexCAN外设,收发器是TJA1043T,两端的电阻由主机厂提供,我们的OBU中不加电阻。常见CAN收发器分为三种:高速CAN,最高速率1M/bps低速/容错CAN,最高速率125K/bps单线CAN,最高速率33.3K/bps接法和物理信号如下图所示:Quipass

2022-01-10 07:54:45

求助FPGA高速串行收发器,输出12.5Gbps的信号要用什么电平 ...

求助FPGA高速串行收发器,输出12.5Gbps的信号要用什么电平输出28.5Gbps的信号要用什么电平?

2014-11-10 09:12:51

请问7系列FPGA收发器向导v2.3 GTX名称不正确的原因?

你好我试图在KC705板上使用收发器来生成比特流。我正在使用Vivado 2012.3和7系列FPGA收发器向导v2.3。我之前使用过具有不同传输者名称的IBERT核心。IBERT收发器名称类似于

2020-07-28 10:29:31

请问能用FPGA直接连接CAN收发器吗?

我之前在CSDN上查到的资料都显示FPGA需要连接一个独立CAN控制器,如SJA1000再去连CAN收发器。请问我能直接把FPGA的引脚直接连在CAN收发器的TX、RX上吗?如果不能原因又是什么?

2018-10-10 09:05:37

采用AD9361高性能高度集成的RF收发器

AD-FMCOMMS2-EBZ,评估板是一款高速模拟模块,旨在展示AD9361,这是一款高性能,高度集成的RF收发器,适用于RF应用,如3G和4G基站和测试设备应用,以及软件定义的无线电。其可编程性

2019-07-04 14:15:44

TJA1042高速CAN 收发器

关键词 TJA1042、高速、低功耗、CAN 收发器摘 要TJA1042 是一款高速CAN 收发器,是CAN 控制器和物理总线之间的接口,为CAN 控制器提供差动发送和接收功能

2009-11-10 13:50:18 364

364

364

364基于MICRF005的高速无线UHF收发器原理及应用

MICRF005芯片是Micrel公司生产的一种高速无线UHF收发器?熏是一款单芯片OOK收发器,可用于远距离低功率无线设备中单向和双向无线连接。MICRF0

2010-11-30 17:15:51 26

26

26

26基于FPGA的高速时钟数据恢复电路的实现

基于FPGA的高速时钟数据恢复电路的实现

时钟数据恢复电路是高速收发器的核心模块,而高速收发器是通信系统中的关键部分。随着光纤在通信中的应用,信道可以承载

2009-10-25 10:29:45 3626

3626

3626

3626

选择合适的FPGA千兆位收发器至关重要

选择合适的FPGA千兆位收发器至关重要

选择合适的千兆位收发器(GT)是通信和实时处理领域尤其需要重点考虑的设计事项,但特定的市场领域可能会存在太多的标准、

2009-11-04 10:05:02 467

467

467

467

采用带有收发器的全系列40-nm FPGA和ASIC实现创新

采用带有收发器的全系列40-nm FPGA和ASIC实现创新设计

人们对宽带服务的带宽要求越来越高,促使芯片供应商使用更多的高速串行收发器。因此,下一代应用采

2010-02-04 11:06:19 879

879

879

879

TJA1043新一代高速CAN总线收发器

TJA1043新一代高速CAN总线收发器

恩智浦半导体推出了新一代的高速CAN总线收发器-TJA1043,它在电磁兼容(EMC)和静电放电(ESD)性能上有显著提高。

2010-05-10 11:01:21 7709

7709

7709

7709PDN设计和FPGA收发器性能

面向收发器(SERDES) FPGA 的PDN 设计对电源有严格的要求,需要干净的电压源。虽然低功耗应用中通常采用低泄漏(LDO) 线性稳压器,但这一方法必须仔细的隔离电压源。电路板设计人员在这

2011-05-11 18:29:41 57

57

57

57Xilinx推出UltraScale FPGA收发器设计

了解如何在您的 UltraScale™ FPGA 设计中部署串行收发器。了解并利用串行收发器模块的特性,如 8B/10B 和 64B/66B 编码、通道绑定、时钟校正和逗点检测。其它专题

2017-02-09 08:04:41 327

327

327

327FPGA中RocketIO GTP收发器的高速串行传输实现方案

提出了基于Xilinx公司Virtex-5系列FPGA中RocketIO GTP收发器设计的一个高速串行传输实现方案,详细阐述了硬件设计要点和软件实现概要,系统实测表明,该方案能在某信号处理系统两个板卡之间稳定地进行1.6 Gb/s的数据传输,误码率优于10e-12,传输距离大于1米。

2017-11-21 10:16:00 7689

7689

7689

7689比较 Xilinx® Virtex®-7FPGA GTH收发器和Altera Stratix V GX收发器的均衡能力

设计人员呼吁提升10G+ 芯片到芯片和背板性能, 依赖接收机均衡来补偿信号失真。观看视频, 并排比较 Xilinx® Virtex®-7 FPGA GTH 收发器 和 Altera Stratix V GX 收发器的均衡能力。

2018-05-23 15:47:00 3974

3974

3974

3974

基于MCP2561/2下的高速 CAN 收发器

MCP2561/2 是 Microchip 的第二代高速 CAN 收发器。

它可用作 CAN 协议控制器与两线制 CAN 物理总线之间

的接口。

2018-06-28 09:23:00 23

23

23

2340-nm收发器FPGA和ASIC系列的特点

您意识到对高速收发器、更高的数据速率和带宽的需求越来越强烈了吗? 您是否希望“以少胜多”呢? 请观看这一新视频,了解全系列收发器FPGA和ASIC怎样满足这些需求,为业界提供最全面的收发器定制逻辑

2018-06-22 01:18:00 2817

2817

2817

2817高速ADC与高速串行收发器

经理。我从事FPGA工作已经有12年了。他们中后5人的主要工作是高速串行收发器应用。

我们今天在这里演示新的Linear Technology LTC2274模数转换器怎样与具有嵌入式串行收发器

2018-06-20 05:28:00 4215

4215

4215

4215

Virtex UltraScale+ FPGA收发器的演示

该视频演示了具有32.75G背板功能的Virtex®UltraScale+™FPGA,功率优化的收发器。

该收发器具有同类最佳的发送抖动和第三代客户验证的自适应接收器均衡功能......

2018-11-28 06:39:00 2161

2161

2161

2161如何在spartan-6 FPGA中使用GTP收发器的详细资料说明

本文档介绍如何在Spartan®6 FPGA中使用GTP收发器。•spartan-6 FPGA GTP收发器简称为GTP收发器。

•gtpa1_dual是实例化原语的名称,它实例化一组

2019-02-15 14:42:47 27

27

27

27virtex-6 FPGA GTH收发器的用户指南资料免费下载

本章介绍virtex-6 FPGA GTH收发器向导,并提供相关信息,包括其他资源、技术支持和向xilinx提交反馈。向导自动执行创建HDL包装器的任务,以配置virtex-6设备中的高速串行GTH收发器。

2019-02-20 09:35:45 4

4

4

4如何使用电源管理系统使FPGA收发器的容差保持很小

ADI Guneet Chadha演示如何使用电源系统管理使FPGA内核或I/O(例如:高速收发器)的电源输出电压(1V)保持在很小的容差范围内(0.25%)还显示了“如何确定电源裕量”

2019-07-24 06:15:00 2098

2098

2098

2098基于XilinxVirtex®-6FPGA 11.18 Gbps收发器的高速互操作性

和AFCT-701SDZ 10 Gbs以太网SFP +收发器产品与具有自适应DFE的XilinxVirtex®-6FPGA 11.18 Gbps收发器的高速互操作性。 Xilinx产品:Virtex-6 HXT

2021-04-14 11:53:31 4122

4122

4122

4122

工业级光纤收发器的选购原则及使用注意事项

此外还有单纤工业级光纤收发器和双纤工业级光纤收发器,内置电源工业级光纤收发器和外置电源工业级光纤收发器以及网管型工业级光纤收发器和非网管型工业级光纤收发器。

2020-11-17 14:21:23 4508

4508

4508

4508Xilinx 7系列FPGA收发器架构之硬件设计指导(一)

引言:本文我们介绍Xilinx 7系列FPGA收发器硬件设计主要注意的一些问题,指导硬件设计人员进行原理图及PCB设计。本文介绍以下内容:GTX/GTH收发器管脚概述 GTX/GTH收发器时钟

2021-11-06 19:51:00 35

35

35

35如何区分单纤收发器与双纤收发器

单纤收发器是指采用的是单模光缆,单纤收发器是只用一根芯,两端都接这根芯,两端的收发器采用不同的光波长,所以能在一根芯里传输光信号。

2023-03-16 14:24:33 1050

1050

1050

1050

如何计算高速RS485收发器的功耗?

如何计算高速RS485收发器的功耗? 高速RS485收发器是一种常见的通信设备,用于对串口数据进行收发。对于高速RS485收发器,我们需要了解它的功耗计算方法,以便在使用过程中合理计划电源供应

2023-10-31 14:37:15 554

554

554

554 电子发烧友App

电子发烧友App

评论