ISE12.2设计套件强化了其部分可重配置技术设计流程,并通过智能时钟门控技术降低24% 的 BRAM 功耗。赛灵思部分可重配置技术,是目前唯一经行业验证的可重配置FPGA

2010-07-31 12:39:03 439

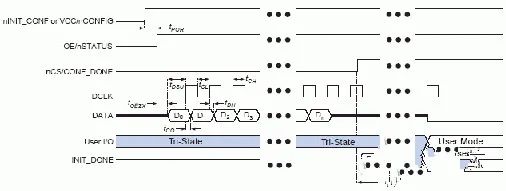

439 通过FPGA的多重配置可以有效地精简控制结构的设计,同时可以用逻辑资源较少的FPGA器件实现需要很大资源才能实现的程序。以Virtex5系列开发板和配置存储器SPI FLASH为基础,从硬件电路

2014-01-24 14:17:22 13670

13670

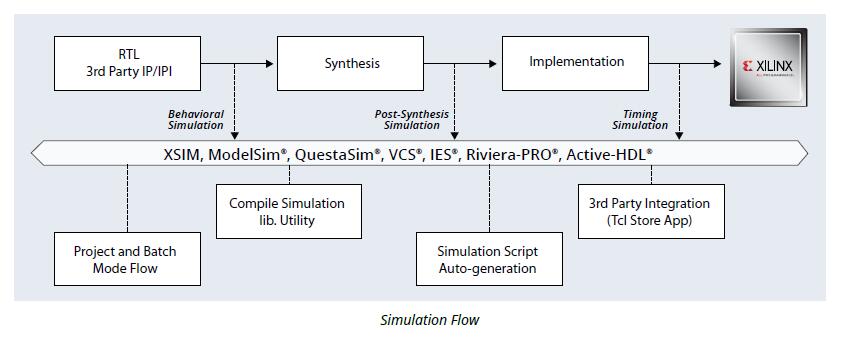

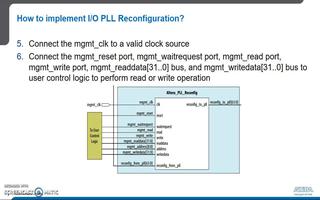

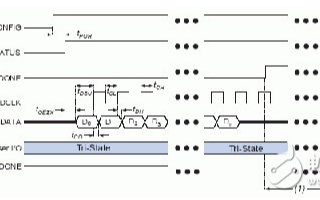

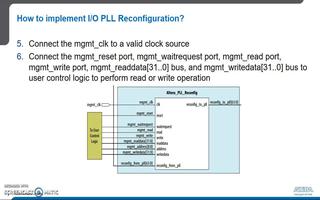

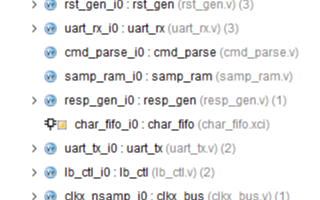

上文XILINX FPGA IP之Clocking Wizard详解说到时钟IP的支持动态重配的,本节介绍通过DRP进行MMCM PLL的重新配置。

2023-06-12 18:24:03 5528

5528

AS安全模式建立完毕后,UE和gNB之间会触发RRC重配置流程。

重配置信令流程如图所示:

那么触发重配置流程的目的以及重配置消息中有哪些关键字段呢?

1 RRC重配置流程的目的

2023-05-10 15:44:58

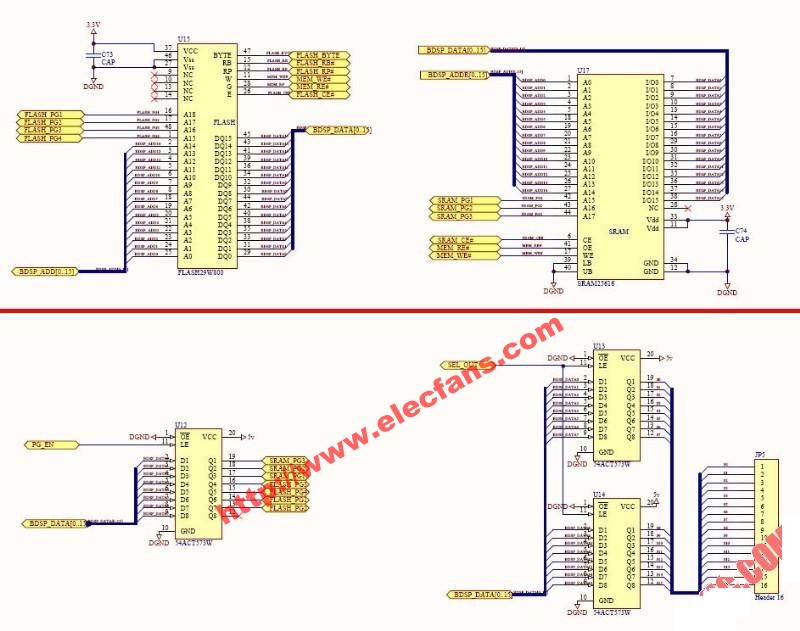

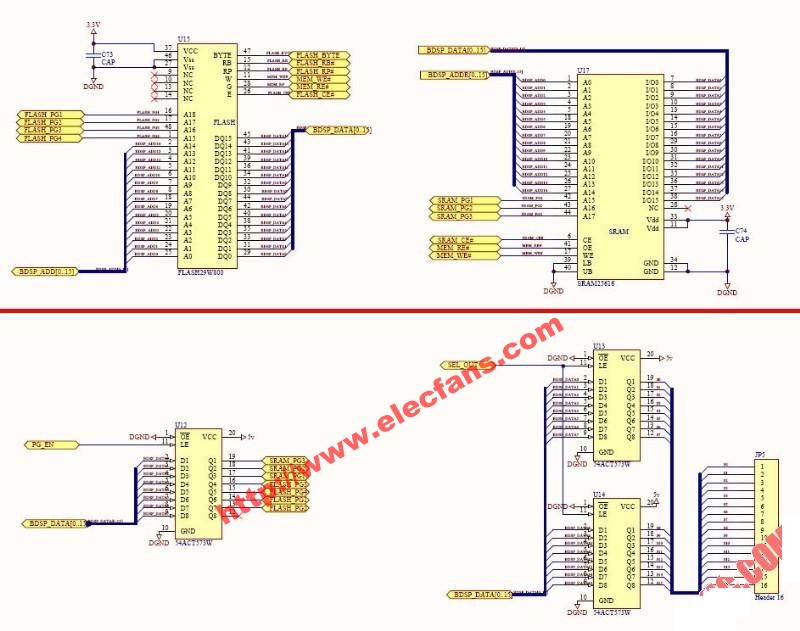

HII我正在使用FM4-S6E2CC-ETH套件,我正在尝试了解SRAM与控制器的引脚连接,但是它看起来是不同的和混淆的,所以请帮助我或者让我知道PIN配置是如何完成的。这里是什么UB和LB引脚21

2018-11-28 16:34:38

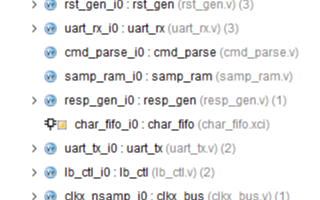

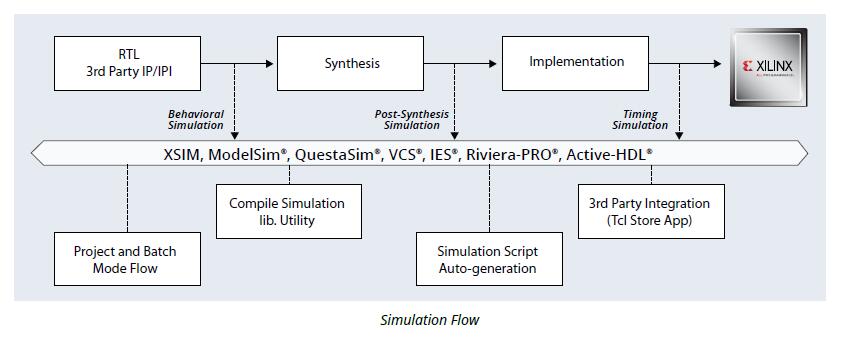

在FPGA的应用中,很多时候就是CPU+FPGA+一些常见外设(FLASH、SRAM等),FPGA的功能差别其实不大,那么它的测试文件差别应该也不是这么大,为了简化仿真,是不是可以写些文件,通过修改

2013-08-29 20:40:25

在FPGA的应用中,很多时候就是CPU+FPGA+一些常见外设(FLASH、SRAM等),FPGA的功能差别其实不大,那么它的测试文件差别应该也不是这么大,为了简化仿真,是不是可以写些文件,通过修改

2013-08-29 20:42:31

在FPGA的应用中,很多时候就是CPU+FPGA+一些常见外设(FLASH、SRAM等),FPGA的功能差别其实不大,那么它的测试文件差别应该也不是这么大,为了简化仿真,是不是可以写些文件,通过修改

2013-08-29 20:46:18

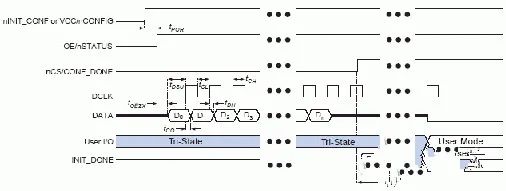

Altera可重配置PLL使用手册在实际应用中,FPGA的工作时钟频率可能在几个时间段内变动,对于与之相关的锁相环(PLL),若PLL的输入时钟在初始设定的时钟频率的基础上变化不太大时,PLL一般

2009-12-22 11:27:13

Cyclone® IV GX 收发器支持对收发器的不同部分进行动态重配置,而无需对器件的任何部分断电。本章节提供并讲解了用于动态重配置各种模式的实例。您可以使用 ALTGX_RECONFIG

2017-11-14 10:53:11

可重构设计是指利用可重用的软、硬件资源,根据不同的应用需求,灵活地改变自身体系结构的设计方法。FPGA器件可多次重复配置逻辑的特性使可重构系统成为可能,使系统兼具灵活、便捷、硬件资源可复用等性能

2011-05-27 10:22:36

直接把所有电路做在一个工程中,这样使用的FPGA芯片容量太庞大,非常昂贵,而且电路胶合控制太复杂,这时候我们可以对每种FPGA模型进行分别生成配置文件,当根据实时状态现场更新FPGA电路。这样就可以采用

2012-04-26 14:27:03

PSoC 1具有独特的“动态重配置”能力。这意味着可以使用单个资源来执行多个功能。例如,我们可以考虑一种冷饮自动售货机。大部分时间,它必须作为一个自动售货机扔出罐头和收集钱。但是在晚上,一段时间

2019-05-24 14:51:27

大家好,PSoC 3/5支持类似于PSoC 1的硬件重配置吗?这可以在运行期间完成吗?谢谢,亚历克斯 以上来自于百度翻译 以下为原文Hello All, Do PSoC 3/5 support

2019-04-03 10:49:18

最近项目用到TMS570LS1227的EMIF功能,第一次接触求HAL中关于SRAM配置如何配置?附件中有SRAM资料(IDT70V25)。谢谢

2018-06-21 10:17:19

用于Virtex 6设计的可重配置LUT(CFGLUT)可能被封装到FPGA的输出逻辑OLOGICE1而不是SLICEM上的LUT。我的设计涉及使用存在于与CFGLUT相同的片中的FF(用于流水线

2018-10-22 11:04:46

Xilinx目前只提供工程芯片,因此这些器件的比特流生成无效。 - 器件支持仅限于这些器件:KU9P,KU15P,VU7P,VU9P, VU13P,ZU7EV,ZU9EG“是否有可能在评估板上使用部分重配置:VCU118使用此设备:XCVU9P在订购之前对我们很重要!谢谢你的细节JLD

2020-05-12 09:15:28

`Xilinx FPGA入门连载17:PWM蜂鸣器驱动之复位与FPGA重配置功能特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm1 复位

2015-10-26 12:05:15

Xilinx PlanAhead工具资料说可以用来部分动态重配置,我现在想对芯片的每一帧中每一位进行逐位翻转的动态重配置,使用PlanAhead能够实现么?应该怎么理解Planahead的部分重配置,如何应用?希望知道的朋友告诉下,对这个有点迷茫。

2015-06-01 10:11:33

数据手册里的这句话如何理解?256K FLASH+64K SRAM 的产品支持用户选择字配置为(192K FLASH+128K SRAM)、(224K FLASH+96K SRAM)、(256K

2022-06-20 07:37:12

打扰一下。在paritial重新配置用户指南中,它提到部分重新配置元素可以是lut或reg。我可以问一下xilinx系列中部分重配置的最小粒度是多少? (PR的最小粒度是否只能是一个BLE,CLB?或者它至少包含几个clb,或者至少应该是一个整列?)谢谢您的回复。

2020-06-17 11:34:34

参考了官网和各路大神写的一些关于PLL动态重配置的资料,虽然有收获但是还是感觉大神们写的太高端,不够详细,对于我这种学渣看起来还是迷迷糊糊。所以整理了一下自己的经验,把整个过程记录了下来。没有很多语言全部是截图大家凑合看吧。附有源代码和Word文档。

2017-10-12 12:32:44

CPLD的核心可编程结构介绍基于SRAM编程技术的PLD电路结构设计

2021-04-08 06:51:29

,以便为Microblaze实现不同的periferal。我已经读过Spartan3 FPGA支持部分重配置,但我不知道它是否支持动态重配置,而Microblaze仍在使用中。有帮助吗?提前致谢缺口

2019-05-14 06:28:56

本文介绍的基于FPGA的可重配置系统可以在设计后期甚至量产阶段通过重新编程以适应标准和协议的改变。

2021-05-13 06:35:49

随着集成电路的发展,越来越多的ASIC和SoC开始使用嵌入式SRAM来完成数据的片上存取功能。但嵌入式SRAM的高密集性物理结构使得它很容易在生产过程中产生物理故障而影响芯片的良率,所以,SRAM

2019-10-25 06:28:55

嗨, 我已经成功安装了Xilinx ISE 12.1-系统版。如何使用ISE 12.1安装部分重配置许可证或覆盖?现在我正在使用带有PlanAhead 10.1.1的PR overlay 16

2018-11-16 11:39:22

随着大规模集成电路的快速发展,系统设计已从传统的追求大规模、高密度逐渐转向提高资源利用率,使有限的资源可以实现更大规模的逻辑设计。利用现场可编程逻辑器件FPGA的多次可编程配置特点,通过重新下载存储

2019-08-07 06:17:30

我试图找出部分重配置的配置架构。从我之前使用Virtex-5 FPGA的工作开始,帧将跨越时钟区域的垂直切片。但是,我找不到任何类似的Virtex-7文档。我找到的只是configuraiton指南

2020-05-29 08:54:01

随着大规模集成电路的快速发展,系统设计已从传统的追求大规模、高密度逐渐转向提高资源利用率,使有限的资源可以实现更大规模的逻辑设计。利用现场可编程逻辑器件FPGA的多次可编程配置特点,通过重新下载存储

2019-08-06 07:05:37

存储配置数据。配置数据决定了PLD内部互连和功能,改变配置数据,也就改变了器件的逻辑功能。SRAM编程时间短,为系统动态改变PLD的逻辑功能创造了条件。但由于SRAM的数据易失的,配置数据必须保存在PLD器件以外的非易失存储器内,才能实现在线可重配置(ICR)。

2019-08-22 06:31:02

对于城域网络和长途网络来说,如果光传送层具有远程重新配置的能力,则可以极大地降低运营成本。运营商也已经意识到这种潜力,并在最近业务网络的招标中加入了对于可重配置光分插复用器(ROADM)以及多维光

2019-08-08 06:31:07

请问F28335最多可外扩多大的SRAM?支不支持iis42s16400j-7tliSRAM芯片?

2018-09-12 11:03:09

我程序需要设置SRAM大些,应该是在SCF散列文件改,我改大了size,结果程序就不跑了,我百度,有说NXP的片子SRAM地址不连续,我查看上图手册,没找到0x20000000的地址,请问我如何配置更大SRAM

2022-01-12 07:45:11

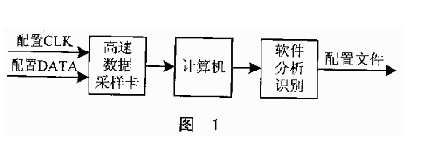

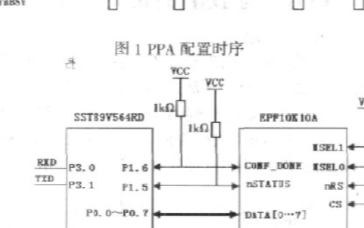

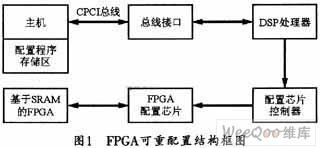

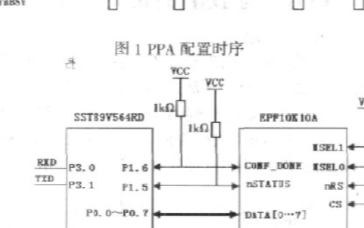

介绍基于SRAM 的可重配置PLD 的原理;通过对多种串行配置的比较,提出单片机与存储器串行配置方式; 从系统复杂度、可靠性和经济性等方面进行比较和分析。

2009-05-14 14:36:33 17

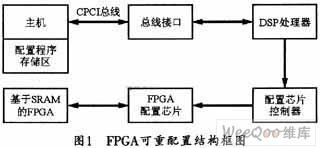

17 本文提出了一种全新的总线可重配置的多处理器架构。该架构结合了多核与可重配置处理器的优势,具有并行性高、计算能力强、结构复杂度低并且应用领域广泛灵活的特点。对

2009-06-13 14:11:04 11

11 本文介绍了基于SRAM 查找表的现场可重配置FPGA 的结构和原理,及其配置方法,通过对多种配置方法的比较,提出了由单片机和EPROM 存储器组成的串行配置方式。这种方式结构简单

2009-08-13 08:25:10 20

20 该文基于现有端到端可重配置系统架构,提出了一种改进的动态门限联合负载控制方法,以适应不同负载条件下对负载均衡的要求,达到资源的有效利用。同时,结合终端的可重配

2009-11-19 16:41:25 13

13 介绍了基于ARM和FPGA的端到端重配置终端的硬件平台设计方法。给出了系统设计的硬件结构和重要接口, 提出了由ARM微处理器通过JTAG在系统配置FPGA的方法, 以满足重配置系统中软件

2010-09-14 16:40:09 21

21 本文档主要是以Altera公司的Stratix II系列的FPGA器件为例,介绍了其内嵌的增强型可重配置PLL在不同的输入时钟频率之间的动态适应,其目的是通过提供PLL的重配置功能,使得不需要对

2010-11-02 15:17:24 27

27 实现了一种用于上位机和FPGA处理板之间通信的可重配置接口,详细介绍了该接口的包格式设计和FPGA逻辑设计。仿真结果表明,该可重配置接口能根据信令,实现准实时在线参数配置

2010-11-22 15:15:28 12

12 FPGA的全局动态可重配置技术主要是指对运行中的FPGA器件的全部逻辑资源实现在系统的功能变换,从而实现硬件的时分复用。提出了一种基于System ACE的全局动态可重配置设计方法,

2011-01-04 17:06:01 54

54 sram电路图

2008-10-14 09:55:33 3432

3432

基于单片机的复杂可编程逻辑器件快速配置方法

基于SRAM(静态随机存储器)的可重配置PLD(可编程逻辑器件)的出现,为系统设计者动态改变运行电路

2009-03-28 16:47:17 749

749

摘要:介绍基于SRAM的可重配置CPLD的原理,通过对多种串行配置的比较,提出了由单片机和FLASH存储器组成的串行配置方式,并从系统复杂度、可靠性和经济性等方面进行了比

2009-06-20 11:03:48 418

418 软件无线电技术与可重配置计算体系结构

1.技术趋势 现代无线通信的主体是移动通信。参照ITU建议M1225,移动通信是在复杂多变的移动环境下工作的,因此必须

2010-03-01 10:58:37 739

739 IMEC、瑞萨、M4S推出可重配置多标准无线收发器

IMEC、株式会社瑞萨科技(以下简称瑞萨)、M4S联手推出了利用40nm低功耗CMOS工艺制造而成、带有RF、基带和数据转换器电

2010-03-01 11:14:01 860

860 SRAM,SRAM原理是什么?

静态随机存取存储器SRAM。

SRAM主要用于二级高速缓存(Level2 C ache)。它利用晶体管来存储数据。与DRAM相比,SRAM的速度快

2010-03-24 16:11:32 8479

8479 SRAM模块,SRAM模块结构原理是什么?

RAM 结构框图如图1 所示。它主要由存储矩阵(又称存储体)、地址译码器和读/写电路 3 部分组成。存储矩阵是存储

2010-03-24 16:28:39 3895

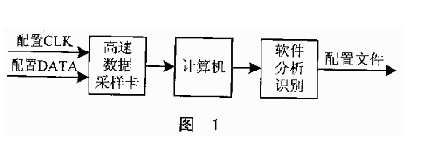

3895 采用VC++程序的FPGA重配置设计方案利用现场可编程逻辑器件FPGA的多次可编程配置特点,通过重新下载存储于存储器的不同系统数据

2010-04-14 15:14:57 580

580

同步突发式SRAM的内部框图如图所示,它与同步管道突发式SRAM基本相同,不同之处只是在输出缓冲器中没有配置锁存器。

2011-05-30 11:01:39 1457

1457

为了满足对分数阶 信号变换 进行实时计算的要求,提出一种基于Altera St ratix II FPGA 平台的可重配置分数阶信号变换处理器的硬件实现方案. 根据角度分解的算法,设计了一种通用的硬件框

2011-07-04 15:13:03 33

33 基于 FPGA 的 RCS 有几项值得注意的设计事项与优势。其核心部分是我们连接在一起以构成单个计算系统的数个FPGA。在我们的可重配置系统中,我们使用了正交通信系统,将 FPGA 布置在矩

2011-09-20 08:57:32 27

27 WP374 Xilinx FPGA的部分重配置

2012-03-07 14:34:39 34

34 本文介绍了XiLinx FPGA中DCM的结构和相关特性,提出了一种基于XiLinx FPGA的DCM动态重配置的原理方法,并给出了一个具体的实现系统。系统仅通过外部和......

2012-05-25 13:42:50 39

39 打造完全可重配置运动控制系统 ,NI LabVIEW。

2016-03-21 16:19:31 0

0 11月15日,All Programmable技术和器件的全球领先企业赛灵思公司)宣布,在2016全球超算大会上宣布推出一套全新的技术——赛灵思可重配置加速堆栈方案,旨在帮助全球最大的云端服务供应商

2016-11-16 16:42:23 648

648 一种基于忆阻器的可重配置逻辑电路_张波

2017-01-08 10:18:57 4

4 这里提到的局部重配置技术(Partial Reconfiguration) 是现场可编程门阵列(呵呵,就是FPGA了) 器件中的一部分。指的是在FPGA其他部分还在正常运行的情况下对其局部进行的重新配置。

2017-02-11 16:32:11 2622

2622 Suite HLx 2017.1版中广泛纳入部分重配置技术,为有线和无线网络、测试测量、航空航天与军用、汽车以及数据中心等丰富应用,提供动态的现场升级优势和更高的系统集成度。

2017-04-27 18:38:08 2782

2782

工作效率。通过FPGA 的多重配置可以有效地精简控制结构的设计,同时可以用逻辑资源较少的FPGA 器件实现需要很大资源才能实现的程序。以Virtex5系列开发板和配置存储器SPIFLASH为基础,从硬件电路和软件设计两个方面对多重配置进行分析,给出了多

2017-10-12 17:57:08 15

15 FPGA 动态局部重配置技术是近几年才发展起来的一项新技术。这项技术可以使 FPGA运行时,通过 JTAG或 SelectMAP(ICAP)动态重配置部分区域,而不影响非重配置区域的正常工作

2017-10-18 16:38:59 4

4 SRAM不需要刷新电路即能保存它内部存储的数据。而DRAM(Dynamic Random Access Memory)每隔一段时间,要刷新充电一次,否则内部的数据即会消失,因此SRAM具有较高的性能,功耗较小。

2017-11-03 16:11:12 11256

11256 视频、影像和电信市场的标准推动了异构可重配置DSP硬件平台的使用。在本文中这些平台包括DSP处理器和FPGA,它们提供的现成硬件解决方案可以解决视频、影像和电信设计中的重大难题,同时又不失差异化

2017-11-06 13:59:42 2

2 :不存在时延,这种方法基本不占用资源(在FPGA上占用的查找表不足300个),而且设计人员可以优化部分重配置的时序。

2017-11-22 17:08:56 1492

1492 的应用。在主流的FPGA中,绝大多数都采用了SRAM来存放配置数据,称为SRAM FPGA。这种FPGA的突出优点是可以进行多次配置。通过给FPGA加载不同的配置数据,即可令其实现不同的逻辑功能.FPGA这种可重配置的能力将给数字系统的设计带来很大的方便。

2018-07-18 12:50:00 2407

2407

针对虚拟网络映射中能耗过高、接收率偏低和负载不够均衡等问题,提出一种基于虚拟资源整合的综合性重配置算法-HEAR算法。该重配置算法分为两个阶段:节点重配置阶段优先将映射虚拟节点最少的物理节点上的虚拟

2017-12-20 11:31:58 0

0 如何在 Arria 10 中实现 I/O 锁相环 (PLL) 重配置

2018-06-20 00:57:00 3438

3438

赛灵思公司(Xilinx)宣布,在2016全球超算大会(SC 16)上宣布推出一套全新的技术——赛灵思可重配置加速堆栈方案,旨在帮助全球最大的云端服务供应商们快速开发和部署加速平台。专门针对

2018-07-31 09:08:00 731

731 Xilinx 公司Virtex5 系列的FPGA 具有多重配置的特性,允许用户在不掉电重启的情况下,根据不同时刻的需求,可以从FLASH 中贮存的多个比特文件选择加载其中的一个,实现系统功能的变换。

2018-12-04 08:37:00 4654

4654

存储配置数据。配置数据决定了PLD内部互连和功能,改变配置数据,也就改变了器件的逻辑功能。SRAM编程时间短,为系统动态改变PLD的逻辑功能创造了条件。但由于SRAM的数据易失的,配置数据必须保存在PLD器件以外的非易失存储器内,才能实现在线可重配置(ICR)。

2020-01-15 07:57:00 2612

2612

结合对FPGA重配置方案的软硬件设计,本文通过PC机并通过总线(如PCI总线)将配置数据流下载到硬件功能模块的有关配置芯片,从而完成配置FPGA的全过程。该方法的软件部分基于Visual C++的开发环境,并用C++语言开发动态连接库,以用于软件设计应用程序部分的调用。

2018-12-30 09:26:00 2425

2425

由于大规模高密度可编程逻辑器件多采用SRAM工艺,要求每次上电,对FPGA器件进行重配置,这就使得可以通过监视配置的位数据流,进行克隆设计。因此,在关键、核心设备中,必须采用加密技术保护设计者的知识产权。

2018-11-20 09:28:41 1967

1967

本视频介绍了UltraScale +芯片的部分重配置功能,展示了Vivado Design Suite中部分重配置的新功能,并介绍了对部分重配置的更广泛的访问权限

2018-11-20 06:25:00 3831

3831 关键词:PLD , SRAM , 可重配置电路 由于SRAM的可重配置PLD(可编程逻辑器件)的出现,为系统设计者动态改变运行电路中PLD的逻辑功能创造了条件。PLD使用SRAM单元来保存字的配置

2019-02-23 14:30:01 675

675

All Programmable 技术和器件的全球领先企业赛灵思公司(Xilinx, Inc. (NASDAQ:XLNX))宣布,将在 2016 全球超算大会(SC16) 上发布并展示其专门针对云应用的可重配置加速方案。

2019-08-01 16:22:44 1565

1565 在当今变化的市场环境中,产品是否便于现场升级、便于灵活使用,已成为产品进入市场的关键因素。而基于 SRAM结构的 FPGA器件的出现,为系统设计者动态改变运行电路中的逻辑功能创造了条件,也为现场升级

2020-08-19 16:26:14 1803

1803

SRAM是随机存取存储器的一种。所谓的静态是指这种存储器只要保持通电,里面储存的数据就可以恒常保持。SRAM不需要刷新电路即能保存它内部存储的数据,因此SRAM具有较高的性能。 SRAM的速度快

2020-09-19 11:42:25 6553

6553 TD-LTE SRS带宽重配置导致掉话率高案例说明。

2021-03-25 09:51:33 20

20 Partial Reconfiguration(部分重配置)在现在的FPGA应用中越来越常见,我们这次的教程以Project模式为例来说明部分重配置的操作过程。

2021-07-05 15:28:24 3140

3140

星载嵌入式处理器软件在轨重配置技术研究(嵌入式开发培训费用)-该文档为星载嵌入式处理器软件在轨重配置技术研究总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-07-30 17:07:59 11

11 一般情况下,要重新配置一个FPGA需要使其处于复位状态,并通过外部控制器重新加载一个新设计到器件中。而局部重配置技术允许在FPGA内部或外部的控制器在加载一个局部设计到一个可重配置模块中时

2023-03-17 14:03:39 1508

1508 除通过外部多功能IO来选择之外,易灵思通过内部重配置实现远程更新操作也非常简单。

2023-05-30 09:24:32 712

712

单元存储配置数据。配置数据决定了PLD内部互连和功能,改变配置数据,也就改变了器件的逻辑功能。SRAM编程时间短,为系统动态改变PLD的逻辑功能创造了条件。但由于SRAM的数据易失的,配置数据必须保存在PLD器件以外的非易失 存储器 内,才能实现在线可重配置(

2023-05-30 11:00:01 434

434 存储配置数据。配置数据决定了PLD内部互连和功能,改变配置数据,也就改变了器件的逻辑功能。SRAM编程时间短,为系统动态改变PLD的逻辑功能创造了条件。但由于SRAM的数据易失的,配置数据必须保存在PLD器件以外的非易失存储器内,才能实现在线可重配置(ICR)。

2023-05-30 10:59:00 449

449

SRAM (Static Random Access Memory)是一种高速、随机访问的存储器,它以其快速的读写操作和不需要刷新的特点而受到广泛使用。本文将详细介绍SRAM的读写电路

2023-12-18 11:22:39 501

501

电子发烧友App

电子发烧友App

评论