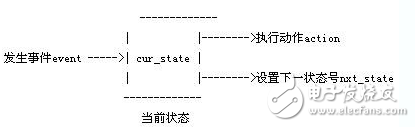

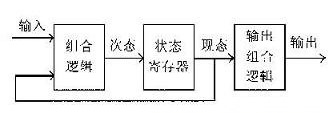

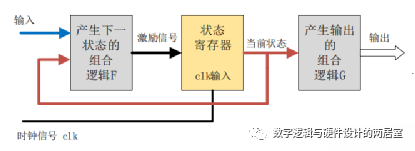

数字系统通常划分为信息处理单元和控制单元。信息单元主要进行信息的传输和运算, 而控制单元的主要任务是控制信息处理单元的微操作的顺序。控制单元的实现方式有: 有限状态机、控制寄存器和微代码控制器等。有限状态机在时间尺度上对其控制信号进行离散化控制, 利用状态转移使控制信号在有限状态机的状态节拍控制下变化, 以实现对被控对象的控制。有限状态机设计的关键是如何把一个实际的时序逻辑关系抽象成一个时序逻辑函数,传统的电路图输入法通过直接设计寄存器组来实现各个状态之间的转换, 而用硬件描述语言来描述有限状态机, 往往是通过充分发挥硬件描述语言的抽象建模能力,通过对系统在系统级或寄存器传输级进行描述来建立有限状态机。EDA 工具的快速发展,使通过CAD快速设计有限状态机自动化成为可能。

传统上在系统级和寄存器传输级完成VHDL 的描述主要分以下几步:

(1) 分析控制器设计指标, 建立系统算法模型图;

(2) 分析被控对象的时序状态, 确定控制器有限状态机的各个状态及输入.输出条件;

(3) 应用VHDL 语言完成描述。使用XILINX的ISE6.1软件包能加速有限状态机设计,大大简化状态机的设计过程,实现状态机设计的自动化。下面分析二个简单的状态机设计实例来介绍使用ISE6.1软件包中STATECAD来介绍快速设计有限状态机的方法。使用STATECAD进行状态机设计的流程如下:

(1) 分析控制器设计指标, 建立系统算法模型图;

(2) 分析被控对象的时序状态, 确定控制器有限状态机的各个状态及输入.输出条件;

(3) 在STATECAD中输入有限状态机状态图,自动产生VHDL模型描述,使用STATEBENCH进行状态转移分析,分析无误后使用导出VHDL模型块到ISE中进行仿真后综合,实现到CPLD或FPGA的映射。设计人员的主要工作在第一步。第二步,第三步基本上可以通过STATECAD完成有限状态机的自动生成和分析,还可以利用分析结果来对被控对象的逻辑进行分析,改进,完善系统控制逻辑。

下面以一个VCR控制机状态机设计过程来介绍如何使用STATECAD设计状态机。

VCR控制机描述:外部输入:

1.POWERSWITCH---------电源开关

2.STOP----------------停按钮

3.PLAY――――――――播放按钮

4.RECORD―――――――录影按钮输出状态:

1. 有电显示:电源指示灯亮,播放指示灯灭,录影指示灯灭;

2. 按播放按钮,进入播放状态,播放指示灯亮,电源指示灯亮,录影指示灯灭;按停按钮,退出播放状态回到有电状态,播放指示灯灭,电源指示灯亮,录影指示灯灭;

3. 按录影按钮,进入录影状态,录影指示灯亮;按停按钮,退出录影状态回到有电状态;电源指示灯亮,播放指示灯灭,录影指示灯灭;

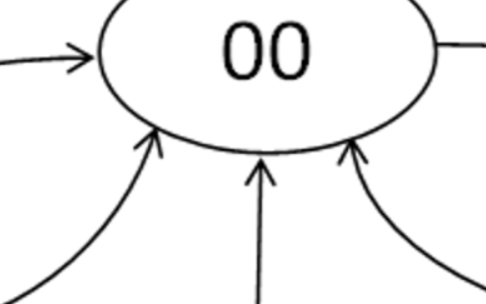

4. 电源开关断开,电源指示灯灭,播放指示灯灭,录影指示灯灭;打开STATECAD,输入如下的状态图:

进行逻辑优化(工具自动进行逻辑优化)后,使用STATEBENCH进行状态转移分析。以下是自动状态转移模拟波形。

也可以进行行为状态模拟:如以下动作的模拟波形,按电源开关上电,按播放按钮,按播放按钮,按停按钮,按录影按钮,按停按钮,电源开关断电。

综合以上的模拟波形结果,可以看到状态机安装指定的状态转移图工作。

导出VHDL模型块到ISE中进行仿真后综合后可以适配到XC9536-5-PC44芯片,适配结果如下:宏模块使用 Pterms Used 寄存器使用情况 引脚使用情况 IOB使用情况

9/36 (25%) 37/180 (21%) 9/36 (25%) 13/34 (39%) 11/72 (16%)进行引脚锁定后就可以进行编程。

代码如下:

-- D:\XILINXTUTORIAL\VCRSTATE.vhd

-- VHDL code created by Xilinx's StateCAD 6.1iLIBRARY ieee;

USE ieee.std_logic_1164.all;ENTITY VCRSTATE IS

PORT (CLK,PLAYSWITCH,POWERSWITCH,RECORDSWITCH,RESET,STOPSWITCH: IN std_logic ;

PLAYLED,POWERLED,RECORDLED : OUT std_logic);

END;ARCHITECTURE BEHAVIOR OF VCRSTATE IS

TYPE type_sreg IS (OFF,PLAY,POWERON,RECORDING);

SIGNAL sreg, next_sreg : type_sreg;

SIGNAL next_PLAYLED,next_POWERLED,next_RECORDLED : std_logic;

BEGIN

PROCESS (CLK, RESET, next_sreg, next_PLAYLED, next_POWERLED, next_RECORDLED)

BEGIN

IF ( RESET='1' ) THEN

sreg <= OFF; PLAYLED <= '0';

POWERLED <= '0'; RECORDLED <= '0';

ELSIF CLK='1' AND CLK'event THEN

sreg <= next_sreg; PLAYLED <= next_PLAYLED;

POWERLED <= next_POWERLED; RECORDLED <= next_RECORDLED;

END IF;

END PROCESS;PROCESS (sreg,PLAYSWITCH,POWERSWITCH,RECORDSWITCH,STOPSWITCH)

BEGIN

next_PLAYLED <= '0'; next_POWERLED <= '0'; next_RECORDLED <= '0';

next_sreg<=OFF;

CASE sreg IS

WHEN OFF =>

IF ( POWERSWITCH='1' ) THEN

next_sreg<=POWERON; next_POWERLED<='1';

next_PLAYLED<='0'; next_RECORDLED<='0';

ELSE

next_sreg<=OFF; next_POWERLED<='0';

next_PLAYLED<='0'; next_RECORDLED<='0';

END IF;

WHEN PLAY =>

IF ( POWERSWITCH='1' AND STOPSWITCH='0' ) THEN

next_sreg<=PLAY; next_POWERLED<='1';

next_PLAYLED<='1'; next_RECORDLED<='0';

END IF;

IF ( POWERSWITCH='0' ) THEN

next_sreg<=OFF; next_POWERLED<='0';

next_PLAYLED<='0'; next_RECORDLED<='0';

END IF;

IF ( STOPSWITCH='1' AND POWERSWITCH='1' ) THEN

next_sreg<=POWERON; next_POWERLED<='1';

next_PLAYLED<='0'; next_RECORDLED<='0';

END IF;

WHEN POWERON =>

IF ( POWERSWITCH='0' ) THEN

next_sreg<=OFF; next_POWERLED<='0';

next_PLAYLED<='0'; next_RECORDLED<='0';

ELSIF ( RECORDSWITCH='1' ) THEN

next_sreg<=RECORDING; next_POWERLED<='1';

next_PLAYLED<='0'; next_RECORDLED<='1';

ELSIF ( PLAYSWITCH='1' ) THEN

next_sreg<=PLAY; next_POWERLED<='1';

next_PLAYLED<='1'; next_RECORDLED<='0';

ELSE

next_sreg<=POWERON; next_POWERLED<='1';

next_PLAYLED<='0'; next_RECORDLED<='0';

END IF;

WHEN RECORDING =>

IF ( POWERSWITCH='1' AND STOPSWITCH='0' ) THEN

next_sreg<=RECORDING; next_POWERLED<='1';

next_PLAYLED<='0'; next_RECORDLED<='1';

END IF;

IF ( POWERSWITCH='0' ) THEN

next_sreg<=OFF; next_POWERLED<='0';

next_PLAYLED<='0'; next_RECORDLED<='0';

END IF;

IF ( STOPSWITCH='1' AND POWERSWITCH='1' ) THEN

next_sreg<=POWERON; next_POWERLED<='1';

next_PLAYLED<='0'; next_RECORDLED<='0';

END IF;

WHEN OTHERS =>

END CASE;

END PROCESS;

END BEHAVIOR;整个状态机实现过程比相当简单。快捷。有效。

用STATECAD快速设计有限状态机

- 寄存器(117355)

- vhdl(127605)

- 状态机(27117)

相关推荐

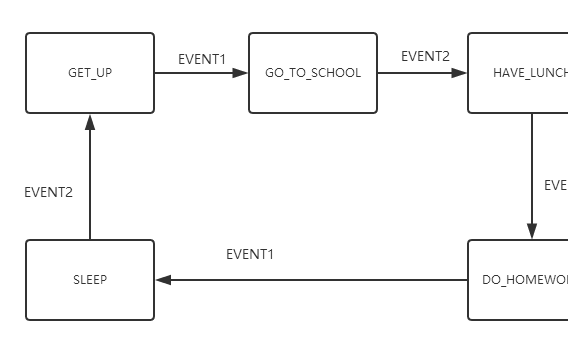

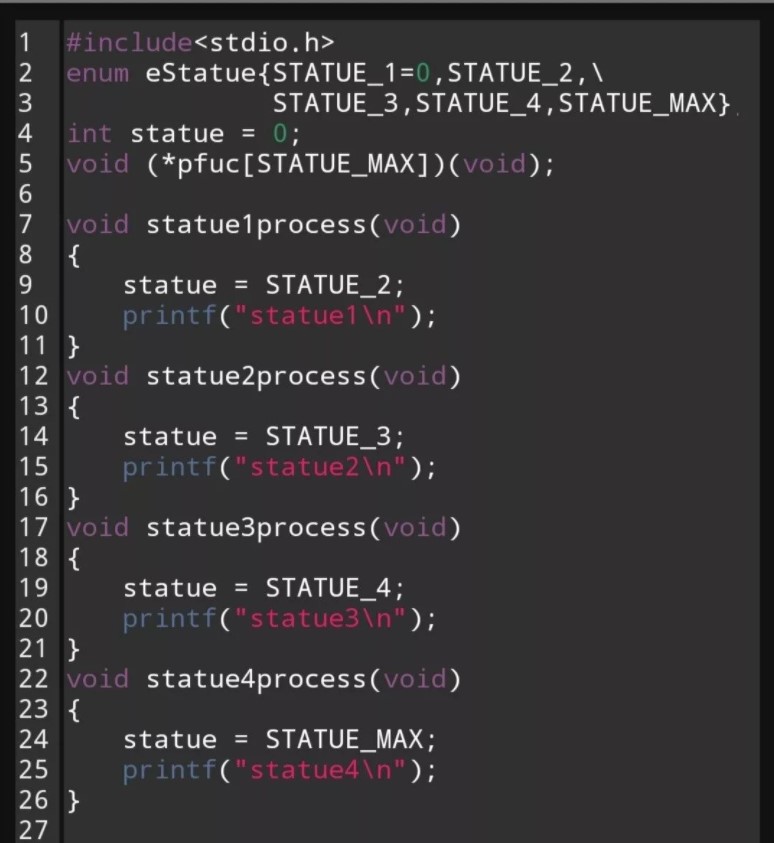

基于C语言的状态机实现方案

关于状态机,基础的知识点可以自行理解。本文主要讲解的是一个有限状态机FSM通用的写法,目的在于更好理解,移植,节省代码阅读与调试时间,体现出编程之美。

2023-09-13 09:28:42 282

282

282

282

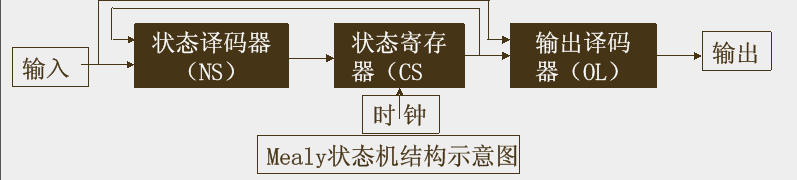

Verilog状态机+设计实例

的是有限状态机(Finite-State Machine,FSM),简称为状态机,表示在有限个状态以及这些状态之间的转移和动作等行为的数学模型。 二、分类 在verilog中常使用的状态机可以分为两类,分别是Moore(摩尔)状态机和Mealy(米利)状态机。两种状态机的主要区别在于

2024-02-12 19:07:39 1818

1818

1818

1818

有限状态机的相关资料推荐

软件开发第四讲 - 按键检测(状态机)一、工具链接1、Keil c51 UV4https://yunpan.360.cn/surl_yrIfYYmeRFk2、STC-ISP下载软件https

2022-02-18 06:51:28

状态机编程

等待一段时间后,光标的位置就会右移,表示对最后输入字符的确认。因此,按键输入接口设计和实现的核心,更多的体现在软件接口处理程序的设计中。下面将以此为例,介绍有限状态机的分析设计原理,以及基于状态机思想

2008-07-10 18:00:24

FPGA Verilog HDL 设计实例系列连载--------有限状态机设计

数字系统有两大类有限状态机(Finite State Machine,FSM):Moore状态机和Mealy状态机。Moore状态机 其最大特点是输出只由当前状态确定,与输入无关。Moore状态机

2012-03-09 10:04:18

ISM330DHCX嵌入式有限状态机的使用和配置信息

本文档旨在提供有关 ST 的 ISM330DHCX嵌入式有限状态机的使用和配置的信息。ISM330DHCX 可配置为由用户定义的运动模式激活中断信号生成。为此,最多可以为运动检测独立编程 16 组嵌入式有限状态机。

2023-09-08 08:00:23

LSM6DSOX嵌入式有限状态机的使用和配置的信息

本文档旨在提供有关 ST 的 LSM6DSOX 嵌入式有限状态机的使用和配置的信息。LSM6DSOX 可配置为由用户定义的运动模式激活中断信号生成。为此,最多可以为运动检测独立编程 16 组嵌入式有限状态机

2023-09-06 06:36:09

LSM6DSOX嵌入式有限状态机的使用和配置的信息

本文档旨在提供有关 ST 的 LSM6DSOX 嵌入式有限状态机的使用和配置的信息。LSM6DSOX 可配置为由用户定义的运动模式激活中断信号生成。为此,最多可以为运动检测独立编程 16 组嵌入式有限状态机。

2023-09-13 07:33:03

raw os 之状态机编程

状态机编程的历史很可能久于传统的操作系统, 传统的一个大while 循环模式普遍用到了状态机模式编程, 状态机一般是基于fsm 的有限状态机,或者更先进点的是hsm 分层的状态机。具体的fsm 以及

2013-02-27 14:35:10

【FPGA开源教程连载】第七章 状态机设计实例

always模块描述状态输出(可以用组合电路输出,也可以时序电路输出)。可以看出两段式有限状态机与一段式有限状态机的区别是FSM将时序部分(状态转移部分)和组合部分(判断状态转移条件和产生输出)分开,写为

2016-12-26 00:17:38

【Z-turn Board试用体验】有限状态机三段式描述方法(转载)

;(2)二段式:用两个always模块来描述状态机,其中一个always模块采用同步时序描述状态转移;另一个模块采用组合逻辑判断状态转移条件,描述状态转移规律以及输出;(3)三段式:在两个always

2015-05-25 20:33:02

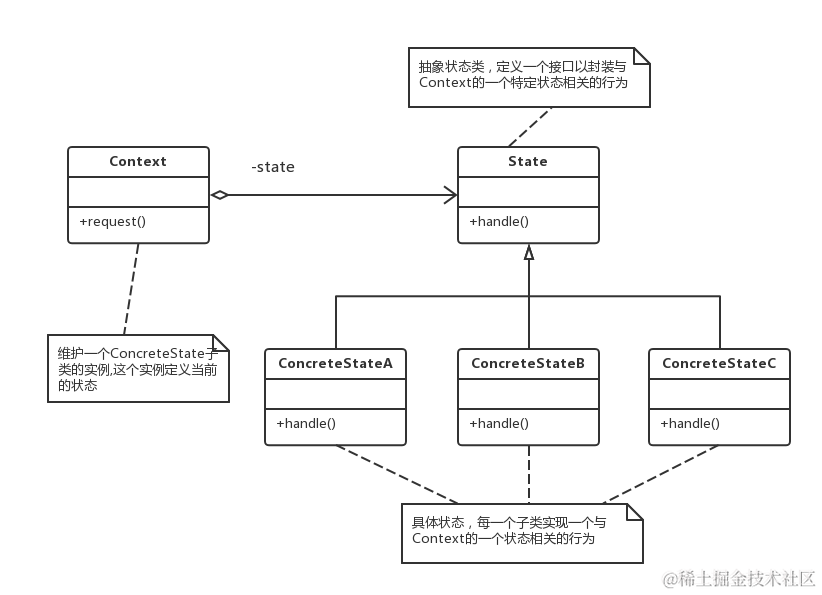

什么是有限状态机FSM

什么是有限状态机FSM简述 有限状态机(以下用FSM指代)是一种算法思想,简单而言,有限状态机由一组状态、一个初始状态、输入和根据输入及现有状态转换为下一个状态的转换函数组成。在Gof的23种

2008-06-04 10:35:23

什么是有限状态机呢

在嵌入式,机器人领域,由于多的复杂逻辑状态,我们编写程序的时候不得不考虑很多种情况,容易造成功能间的冲突。有限状态机(finite-state machine),简称状态机,是一种表示有限个状态以及状态间转移等行为的数学模型。状态机简单来说

2021-12-20 06:51:26

如何利用STM32去实现一种按键有限状态机呢

STM32实现按键有限状态机(超详细,易移植)一、状态机简而言之,状态机是使不同状态之间的改变以及状态时产生的相应动作的一种机制。1.1状态机的四要素现态:状态机当前状态。触发条件:改变当前状态

2022-02-16 06:58:52

浅谈有限状态机FSM——以序列检测为例

应用,往往需要让硬件来实现一些具有一定顺序的工作,这就是要用到状态机的思想。(以上摘自特权同学的《深入浅出玩转FPGA》一书) 有限状态机FSM(Finite State Machine)是数字电路

2014-09-25 09:35:29

谁能说说状态机怎么用啊?

如题,状态机本身好写,但是具体怎么用,没用过状态机真是感觉很低端。 比如用状态机产生一个波形,除了输入输出还有很多寄存器用于控制,都写在一起呢,还是把状态机独立出来为一个module,然后再根据这个module来控制电路。 我是状态机小白,请大家交流交流。

2014-02-18 22:31:47

fsm有限状态机pdf

利用 VHDL 设计的许多实用逻辑系统中,有许多是可以利用有限状态机的设计方案来描述和实现的。无论与基于 VHDL的其它设计方案相比,还是与可完成相似功能的 CPU 相比,状

2008-06-04 10:33:10 75

75

75

75一种改进的遗传算法进化有限状态机

提出了一种改进的遗传算法,针对有限状态机中输出矢量与状态转移相关的特性,将配置有限状态机的染色体分解为状态转移基因和输出矢量基因进行分阶段的进化实验。实验结

2009-05-10 11:55:33 18

18

18

18基于有限状态机的工控系统软件设计

通过分析工控系统的特性,提出采用状态机的思想进行工控软件设计。详细论述了高速状态机的错步问题以及控制层中状态机的状态划分问题。结合具体的应用实例,给出了基于状

2009-08-10 14:26:08 30

30

30

30基于有限状态机的虚拟训练过程模型研究

通过一个基于操作规程的虚拟训练系统研究了系统仿真流程,分析了有限状态机(FSM)的原理,结合虚拟仿真训练的特点,设计出了操作过程模型,并通过Windows 消息机制编程实

2009-12-07 14:23:01 14

14

14

14有限状态机的硬件描述语言设计方法

实验目的

1、 熟悉用硬件描述语言(VHDL)设计一般状态机所包含的几个基本部分;2、 掌握用硬件描述语言(VHDL)设计Moore型和Mealy型有限状态机的方法;3、 了解状态

2010-09-03 09:48:17 0

0

0

0ST推出LIS3DSH内置2个有限状态机的三轴高分辨率加速度计

意法半导体简称ST;纽约证券交易所代码:STM)推出业界首款内置2个有限状态机的三轴高分辨率加速度计。

2011-11-07 23:33:20 4021

4021

4021

4021如何使用STATECAD进行多状态机设计实例分析

有限状态机设计的关键是如何把一个实际的时序逻辑关系抽象成一个时序逻辑函数,传统的电路图输入法通过直接设计寄存器组来实现各个状态之间的转换, 而用硬件描述语言来描述有限

2011-11-11 09:49:28 1886

1886

1886

1886

有限状态机网络配置管理研究

设计了有限状态机模型,实现了对不同设备命令的统一转换。基于统一命令转换,实现了Telnet对远程设备的统一命令配置,通过SNMP协议可视化配置设备更加方便。

2011-12-14 14:35:47 22

22

22

22基于RTL综合策略的状态机优化方案

有限状态机及其设计技术是数字系统设计中的重要组成部分,是实现高效率、高可靠性逻辑控制的重要途径。本文论述了两种针对状态机的综合策略实现

2012-01-05 10:34:21 2056

2056

2056

2056

基于VHDL的MTM总线主模块有限状态机设计

为了能够更简洁严谨地描述MTM总线的主模块有限状态机的状态转换,同时减少FPGA芯片功耗,提高系统稳定性,文中在分析MTM总线结构和主模块有限状态机模型的基础上,基于VHDL语言采

2012-05-29 15:39:09 20

20

20

20基于有限状态机的UART设计

文章结合UART的设计,分析阐述了硬件设计中的有限状态自动机理论;并在分析UART功 能特点的基础上,给出了利用有限状态自动机理论进行UART设计的实例 。

2016-03-22 15:53:07 7

7

7

7基于有限状态机实现全双工可编程UART

Transmitter 通用异步收发器) 。 重点讨论了使用 FSM(有限状态机) 技术进行接收器和发送器两大核心模块的设计实现 以及接收器能够正常工作的关键技术 ———倍频采样技术。

2016-03-22 15:52:23 4

4

4

4有限状态机在嵌入式系统中的实现及应用

如何使嵌入式软件代码更加可靠 增强程序的可维护性 一直以来都是嵌入式程序员追 求的目标。论述了有限状态机的原理和其实现方法;采用状态机方法编写了一个按键扫描程序介绍了状态机编程在嵌入式系统中的实际应用和优点。

2016-03-22 15:40:22 1

1

1

1有限状态机的建模与优化设计

本文提出一种优秀 、高效的 Verilog HDL 描述方式来进行有限状态机设计 介绍了 有限状态机的建模原则 并通过一个可综合的实例 验证了 该方法设计的有限状态机在面积和功耗上的优势。

2016-03-22 15:19:41 1

1

1

1初学者对有限状态机(FSM)的设计的认识

有限状态机(FSM)是一种常见的电路,由时序电路和组合电路组成。设计有限状态机的第一步是确定采用Moore状态机还是采用Mealy状态机。

2017-02-11 13:51:40 3881

3881

3881

3881

基于存储器映射的有限状态机逻辑实现方法

在FPGA对Flash控制操作中,有限状态机(Finite State Machine,FSM)与多进程描述方式相比有着层次分明、结构清晰、易于修改和移植的明显优势而被广泛应用。传统状态机在描述实现

2017-11-17 02:30:07 3184

3184

3184

3184

基于有限状态机和查找表的RICE解码结构

和通用性上都不理想。针对RICE算法中自适应熵编码的特点,设计了一种基于有限状态机和查找表的并行RICE解码结构,可在FPGA上完成8比特宽度的并行解码,解码速度最高可达176 MB/s;同时,该解码结构适用于编码参数足变化的情况,具有很强的通用性。

2017-11-20 14:21:55 8

8

8

8用状态机原理进行软件设计

个组成部分。 不过,状态机理论的发展却很缓慢。在众多原因中,状态机只是做为编程的实现工具而不是设计工具是一个最重要的原因。 本文的重点就在于,怎样利用状态机原理进行程序设计。本文会先给出普通的、一个平面上的FSM(有限状态机)的概念和实例,并指出

2017-12-02 15:03:07 413

413

413

413利用74LS161实现复杂状态机

本文主要介绍了是如何利用74LS161实现复杂状态机的。时序逻辑电路的数学模型是有限状态机。有限状态机它把复杂的控制逻辑分解成有限个稳定状态,在每个状态上判断事件,变连续处理为离散数字处理,符合计算机的工作特点。本文主要讨论使用MSI同步计数器74LS161进行复杂状态机的设计。

2018-01-18 09:00:02 8299

8299

8299

8299

状态机和组合逻辑的冒险竞争浅析

有限状态机(Finite State Machine, FSM),根据状态机的输出是否与输入有关,可分为Moore型状态机和Mealy型状态机。Moore型状态机输出仅仅与现态有关和Mealy

2018-06-25 08:42:00 3638

3638

3638

3638MOORE型有限状态机的设计方案分析

随着微电子技术的迅速发展,人们对数字系统的需求也在提高。不仅要有完善的功能,而且对速度也提出了很高的要求。对于大部分数字系统,都可以划分为控制单元和数据单元两个组成部分。通常,控制单元的主体是一个有限状态机,它接收外部信号以及数据单元产生的状态信息,产生控制信号序列。

2019-06-10 08:03:00 4833

4833

4833

4833

Linux编程之有限状态机FSM的理解与实现

有限状态机(finite state machine)简称FSM,表示有限个状态及在这些状态之间的转移和动作等行为的数学模型,在计算机领域有着广泛的应用。FSM是一种逻辑单元内部的一种高效编程方法,在服务器编程中,服务器可以根据不同状态或者消息类型进行相应的处理逻辑,使得程序逻辑清晰易懂。

2019-05-15 16:53:39 1813

1813

1813

1813

使用层次型有限状态机对售货机控制器实现改造设计

有限状态机是一种具有离散输入输出系统的模型,在任何时刻都处于一个特定的状态。对于事件驱动的程序设计,它是非常有用的设计模型。在某一个状态下有事件发生时,根据当前状态和输入事件的不同,选择如何处

2020-05-03 17:49:00 2402

2402

2402

2402使用函数指针的方法实现状态机

之前写过一篇状态机的实用文章,很多朋友说有几个地方有点难度不易理解,今天给大家换种简单写法,使用函数指针的方法实现状态机。 状态机简介 有限状态机FSM是有限个状态及在这些状态之间的转移和动作等行为

2020-10-19 09:36:53 2141

2141

2141

2141

如何使用FPGA实现序列检测有限状态机

有限状态机是绝大部分控制电路的核心结构, 是表示有限个状态以及在这些状态之间转移和动作等行为的数学模型。有限状态机是指输出取决于过去输入部分和当前输入部分的时序逻辑电路。一般来说, 除了输入部分和

2020-11-04 17:17:04 12

12

12

12基于有限状态机的FlexRay时钟同步机制

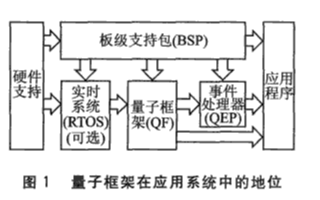

工作的能力,其信息传输的确定性离不开其内部的时钟同步机制的支持。时钟同步机制可根据该节点启动的不同工作阶段,定义成不同的工作状态,如初始化、等待接收同步帧等。考虑到传统的FSM方法建立模型存在代码难以复用、维护困难等问题,本文基于量子框架的角度,采用有限状态机的方法对FlexRay时钟同步机制进行研究。

2021-03-31 10:22:27 2908

2908

2908

2908

使用Synplify设计安全的VHDL状态机

Synplify的优势之一是有限状态机编译器。 这是一个强大的功能,不仅具有自动检测状态机中的状态的能力源代码,并使用顺序编码,灰色编码或一键编码实现它们。但也要进行可达性分析,以确定所有可能的状态达到并优化掉所有无法达到的状态和转换逻辑。因此,产生状态机的高度优化的最终实现。

2021-04-07 09:20:51 12

12

12

12有限状态机设计是HDL Designer Series的关键应用

有限状态机的设计是HDL Designer Series™工具的关键应用。 尽可能地对于设计人员编写导致状态机性能不佳的VHDL,可以使用HDL Designer用于生成VHDL的Series™工具

2021-04-08 10:05:23 3

3

3

3基于事件驱动的有限状态机介绍

一、介绍 EFSM(event finite state machine,事件驱动型有限状态机),是一个基于事件驱动的有限状态机,主要应用于嵌入式设备的软件系统中。 EFSM的设计原则是:简单

2021-11-16 15:29:10 2036

2036

2036

2036基于STM32F103C8T6的多按键检测 | 有限状态机短按、长按识别 | 标准库函数实现方法

制作航模遥控器需要用到多按键检测,使用有限状态机实现检测短按、长按,修正了原文中的一些错误

2021-11-26 11:21:04 36

36

36

36STM32实现按键有限状态机(超详细,易移植)

STM32实现按键有限状态机(超详细,易移植)一、状态机简而言之,状态机是使不同状态之间的改变以及状态时产生的相应动作的一种机制。1.1状态机的四要素现态:状态机当前状态。触发条件:改变当前状态

2021-12-17 18:37:10 25

25

25

25C语言状态机编程思想

关注、星标公众号,直达精彩内容文章来源:头条-嵌入式在左C语言在右链接:https://www.toutiao.com/i6843028812112855564/有限状态机概念有限状态机...

2022-01-13 13:32:23 14

14

14

14如何以面向对象的思想设计有限状态机

有限状态机又称有限状态自动机,简称状态机,是表示有限个状态以及在这些状态之间的转移和动作等行为的数学计算模型,用英文缩写也被简...

2022-02-07 11:23:28 4

4

4

4介绍一种高效率的c语言状态机

状态机对于有一定编程经验的程序员一定会用到,因为对于我们的各种各样的模块他们都会有各种状态,其他模块都会根据这些状态和数据进行处理;同时在网络编程方面也会根据网络状态和消息类型进行相应处理等等方面状态机的使用是非常广泛的,我们通常称这种状态机为有限状态机—FSM。

2022-08-12 09:07:59 2461

2461

2461

2461

如何构建基于状态机的软件系统

有限自动机(Finite Automata Machine)是计算机科学的重要基石,它在软件开发领域内通常被称作有限状态机(Finite State Machine),是一种应用非常广泛的软件设计

2022-09-14 10:55:27 1245

1245

1245

1245基于事件驱动的有限状态机介绍

EFSM(event finite state machine,事件驱动型有限状态机),是一个基于事件驱动的有限状态机,主要应用于嵌入式设备的软件系统中。

2023-02-11 10:17:15 709

709

709

709FPGA中有限状态机的状态编码采用格雷码还是独热码?

有限状态机是由寄存器组和组合逻辑构成的硬件时序电路,其状态(即由寄存器组的1和0的组合状态所构成的有限个状态)只可能在同一时钟跳变沿的情况下才能从一个状态转向另一个状态,究竟转向哪一状态还是留在原状态不但取决于各个输入值,还取决于当前所在状态。这里是指Mealy型有限状态机。

2023-04-07 09:52:46 909

909

909

909Verilog状态机的类型

有限状态机(Finite-State Machine,FSM),简称状态机,是表示有限个状态以及在这些状态之间的转移和动作等行为的数学模型。

2023-06-01 15:23:39 1260

1260

1260

1260

一个基于事件驱动的有限状态机

EFSM(event finite state machine,事件驱动型有限状态机),是一个基于事件驱动的有限状态机,主要应用于嵌入式设备的软件系统中。 EFSM的设计原则是:简单!EFSM的使用者只需要关心:

2023-08-30 09:28:51 448

448

448

448

三段式,四段式状态机设计方法是什么(状态机设计注意事项)

有限状态机,简称状态机,通俗的说,就是把全部的情况分成几个场景,这些场景的工作方式明显不同。简单来说就是如下所示的状态转移图

2023-08-31 15:30:49 585

585

585

585

什么是有限状态机?有限状态机的四要素介绍

如果一个对象(系统或机器),由若干个状态构成,在某种条件下触发这些状态,会发生状态相互转移的事件,那么此对象称之为状态机。

2023-09-17 16:42:34 1513

1513

1513

1513BGP有限状态机有哪几种状态?

BGP有限状态机共有六种状态,分别是Idle、Connect、Active、OpenSent、OpenConfirm和Established。

2023-10-07 14:56:55 897

897

897

897什么是状态机?状态机的种类与实现

状态机,又称有限状态机(Finite State Machine,FSM)或米利状态机(Mealy Machine),是一种描述系统状态变化的模型。在芯片设计中,状态机被广泛应用于各种场景,如CPU指令集、内存控制器、总线控制器等。

2023-10-19 10:27:55 3405

3405

3405

3405什么是有限状态机?如何解决传统有限状态机「状态爆炸」问题?

有限状态机(Finite State Machine,简称FSM)是一种用来进行对象行为建模的工具,其作用主要是描述对象在它的生命周期内所经历的状态序列以及如何响应来自外界的各种事件。

2024-02-17 16:09:00 612

612

612

612

电子发烧友App

电子发烧友App

评论