摘要: 给出一种基于FPGA的新型谐波分析仪的设计方案。在该方案中,采用FPGA实现快速的FFT运算,使用实时操作系统结合Ethernet芯片实现TCP/IP协议直接接入局域网,并给出实现的设计实现。

关键词: FPGA Verilog HDL Nios 谐波分析仪 实时操作系统

引言

随着节能技术和自动化技术的推广,电力电子装置如变频设备、变流设备等,容量日益扩大,数量日益增多,使电网中的谐波污染日益严重,给电力系统和各类用电设备带来危害,轻则增加能耗,缩短寿命,重则造成用电事故,影响安全生产。因此,消除谐波污染,把谐波含量控制在允许范围内,已成为主管部门和用电单位的共同奋斗目标。

目前,电力系统中的谐波源,不但类型多,而且分布广,用户电网中的谐波电流可能来自本身的非线性设备,也可能来自外线路,如不加以区分将给谐波治理造成困难。因此进行谐波治理之前,必须要了解电网中谐波的次数及其含量,即必须进行谐波的测试。谐波测量是谐波问题的一个重要分支,它是谐波问题研究的主要依据,也是研究分析问题的出发点。

当前谐波测量的主要方式有3种。

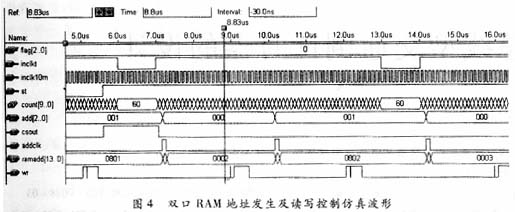

图1

(1)采用模拟滤波器的谐波测量

最早的谐波测量是采用模拟滤波器实现的。即采用带阻滤波器将基波分量滤波,得到谐波分量;或采用带通滤波器得出基波分量,再与被检测量相减得到谐波分量。该检测方法的优点是电路结构简单,造价低,输出阻抗低,品质因素易于控制。但也有很多缺点,如精度不高、误差较大等。

(2)基于傅里叶变换的谐波测量

随着计算机和微电子技术的发展,基于傅里叶变换的谐波测量是当今应用最多也是最广的一种方法。它的核心理论建议在傅里叶变换的基础上。根据傅里叶变换理论,将模拟信号采信变成离散化数字序列信号后,输入微型计算机进行傅里叶变换,计算得到基波和频率为基波频率整数倍的多次谐波的幅值和相位,然后将计算获得的数据显示在屏幕上或存放在磁盘中供将来统计使用。

(3)利用小波分析方法的谐波测量

小波分析作为调和分析的重大进展,克服了傅里叶变换的频域完全局部性,而在时域完全无局部性的缺点,即它在频域和时域同时具有局部性。通过对含有谐波的电流信号进行正交小波分解,利用多分辨的概念,将低频段(高尺度)上的结果看作不含谐波的基波分量。基于这种算法,可以利用软件构成谐波检测环节,同时由于其计算速度快,能快速跟踪谐波的变化。小波变换应用在谐波测量方面尚处于初始阶段。

目前市场主流的谐波测量仪器均基于快速傅里叶变换理论基础。将输入的模拟量电流电压通过A/D采样环节变换成离散的数字量,然后进行快速傅里叶变换,计算获得基波和各次谐波的复数值,然后根据国家标准计算相应的谐波指标并显示最终结果。基于FFT的谐波时域测量仪器一般采用两种实现方式:使用工业PC机或者采用高档嵌入式系统。两类实现方式性能可靠、运算快速、技术成熟,是目前市场的主流产品。其缺点在于成本过高、难以扩展输入通道数、运算时消耗系统资源大。就广大电力系统用户而言,对成本低廉、运算快速、易于进行通道扩展的谐波分析仪有强烈的市场需求。

本文给出了种基于FPGA的新型谐波测量仪,该仪器集成了A/D采样单元、FFT运算处理单元、显示单元和网络通信单元。系统使用FPGA内部实现的处理器Nios作为系统的嵌入式处理器,来控制14位高速A/D采样芯片、FFT运算核和实现网络通信功能、显示功能。其FFT运算处理单元核心为基于FPGA的FFT运算核,采用先进的多层并行流水线技术,可以在200μs内完成1024点的标准单精度浮点数FFT运算,理论上可以实现8路工频输入信号的FFT运算处理;A/D采样单元使用14位高速A/D采样芯片实现8路信号扫描采样功能,并利用锁相环实现同步采样;显示单元为LCD显示屏;网络通信基于Ethernet和RS485,使用RFC 1600规范。该系统成本低廉,易于扩展、处理能力强大、可测量8路输入信号50次以内谐波,精度可以达到GB/T 17626.7规定的A级测量仪器精度要求。

1 系统总体设计

系统总体结构如图1所示。

该系统从结构上分为CT/PT变送单元、A/D采样单元、FFT运算处理单元、控制单元、显示单元和网络接口单元。CT/PT变送单元负责将输入的150~390V电压信号线性变换为5mA的电流信号,输入的0~15A电流信号线性变换5mA的电流信号,并对信号进行相位补偿;A/D采样单元对从CT/PT变送单元输出的模拟信号每周波采样256点,精确变换成14位的数字量;FFT运算处理单元负责处理A/D采样单元输出的数字量,进行256点FFT变换运算;显示单元负责显示系统的全部显示信息;网络接口单元负责提供网络通信的硬件实现电路;控制单元负责系统各个单元的控制,如控制A/D采样单元的采样频率和采样的启动及停止、PLL电路的输出频率计算、键盘输入的响应、网络通信的软件实现、FFT运算处理单元的控制和数据传输等。

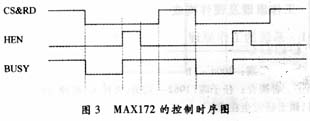

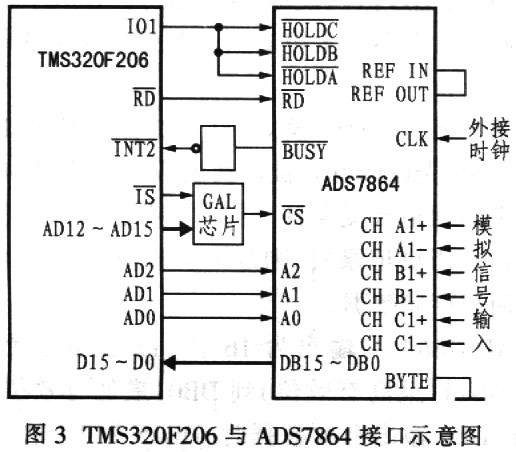

图3

从该系统结构可见,其FFT运算处理单元承担FFT运算的巨大运算任务,从而大大减轻了控制单元的工作量,其处理器单元Nios只需完成TCP/IP的协议实现和简单的控制功能。该系统提供了Ethernet和标准RS485接口,可以直接接入局域网或通过标准IEC4000-5-104规约直接接入电力调度网,具有良好的网络通信功能,便于用户将该分析仪无缝接入电力调度网或生产控制网。用户可以通过局域网对该分析仪进行控制或进行谐波数据传输,也可直接在该仪器上进行控制数据查阅。

2 系统具体实现

CT/PT传感器单元是该系统的关系环节之一,其性能直接决定整个系统能达到的精度等级。对其性能的主要要求有非线性度、相移、线性范围、小信号响应和高频衰减。非线性度、相移、线性范围是最基本的性能指标,按照该系统的精度要求,非线性度必须小于0.1%;相移必须小于5';线性范围必须大于系统的输入范围并20%的裕量。小信号响应主要针对于CT,因输入电流从0~15A变化,当输入电流非常小时仍然需要精确变换,因此对CT的小信号性能要求较高。高频衰减指标主要对高次谐波,通常传感器对于高频率信号有较强的衰减作用,表现为低通滤波器。而本系统最高需对2.5kHz信号进行采样分析,因此高频衰减也是非常重要的指标不。本系统按照以上指标选用高性能CT/PT传感器,满足系统的精度要求。

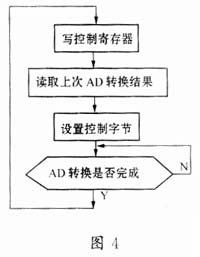

A/D采样单元采用了Maxim公司的MAX125高速8通道14位同步A/D采样芯片,该芯片具有8个采样通道,可以时对4个通道进行扫描采样,每个采样周期只需对该芯片进行两次读操作便能完成8个通道的采样。A/D转换使用逐次逼进去,采样总速率为250kHz,4通道同步扫描采样时单个通道的采样速率大于30kHz,远远超过本系统对16个通道同步采样的速率要求。该芯片通过内部集成的多路开关来实现4通道同步扫描采样,芯片内部有一个4×16位的RAM用于存放每次扫描采样的4通道数据。该芯片提供了14位的数据线,可以在一次扫描采样结束后在4个时钟周期内将4个采样结果全部输出。当采样位数为14位,其LSB代表(1/2 13)VIN(VIN为最大电压输入值)即VIN/8192,而该芯片的采样误差仅为2个LSB即2VIN/8192,约为0.025%VIN,所以该采样芯片能较好满足本系统的精度要求。系统对单个通道的采样速率要求为12.8kHz(每工频周波采样256点),而该芯片的单通道采样速率大于30kHz,所以该芯片能较好满足本系统的采样速率要求。

从FFT的分析可知,其误差很大程度来自采样窗口和实际波形的同步不严格,造成频谱泄漏。为消除频谱泄漏引起的误差,常用的方法有:硬件同步、加窗处理。硬件同步的方法比较多,常用的主要有使用PLL电路进行同步。按照GB/T14549-1993要求,只允许使用矩形窗和汉宁窗,使用矩形窗时窗口间不能有间隔和重叠。为减少信号的混叠和频谱泄漏,本系统的A/D采样单元通过使用高精度的PLL实现严格的同步采样,以保证窗口间无重叠和间隔,并能严格与被测信号频同步,并在FFT运算单元实现了加汉宁窗处理。采样单元基本原理如图2所示。

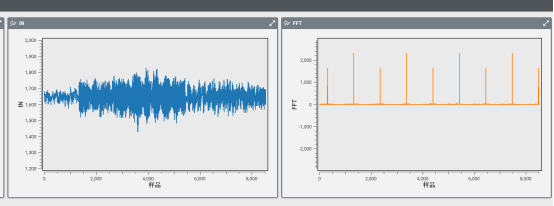

FFT运算处理单元基于一块Altera公司的EP1C20FPGA芯片,该芯片带有294912位RAM,具有20060个LE,最大I/O引脚301。FFT运算处理单元采用先进的多层并行流水线技术,工作在30MHz的频率下,可以在1ms内完成8路工频输入信号的256点FFT运算处理。该处理单元的原理如图3所示。

该单元实际包含两大部分,即采样控制逻辑部分和FFT运算部分。采样逻辑部分负责MAX125的读数据逻辑控制。FFT运算部分包括FFT控制逻辑、采样数据缓存、FFT处理核与结果存储FIFO。从IDT72V845输出的14位采样数据,首先暂存于采样数据缓存中;然后FFT处理核从该缓存中读取数据进行处理;处理完毕的数据存放于结果FIFO中;FFT控制逻辑单元向Nios处理器申请中断,Nios处理器响应应该中断向FFT控制逻辑单元发送读信号;然后从结果FIFO读取分析结果。

以往FFT设计中,往往使用定点数。因为使用定点数时,系统结构相对简单、运算速度快,但精度不高。在FPGA中使用浮点数时,系统相对设计复杂,但精度高。基于本系统对精度的苛刻要求,故采用浮点数进行FFT的硬件算术实现。FFT处理核采用先进的多层并行流水线技术,可以在1ms内完成8路256点的FFT运算。该单元实际相当于一个基于标准单精度浮点数的FFT变换协处理器,提供了简单可靠的接口以连接采样单元和处理器,并能独立进行FFT处理。

显示单元为一块普通点阵LCD显示屏,可以显示各种谐波分析的数据和简单波形。该LCD显示屏由处理器直接控制。

网络接口单元是由1块MAX485芯片和1块RealTek8019以太网接口芯片构成。MAX485芯片提供了标准的RS485接口,其通信协议为标准IEC4000-5-104规约,该规约为IEC规定的标准电力系统通信规约。通过处理器的系统软件实现,可以直接传送分析结果数据给上层使用同样规约的第三方综合自动化站或监控系统。RealTek8019是一块全双工以太网接口芯片,该芯片实现了RFC 1600规范中要求的物理层,提供了标准的以太网接口,其通信协议为标准的TCP/IP协议,通过处理器的软件实现。

控制单元核心为使用FPGA实现的处理器Nios。Nios是Altera公司提供的基于Harvard结构的RISC通用处理器IP Core,目前最新版本为3.0,有16位和32位两个版本。两个版本均使用16位的RISC指令集,差别主要于系统总线带宽。在系统开发中使用Nios,可以根据需要自行配置处理器数目可多达512个。开发者可在FPGA容量允许范围内,自由配置处理器的Cache大小、指令集ROM大小、片内RAM和ROM大小、I/O引脚数目和类型、中断引脚数目、定时器数目、通用串口数目、扩展地址和数据引脚等处理器的性能指标,而且可以在处理器ALU中直接加入自行定义的数字逻辑,并添加自行定义的处理器指令。可见,使用Nios具有极大灵活性和很高的处理效率。使用Altera公司推出的SOPC Builder开发工具,开发者可以快速开发出满足设计需要的处理器。该开发工具支持C、C++语言,并提供了常用的功能类库。开发者可以直接使用C、C++语言进行系统软件开发,然后在线调试自行设计的Nios处理器和软件。当软件达到设计要求时,可通过该工具将执行代码转换成Flash文件格式或HEX文件下载到启动Flash或FPGA器件中,使所设计的系统可独立运行。本系统使用的Nios为32位版本,约使用了2093个逻辑单元,具有64KB ROM和4KB RAM,工作在50MHz频率。设计带有3个中断引脚、1个通用定时器/计数器和1个通用串行口,与FFT运算单元整合在同一FPGA芯片中。所有FPGA设计均使用Verilog HDL硬件描述语言进行设计。

在高速数字系统中,使用直接整合在FPGA芯片中的处理器具有优越的性能。在高速数字系统中,由于信号频率的增加导致PCB连线呈现传输线特性,从而影响到信号的完整性。线路间的串扰、芯片间的连接拓扑、芯片的引脚分布和封装形式、PCB的几何特性及介电特性、过孔及电压参考平面等均会严重影响高速信号的完整性。将电路中的高速数字信号部分整合在同一FPGA芯片中,则能有效解决以上的大部分影响因素,且可充分利用FPGA内部丰富的连线资源来增加系统的数字总线资源。FPGA可实现绝大部分数字电路设计,而将所需的功能直接整合在FPGA的设计中,因此可大大减小处理器外围扩展电路数目,降低外围电路和布局走线复杂度,减少影响高速信号完整性的因素,提高系统的抗干扰能力。FPGA具有丰富的部I/O引脚,可以充分满足电路设计时的外部扩展连接需求。

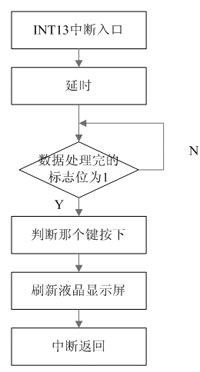

基本接口电路如图4所示。

图4

由于处理器承担着多重任务,因此在系统软件中入了实时操作系统RTOS作为操作系统环境。使用RTOS的优势是非常明显的,它可屏蔽底层设备,提供多进程的并发操作,合理调配优先极不同的任务,有效管理内存空间,使开发者可以集中精力关注于功能的实际算法,并且为软件的调试、移植和有效复用提供良好的条件。本系统使用RTOS为源代码开放的μC/OSII。ΜC/OSII是由Jean J.Labrosse编写的源代码公开的RTOS,目前被移植到多种平台上广泛使用,是一个经过实践考验的优秀RTOS。ΜC/OSII可以同时管理64个进程,每个进程必须有不同优先级。其中优先级0、1、2、3、OS_LOWEST+PRIO-3,OS_LOWEST_PRIO-2,OS_LOWEST_PRIO-1和OS_LOWEST_PRIO为系统保留,所以最大可使用54个进程。ΜC/OSII是一个抢占式的RTOS,即系统能中止低优先级进程的执行,使高优先级的进程获得执行权,这样能有效保障进程调度的实时性。由于μC/OSII的内存管理功能过弱,因此本系统软件中只使用了其进程调度、互斥同步机制及通信机制部分,自行编写了内存管理部分以适应系统网络通信时对内存管理的需求。在系统中创建了6个进程,包括中断响应进程、Ethernet管理进程、串口管理进程、采样控制进程、FFT管理进程及显示进程,其优先级依次下降。中断响应进程负责处理中断的响应和中断的响应进程调用;Ethernet管理进程负责处理TCP/IP通信事件;串行口管理进程负责处理RS485串口通信事件;采样控制进程负责管理采样控制;FFT管理进程负责FPGA的FFT处理单元和处理器之间的事务处理;显示进程负责控制LCD的显示。

具体的软件工作流程为:中断响应进程由于优先级最高,所以可以及时对所有中断进行响应处理。在具体中断发生时,中断响应进程首先判断为何种中断,然后调用相应的处理进程,同时中断响应进程放弃CPU主动休眠,从而让处于低优先级的处理进程可以获得CPU时间运行。在处理完中断后,处理进程主动休眠,在更低优先级的处理进程可以处理完被打断的工作。当所有处理进程均无处理工作时,主动唤醒中断响应进程。处于休眠态的中断响应进程可实时被中断信号所唤醒,从而保证所有中断均能得到实时响应。该系统软件使用RTOS后,程序结构清楚,开发人员可以把精力集中于控制算法上,而不必过多考虑底层的问题,从而有效缩短开发时间,程序的可靠性大大提高。

3 总结

按照本系统所制造的产品已经通过实际测试,其基波幅值误差小于0.2%,谐波幅值误差小于5%,相位误差小于0.2%,其精度满足GB/T 17626.7规定的A级测量仪器精度要求。该产品成本低廉,结构紧凑,抗干扰性强。实际应用中,用户可按实际需求在变电站二次侧任意设置谐波监测点,并可通过局域网或RS485接口方便地接入变电站管理系统中,从而有效实现对线路谐波的监测。

电子发烧友App

电子发烧友App

评论