摘要: 在反辐射导弹的雷达导引头中,信号跟踪器的实时性是影响系统性能的重要因素之一。介绍了利用高性能FPGA丰富的资源实现的多路脉冲重复频率跟踪器,它解决了在密集信号环境下信号跟踪的实时性问题,减小了系统体积。经过实验验证,其各项指标均达到了设计要求。

关键词: 反辐射导弹 信号跟踪 现场可编程门阵列

随着高科技的迅速发展,现代战争已经不仅是传统意义战场上的较量,电子战已经成为决定战争胜负的重要因素之一。反辐射导弹在电子战中扮演着重要的角色,它在战争中可以有效地压制或摧毁敌方武器系统中的雷达,使敌方武器系统失去攻击能力,取得制空权,发挥己方的空中优势。在反辐射导弹中引导攻击目标的是雷达导引头,它截获目标雷达的信号并检测出信号入射角,输送给导弹控制系统,导引导弹跟踪目标直到命中。

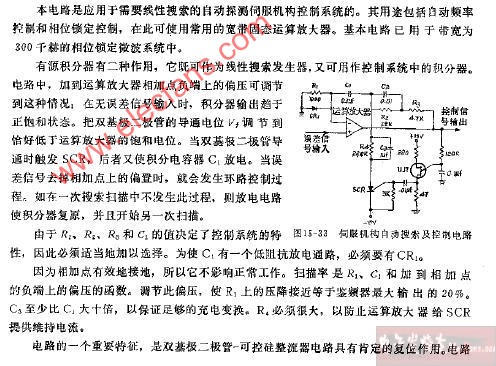

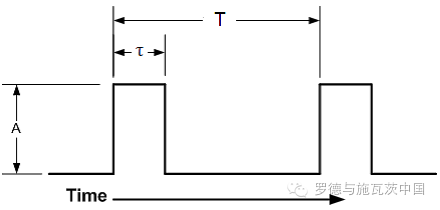

脉冲重复频率(PRF)跟踪器是雷达导引头的重要器件,它的功能是在雷达导引头接收到的信号流中选择出目标信号。在日趋复杂的电磁环境下,空间信号密度已经达到50~100万脉冲/秒,至少相当于几百个辐射源的总和。所以信号接收机截获到的信号通常是不止一部雷达的信号,往往包括很多部。脉冲重复频率跟踪器就是要在包含多部雷达的信号流中选出要截获的那部雷达信号,送到后面的信号处理机。如图1所示,接收机收到的信号包括多部信号,经过脉冲重复频率跟踪器的选择后只输出一部信号送到后续的信号处理机。 目前,实现脉冲重复频率跟踪器的方法主要有三种:纯软方式、半软半硬方式和纯硬方式。纯软方式用高速DSP完成全部功能,这种方式在现代密集信号环境下将影响系统的实时性,要想实现多路信号的跟踪需要多个DSP,这将造成系统体积庞大。半软半硬方式用DSP和硬件电路分别完成一部分功能,和前一种方式有相同的缺点。纯硬方式用FPGA或CPLD实现跟踪信号的全部功能,具有实时性好、性能稳定的优点,能满足目前复杂电磁环境的要求,并且集成度高,可以实现系统的小型化。

本文利用FPGA资源丰富、易于编程的特点设计了纯硬方式的脉冲重复频率跟踪器,实现了在密集信号环境下的信号跟踪,并且将多路并行的跟踪器集成在一片FPGA中,简化了系统结构,缩小了体积。

1 脉冲重复频率(PRF)跟踪器原理

1.1 脉冲重复频率跟踪器

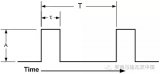

为了在密集的信号流中分离出一部信号,需要知道该信号的脉冲重复频率以及脉冲重复周期(PRI)类型,这部分工作通常由雷达侦察系统或反辐射导弹的信号预处理器来完成。脉冲重复频率是识别雷达的一个重要参数,因为它是雷达最具特征的信号参数。所说的最具特征,是指雷达的性能受其所使用的脉冲重复频率的影响很大,例如对于常规雷达来说,脉冲重复频率的数值决定了雷达的最大无模糊距离和最大无模糊径向速度。脉冲重复周期(PRI)是脉冲重复频率的倒数,其类型大致可分为三种:固定、跳变和参差。固定PRI信号的各个脉冲之间的间隔是恒定的;如果把信号的PRI加上人为的随机跳变就构成了跳变PRI信号,其PRI的变化值可达脉冲重复周期平均值的15%;参差PRI信号由多个间隔不同的脉冲组成一个信号序列帧,各脉冲重复周期的总和称为帧周期,帧周期之间的小间隔称为小周期,一般帧周期是固定的。

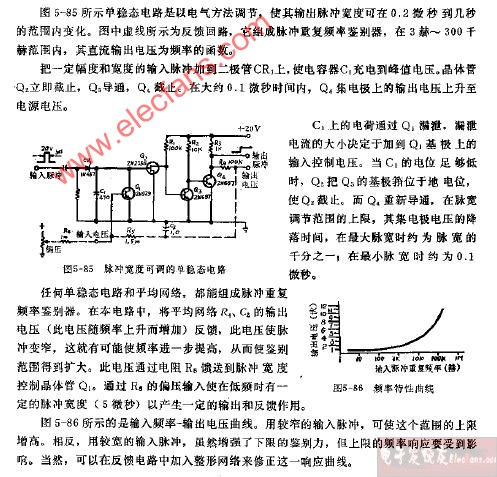

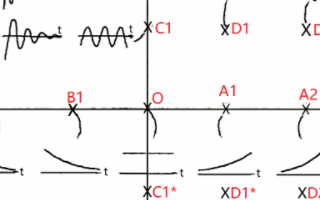

根据以上分析,为了实现各种PRI类型信号的实时跟踪,在FPGA中设计了脉冲重复频率跟踪器电路,其原理图如图2所示。

由图2可见,跟踪器包括重复周期寄存器0~7、参差寄存器、输出波门寄存器以及重复周期计数器、输出波门计数器、输出控制器等单元。其中,参差寄存器存储参差PRI信号的小周期数,即参差数;重复周期寄存器0~7存储信号的各个重复周期。由于目前参差雷达一般不超过8参差数,所以重复周期寄存器有8个即可,参差寄存器储存的参差数控制各个重复周期寄存器。例如参差数等于3,则只有0~2号重复周期寄存器有效,其余5个无用。若参差数等于1,则只有0号重复周期寄存器有效,这相当于固定PRI信号的情况。输出波门寄存器存储的是波门宽度,其值主要由跳变PRI信号的变化量决定。若变化量大,则输出波门宽度也要大,这样才能选中要截获的信号。数值关系可表示为:波门宽度=PRI变化量+脉冲宽度+常量A。常量A为调整参数,可根据调试情况决定。重复周期计数器是跟踪器的核心器件,它根据信号脉冲的到达与否决定何时开始计数,计数周期是重复周期寄存器中的值,各个有效的重复周期寄存器的存储值循环采用。其输出送到输出波门计数器,后者根据输出波门寄存器中的值确定波门的宽度。输出控制器是主要的逻辑控制单元,控制整个跟踪器的工作。输出控制器的功能还包括判断信号是否截获成功、信号是否丢失等。

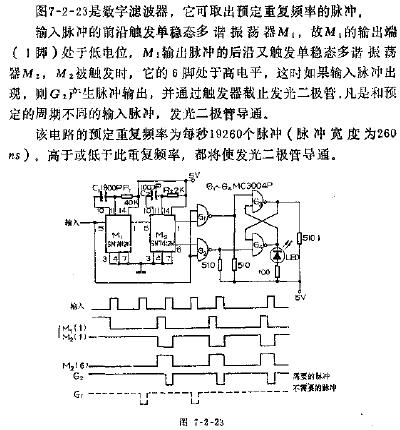

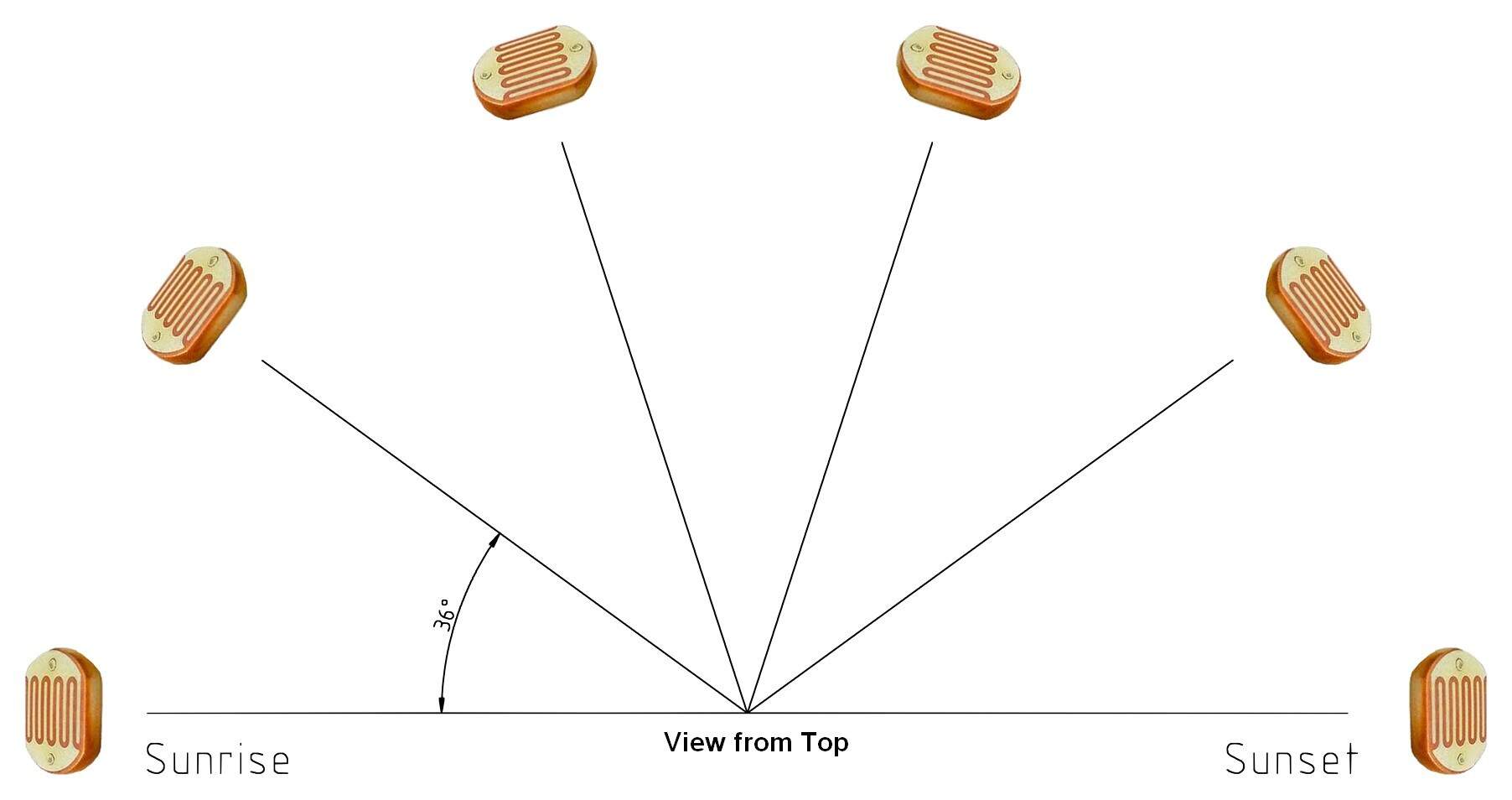

1.2 信号滤波器

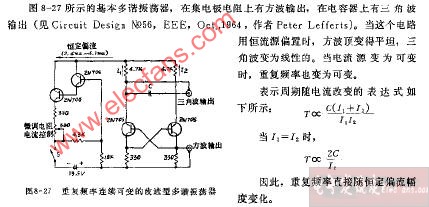

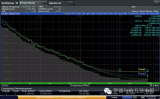

各种电子对抗设备数目的急剧增加使雷达导引头系统处于高度密集的信号环境中,脉冲重复频率跟踪器的实时性受到考验。基于以上考虑,在跟踪器的前端设计了信号滤波器,对信号脉冲流进行稀释,减轻跟踪器的压力。信号滤波器的原理图如图3所示。

信号滤波器的核心是关联比较器,FPGA为关联比较器的实现提供了便利条件。本系统中采用了两路关联比较器,一路用于信号载频滤波,一路用于信号脉宽滤波。由图3可见,只有载频和脉宽都在一定的范围之内的信号才能通过滤波器,即对信号进行了筛选。在现代复杂电磁环境下,载频和脉宽都比较接近的信号是相当多的,同时比较器的上、下限不能取得过于接近,这样滤波器的输出就不只限于一部信号,即使这样也极大地稀释了信号流。这种稀释过的信号流送到跟踪器,有助于提高跟踪器的实时性,更利于成功地截获信号。

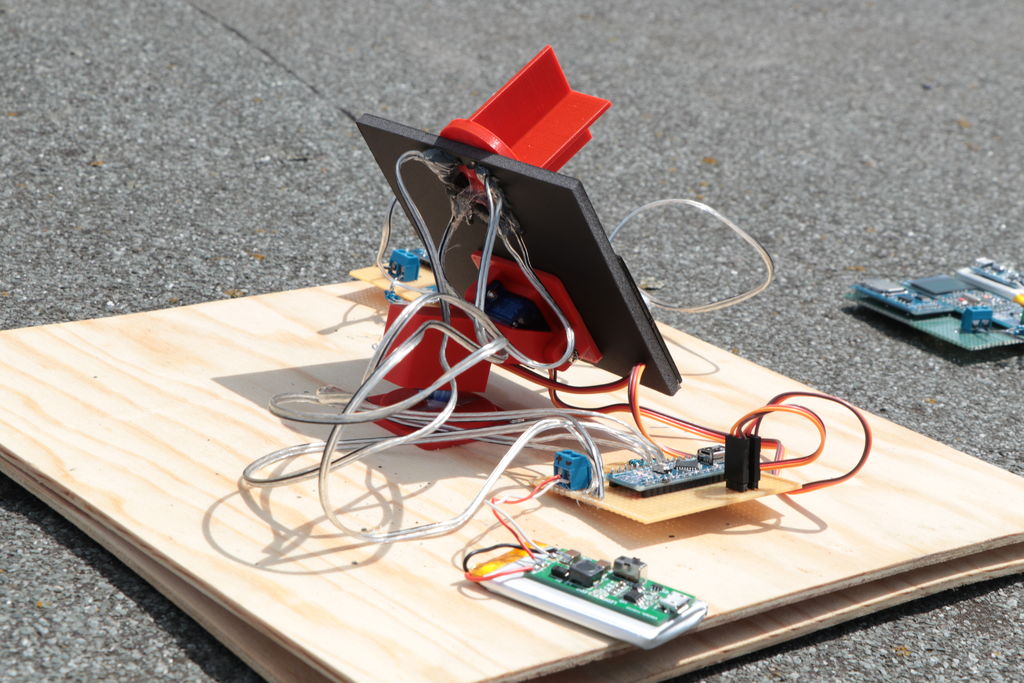

2 系统实现

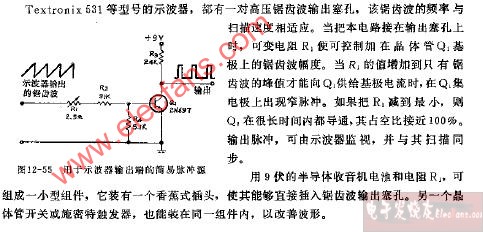

系统框图如图4所示,整个系统由DSP和FPGA组成,在 FPGA中设计了8路跟踪器,最多可同时对8路信号进行跟踪。DSP负责控制各路跟踪器的工作,包括对各路跟踪器装载参数和使能,同时通过HPI(上位机接口)与弹上主控计算机传递数据。

由于各路跟踪器都是采用纯硬件方式实现的,所以占用的DSP处理时间很少,DSP只需将主控计算机传递的信号参数装载到跟踪器中,并发出启动命令即可,余下的工作由跟踪器自动完成,无需DSP干预,使DSP有大量的时间执行其它计算任务。

2.1 FPGA器件选择

本设计采用Altera公司的APEX系列EP20K200EQI芯片。APEX系列FPGA是Altera公司的高端产品,是工业界第一块整合了SOPC(system-on-a-programmable

-chip)集成电路的可编程逻辑器件。其集成度高,最多能提供250万个门电路、5万个逻辑单元,并且在不减少逻辑单元的情况下可提供44万位RAM。低功耗设计,采用双电压体系,核心电压1.8V,I/O电压3.3V,与多种接口标准兼容。

EP20K200EQI芯片属于工业级芯片,采用240针PQFP封装,用户I/O管脚数为168个,提供8320个逻辑单元,芯片面积却仅为34.5mm×34.5mm。本设计中每路跟踪器占用的逻辑单元为7%,8路跟踪器外加一些辅助电路总共占用的逻辑单元为60%,芯片资源尚有剩余,为将来系统功能改进留了余地。

2.2 FPGA芯片的配置

APEX系列FPGA芯片是基于SRAM技术的器件,由于SRAM的易失性,掉电以后芯片中的配置信息将丢失,所以每次系统上电时都要重新加载配置数据。Altera公司提供了一系列的配置器件用于储存配置数据并且在上电时加载FPGA。本设计选用Altera公司的EPC2,最大的优势在于EPC2是FLASH器件,可以多次重复编程,改掉了以前的PROM配置器件只能写入一次的缺点,极大地方便了系统调试和产品升级。当设计完成的产品需要改进时,只需将EPC2中的内容重写一遍即可,缩短了产品的研发周期。

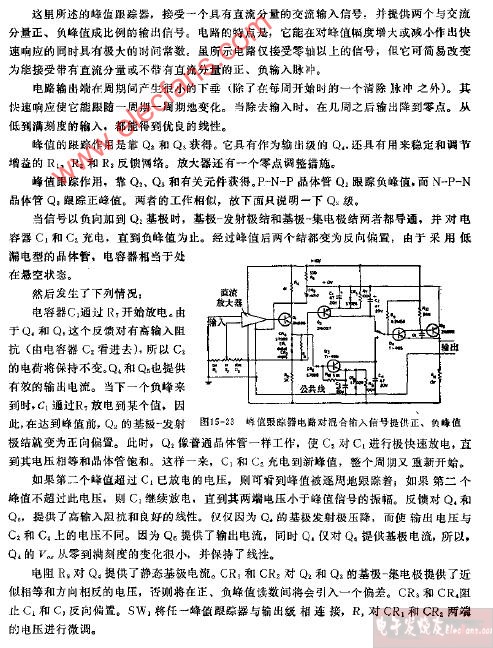

在设计中需要注意的是EPC2的容量是1.6Mb,根据FPGA芯片的容量大小需要的配置芯片的数目是不等的。本设计中采用的EP20K200EQI芯片的容量是1.9Mb,所以需要两片EPC2。图5是用两片EPC2配置EP20K200EQI芯片的连线图,通过EPC2芯片的nCASC管脚,可以方便地实现多片级联。系统上电后, EP20K200EQI芯片检测到nCONFIG管脚电平由低到高的跳变时,启动配置流程。首先EP20K200EQI芯片驱动CONF_DONE管脚为低,将第一片EPC2的nCS管脚拉低,选通该芯片。经过一段延时以后EP20K200EQI芯片释放nSTATUS管脚,上拉电阻将EPC2的OE管脚拉成高电平将其使能。EPC2用其内部振荡器将配置数据串行输出到FPGA芯片中。当第一片EPC2的全部数据输出完后,它驱动nCASC管脚为低,按顺序驱动第二个EPC2的nCS为低,启动第二个EPC2输出数据。前一个EPC2启动下一个EPC2的过程在一个时钟周期内就可以完成,所以输送给FPGA芯片的数据流是连续的。

2.3 FPGA芯片的在线编程

APEX系列FPGA芯片在边界扫描模式(JTAG模式)下可以对其进行在线的配置重构,系统无需重新上电就可以修改FPGA芯片的配置,极大地方便了调试。JTAG模式也可以对EPC2进行在线编程。在系统设计时,可以把多个器件组成一个JTAG器件链,用一个JTAG兼容头(例如Altera的ByteBlasterMV并口下载电缆)把所有的器件连接起来。JTAG器件链方式特别适合电路板上有多个器件的情况,用一个JTAG头就可以对多个器件进行在线编程。本设计中电路板上有三个JTAG器件,包括两片EPC2和一片FPGA,设计的JTAG器件链如图6所示。

图5 EPC2配置FPGA

在JTAG器件链中,两个EPC2是第一和第二个器件,FPGA是第三个器件,JTAG按顺序对器件编程。当对FPGA编程时,通过软件将两个EPC2设置成BYPASS模式,编程数据从EPC2的TDI管脚直接输出到TDO管脚直达FPGA芯片,实现了对FPGA芯片的在线编程。采用这种JTAG器件链方式,方便了系统调试,缩短了产品的开发周期。

3 FPGA应用系统设计中应注意的问题

为了提高FPGA应用系统的抗干扰性能,应尽量采用多层印刷电路板,并有完整的GND层和电源层,从而提供几乎无限的电流吸收能力,起到防止噪声和为逻辑信号提供屏蔽的作用。由于APEX EP20KE系列FPGA采用双电压体系,最好采用两个电源层,一个作为核心电源层,一个作为I/O电源层。本设计采用了八层电路板工艺,其中有两个GND层、一个核心电压层、一个I/O电压层以及四个信号层,在实际调试中抗干扰性能明显强于以前的双面板系统。如果在实际应用中对价格敏感,也可采用四层板工艺,其中应有一个完整的GND层,一个分割的电源层。

FPGA器件的每一个电源和GND引脚都应当直接连接到电源和GND平面上,每一对电源和GND引脚都应当接上一个电源去耦电容器,而且尽可能靠近FPGA器件。对于PQFP封装的器件,应当把去耦电容器集中在器件正下方电路板焊接面上,这样既达到了靠近器件的目的,又可以减少电路板的面积。

在电源线进入电路板的地方一般都放置一个100μF的大容量电容器,以稳定电源电压,但是这个电容器有时也会成为导致FPGA器件配置失败的隐患。Altera器件在上电初始化时,首先实行一个POR(上电复位)延迟以等待电源稳定。如果电源电压上升时间较长,超过了POR延迟时间,可能造成器件初始化不正确,导致功能失效。当用EPC2配置APEX EP20KE系列FPGA时,POR延迟最大为200ms,所以电源电压上升时间不能超过这个时间。如果出现系统上电时FPGA器件配置失败的情况,应当考虑是否由于大容量电容器致使电源电压上升太慢,这时可以更换一个小容量的电容器。尤其是在单块电路板上调试成功,而多块电路板连在一起调试时出现这种情况更应考虑这个原因。因为多块电路板连在一起时电源滤波电容是并联的,此时容量相加导致更大容量的电容出现在电源入口处,致使电压上升过慢。本系统在调试时就曾遇见这种情况,将电源滤波电容从100μF调整为22μF便解决了问题。

图6 JTAG器件链

为了提高电路设计效率,应尽量多采用LPM宏单元库。LPM是参数化的模块库,是优秀的版图设计人员和软件人员智慧的结晶。LPM包括了常用的逻辑单元,通过修改LPM的某些参数,就能迅速设计出自己的电路。Altera公司提供的LPM宏单元库是Altera系列FPGA器件的绝佳组合,可以实现绝大部分的设计功能,并能提供较高的运行速度和较低的资源占用率。在设计中发现,多采用LPM宏单元库的电路与不采用LPM宏单元库的电路相比,资源占用率可减少10%~30%,可见节省的芯片资源是很可观的。

本设计利用FPGA设计灵活、易于编程和容量大的特点实现了多路脉冲重复频率跟踪器,解决了在密集信号环境下跟踪系统的实时性问题,将八路跟踪器设计在一片Altera公司的APEX EP20K200EQI FPGA芯片中,缩小了电路体积,满足了系统小型化的要求。实验证明用高性能FPGA实现多路脉冲跟踪系统是完全可行的。

电子发烧友App

电子发烧友App

评论