cpld的输入电源电路

- cpld(168088)

相关推荐

基于CPLD技术的MOSFET器件保护电路的设计方案

介绍了一种基于CPLD技术的MOSFET器件保护电路的设计与实现。该电路设计方案具有抗干扰能力强、响应速度快和通用性好的优点。通过试验验证了该方案的正确性和可行性。##在功率MOSFET保护电路输入

2014-04-25 11:15:47 1939

1939

1939

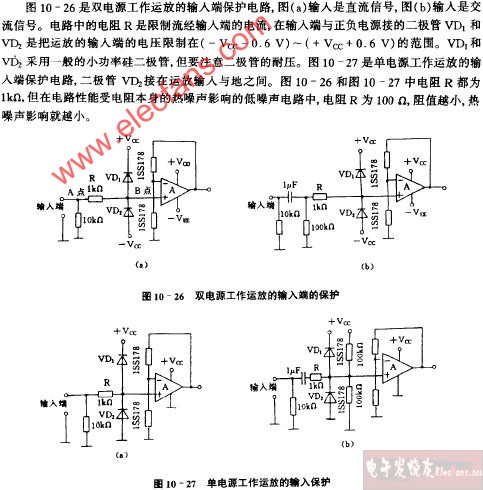

1939开关电源的电路组成、输入电路的原理及常见电路

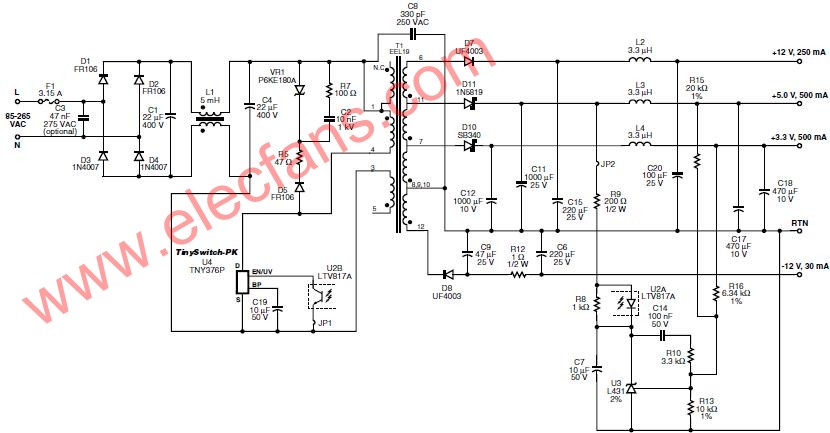

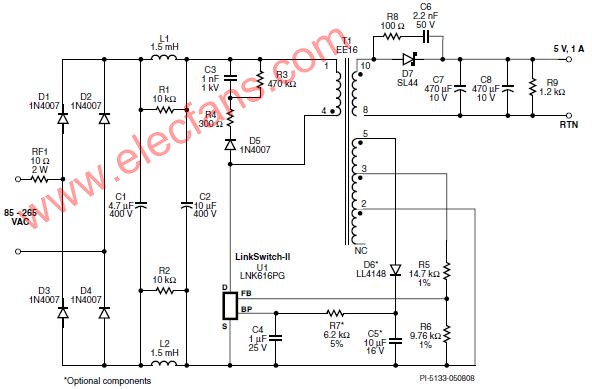

开关电源的主要电路是由输入电磁干扰滤波器(EMI)、整流滤波电路、功率变换电路、PWM控制器电路、输出整流滤波电路组成。辅助电路有输入过欠压保护电路、输出过欠压保护电路、输出过流保护电路、输出短路保护电路等。

2022-10-08 11:30:25 2044

2044

2044

2044CPLD加51单片机让系统更高效

。 最容易的电路设计方法不外乎是直接绘制电路原理图。采用原理图输入,初学者甚至不需要额外学习就可以从事CPLD 设计。我们只需要在软件平台上从集成器件库调出对应的器件,绘制相同的电路原理图即可,实现

2012-01-17 16:48:45

CPLD咨询

有没有哪位大侠搞过CPLD,我咨询个问题,有个带LCD彩色显示的板子,基本电路情况是这样的,由于当初设计的局限性,使用的32位单片机引脚不够用,没有使用单片机直接和LCD相连接,而是把单片机

2016-12-23 18:51:28

cpld大神看过来。。。。。

构建一个激光靶对目标位置的编码识别电路,就是将激光接收器的接收到的电信号输入到cpld中,通过程序来识别出电信号的0和1代码,求问怎么搭建cpld电路和编程识别0和1代码。谢谢啦

2016-04-25 10:35:03

电源输入的防护电路

一般的产品用的都是直流电源,像手持产品多是5V电源,一些小设备也是5V,大一些的设备12V的稍多一些,车载电子产品有12V和24V两种电源。 这些电源输入的防护电路主要包括过压保护,过流保护,防反

2021-11-17 08:27:52

FPGA CPLFPGA CPLD 数字电路设计经验分享

FPGA CPLFPGA CPLD 数字电路设计经验分享FPGA/CPLD数字电路设计经验分享摘要:在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应

2012-08-11 10:17:18

FPGA与CPLD的区别

地说,FPGA就是将CPLD的电路规模,功能,性能等方面强化之后的产物。

一般而言,CPLD与FPGA之间的区别的如下所示(当然也有例外)。

PLD : Programmable Logic

2011-09-27 09:49:48

FPGA与CPLD的概念及基本使用和区别

/O单元互连结构,可由用户根据需要生成特定的电路结构,完成一定的功能.由于 CPLD内部采用固定长度的金属线进行各逻辑块的互连,所以设计的逻辑电路具有时间可预测性,避免了分段式互连结构时序不完全预测

2020-08-28 15:41:47

USB -CPLD开发板使用攻略

LDO:ASM1117-3.3 有源时钟:50MHZ 全钽电容电源滤波 本电路板适合人群: 1. 学习USB2.0通信技术的开发者 2. 学习CPLD 学习开发者 3. 高速数据采集开发应用者 4.8051 单片机学习者

2012-08-15 14:44:47

xilinx XA2C128 CPLD其他通用IO是否可以用作CPLD的时钟输入?

/置位,GCK =全局时钟,CDRST =时钟分频复位等。我的问题是 - 1)我知道GSR,GCK,GTS引脚可以用作通用IO。但我想知道其他通用IO是否可以用作CPLD的时钟输入?或者是否存在一些限制

2019-04-12 06:09:36

供电电源对CPLD的输出波形影响

本人自己设计了一个3.3V的直流电源,给CPLD供电会出现输出波形杂乱的现象,但是使用外接移动电源输出波形就会正常,设计的电路图和输出的波形图如图。想问一下供电电源对芯片输出的影响,是否有大神遇到类似的情况。

2018-01-09 09:43:20

基于CPLD的数据采集与显示接口电路仿真设计

/模转换器DAC0832构成一个数据采集系统,并用CPLD/FPGA实现数据采样、D/A转换输出、有关数据显示的控制,单片机完成对A/D转换数据运算。电路如图1所示。系统功能如下:系统按一定速率采集输入

2018-12-10 10:18:34

基于CPLD的时栅位移传感器应用

作者:陈春生基于CPLD的数字信号处理电路 智能时栅位移传感器内部基于CPLD的数字信号处理电路。电路采用双MCU+CPLD结构设计,内部嵌入主从式两块单片机,副MCU负责数据采集与预处理工作,主

2019-07-17 07:01:38

基于CPLD节省电池能量的系统断电电路设计

的应用逻辑以外(图中未画),CPLD的电源控制逻辑增加了一对标准参数的库宏电路,它由Altera的Quartus II开发工具生成。内部的4.4MHz±25%振荡器Altufm_osc驱动一个模块化44

2018-09-26 17:29:24

如何利用CPLD器件设计单稳态电路?

随着电子技术特别是数字集成电路技术的迅猛发展,市面上出现了FPGA、CPLD等大规模数字集成电路,并且其工作速度和产品质量不断提高。利用大规模数字集成电路实现常规的单稳态集成电路所实现的功能,容易

2019-08-16 06:12:46

如何将LPC2114连接到CPLD再连接到其它电路呢?

现在数字电路除 LPC2114 使用 3.3V 电压外,其余的大部分是 5V 的.我想先将 LPC2114连接到 cpld,再连接到其它电路(CPLD 的 I/O 口可以输出或输入 5V)不知道行不行。谢谢

2023-02-27 10:00:18

怎么利用FPGA和CPLD数字逻辑实现ADC?

数字系统的设计人员擅长在其印制电路板上用FPGA和CPLD将各种处理器、存储器和标准的功能元件粘合在一起来实现数字设计。除了这些数字功能之外,FPGA和CPLD还可以使用LVDS输入、简单的电阻电容(RC)电路和一些FPGA或CPLD的数字逻辑单元实现共模功能,从而构建模数转换器(ADC)。

2019-08-19 06:15:33

请问如何使用CPLD和STM32单片机设计一个具有12路信号输入接口的板卡?

最近有一个小题目:使用CPLD和STM32单片机设计一个具有12路信号输入接口的板卡(每一个接口都是独立的,具有自己的固定地址),当随机接入1~4路方波信号时,CPLD可以快速判断是12路接口

2018-06-27 15:24:06

运放输入端浮空的问题

CPLD的输入。怀疑是哪里短路了,就开始测试电压和各种关联信号,没有发现问题。那就继续向前找,2410的输入是一个运放芯片(双电源供电+-15V),用万用表测试,当时惊呆了,在没有接输入的情况下,运放居然

2016-03-04 21:15:17

CPLD在多路高速同步数据采集系统中的应用

采用VHDL 语言设计,用CPLD 控制模/ 数转换电路, 完成多路模拟输入的高速同步数/ 模转换,具有容错和自检能力。CPLD 与处理器之间采用并行接口,具有很好的移植性、可靠性。

2009-04-16 10:44:25 7

7

7

7CPLD 在多路高速同步数据采集系统中的应用

采用VHDL 语言设计,用CPLD 控制模/ 数转换电路, 完成多路模拟输入的高速同步数/ 模转换,具有容错和自检能力。CPLD 与处理器之间采用并行接口,具有很好的移植性、可靠性。

2009-05-15 13:10:35 18

18

18

18基于ARM9 和CPLD 的输入输出系统设计

介绍了一种基于ARM9 和CPLD 架构的嵌入式输入输出系统的软硬件设计。系统以工业级EP9315 为核心,扩展了LCD、触摸屏、以太网、串口和USB 等控制接口;以MAX2_EPM240为核心,进行了

2009-06-01 10:55:12 21

21

21

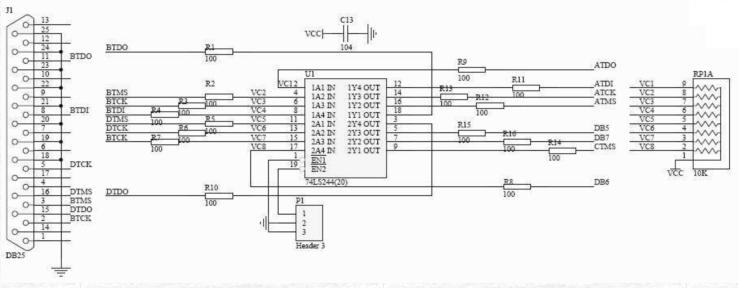

21基于CPLD的计算机接口电路设计技巧

本文介绍了利用计算机ISA、PCI总线和打印机接口设计密码电路。基于CPLD设计密码电路,具有加密性能好的特性。通过并行打印机接 口设计一个密码电路,密码存储在电路中,通过操

2009-06-12 15:00:58 28

28

28

28基于CPLD的计数及LED译码电路

本文采用VHDL语言设计了基于CPLD的计数及LED译码电路,该设计方法符合电子系统设计的发展方向。关键词:计数器;LED译码;CPLD;VHDL在各种检测与控制系统及仪表中,对发生的事

2009-08-24 08:32:39 28

28

28

28基于ARM9和CPLD的输入输出系统设计

介绍了一种基于ARM9 和CPLD 架构的嵌入式输入输出系统的软硬件设计。系统以工业级EP9315 为核心,扩展了LCD、触摸屏、以太网、串口和USB 等控制接口;以MAX2_EPM240为核心,进行了

2009-12-22 11:33:23 30

30

30

30嵌入式CPU外围接口电路的CPLD实现

摘要:介绍了一种采用CPLD实现嵌入式CPU外围电路的方法,将数据总线、译码单元、分频电路及逻辑电路集成于一片CPLD,大大缩小了印制板的面积并提高了系统可靠性,同时,由于CPLD

2010-05-10 09:23:49 29

29

29

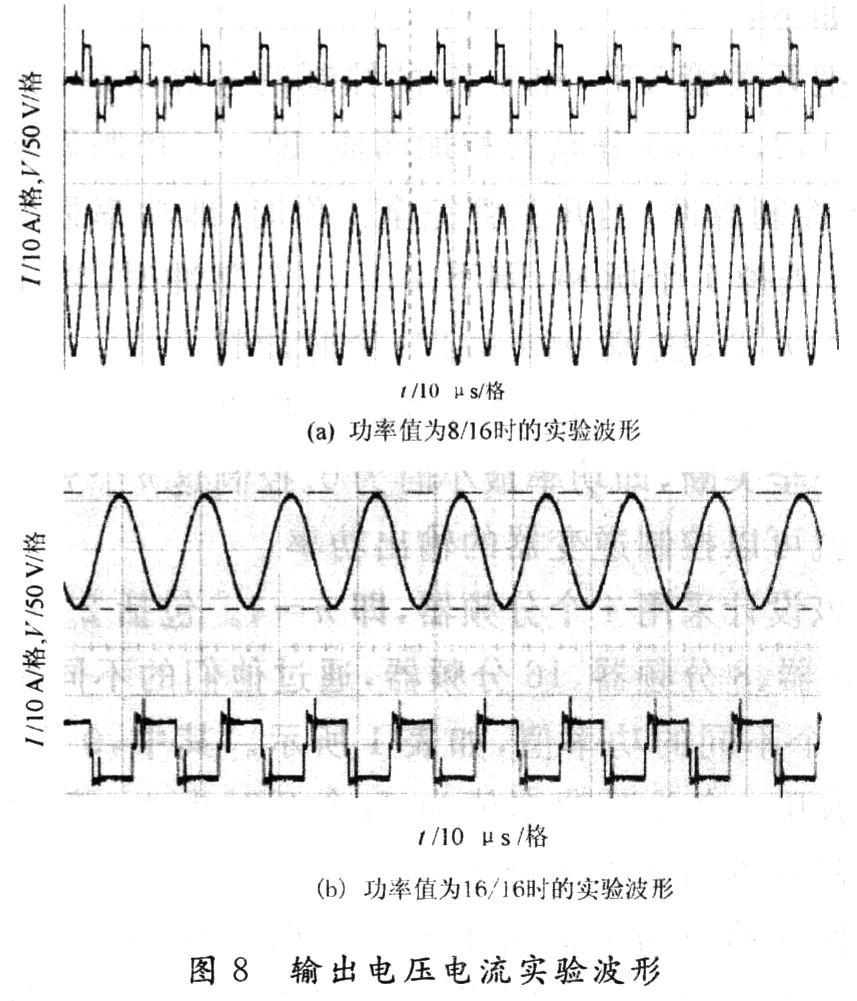

29基于CPLD的数字触发电路的设计

摘要:利用大规模可编程控制器(Complex Programmable Logic Device)CPLD.针对静止补偿器(STATCOM)对触发脉冲信号的要求.设计一种基于CPLD的正弦脉宽调制(SPwM)数字触发电路。正弦调制波的产

2010-05-14 09:33:55 21

21

21

21CPLD器件的配置与编程下载

当利用CPLD/FPGA开发系统完成数字电路或系统的开发设计并仿真校验通过之后,就需要将获得的CPLD/FPGA编程配置数据下载到CPLD/FPGA芯片中,以便最后获得所设计的硬件数字电路或系

2010-06-01 10:14:46 23

23

23

23ADS8323与高速FIFO接口电路的CPLD实现

以CPLD为逻辑控制核心实现了ADS8323与高速FIFO的接口电路,该电路具有可靠性高、通用性强、易于移植等特点。在设计过程中,以QuartusII作为开发环境,采用图形输入和Verilog HDL语言输

2010-08-06 14:25:53 22

22

22

22换体DMA高速数据采集电路的CPLD实现

换体DMA高速数据采集电路的CPLD实现

介绍了换体DMA高速数据采集电路原理及其CPLD实现。用CPLD设计双端口RAM缓存、控制译码、时序逻辑电路,很好地解决了电路元件所占体积

2009-03-28 15:09:18 666

666

666

666

什么是CPLD?CPLD是什么意思?

什么是CPLD

CPLD(Complex Programmable Logic Device)是Complex PLD的简称,一种较PLD为复杂的逻辑元件。CPLD是一种用户根据各自

2009-03-30 13:40:43 3143

3143

3143

3143VHDL语言在FPGA/CPLD开发中的应用?

【摘 要】 通过设计实例详细介绍了用VHDL(VHSIC Hardware DescriptionLanguage)语言开发FPGA/CPLD的方法,以及与电路图输入和其它HDL语言相比,使用VHDL语言的优越性。

2009-05-10 19:47:30 1111

1111

1111

1111

基于CPLD技术的看门狗电路的设计

【摘 要】 介绍了一种基于CPLD器件设计看门狗电路的方法。 关键词:CPLD,看门狗,计数器

1 引 言 随着现代电子技

2009-05-16 19:18:28 700

700

700

700

换体DMA高速数据采集电路原理及其CPLD实现

摘要:介绍了换体DMA高速数据采集电路原理及其CPLD实现。用CPLD设计双端口RAM缓存、控制译码、时序逻辑电路,很好地解决了电路元件所占体积大、电路复杂、不能实现在线

2009-06-20 15:12:07 878

878

878

878

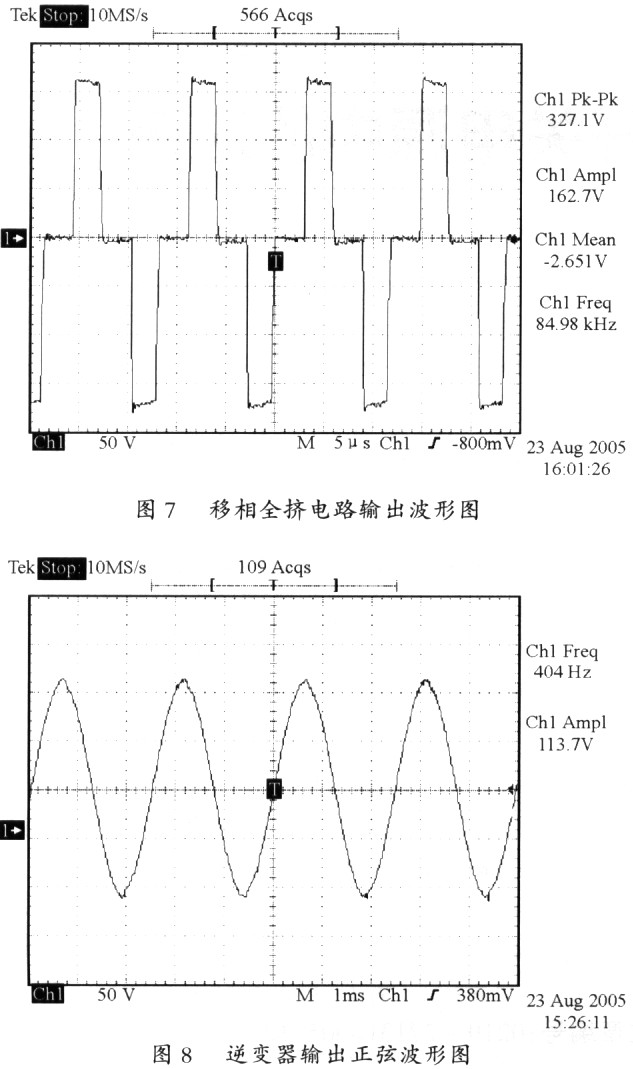

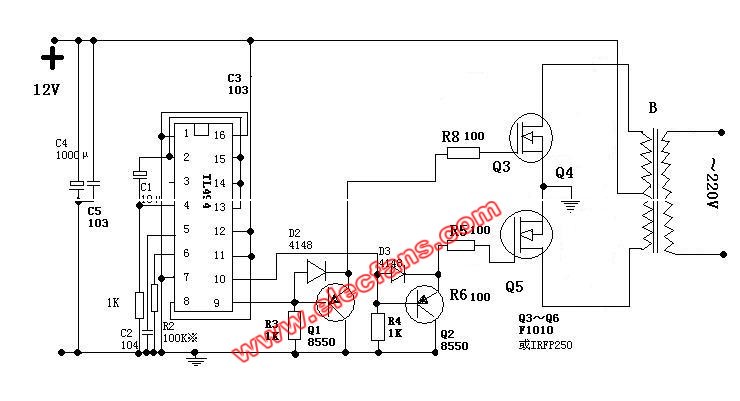

CPLD在航空15V/400Hz高频链逆变电源中的应用

CPLD在航空15V/400Hz高频链逆变电源中的应用介绍了一种基于CPLD的,用于大功率航空逆变电源的,触发电路的设计原理和设计方法。实

2009-10-09 09:29:48 826

826

826

826

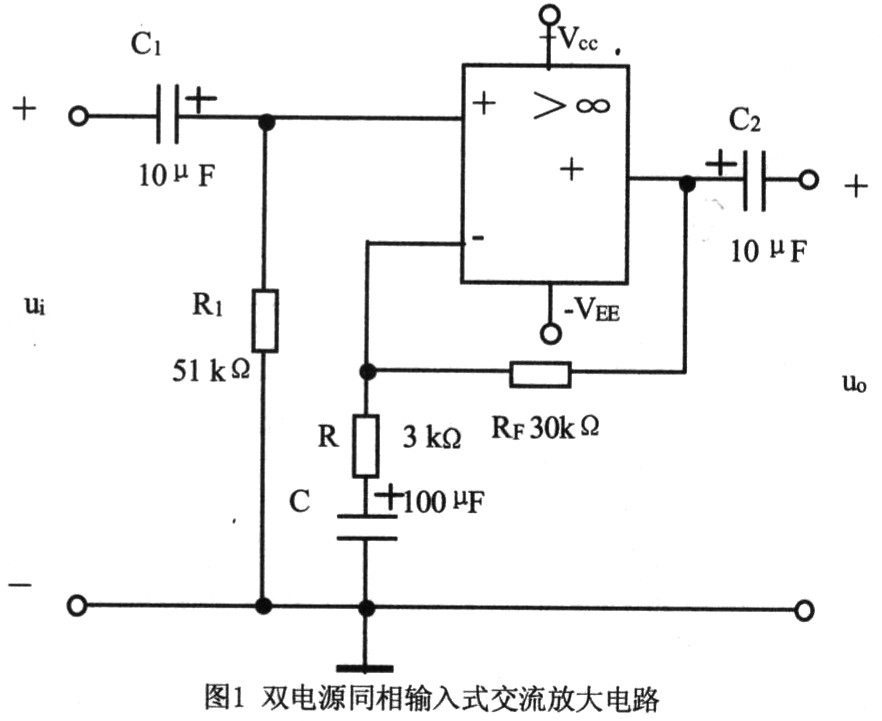

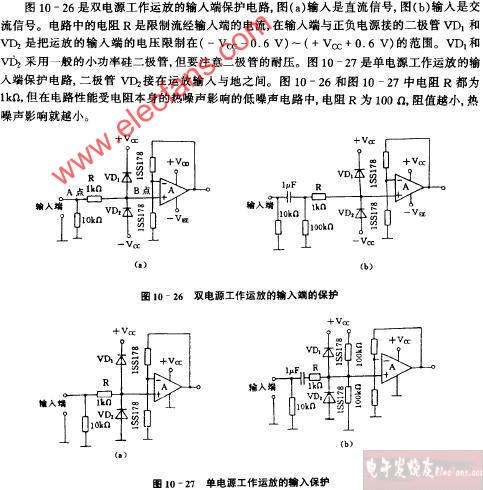

双电源同相输入式交流放大电路

双电源同相输入式交流放大电路

图1是使用双电源的同相输入式交流放大电路。两组电源电压VCC和VEE相等。C1和C2为输入和输出耦合电容;R1使运放同相输入端

2009-10-25 10:42:03 4718

4718

4718

4718

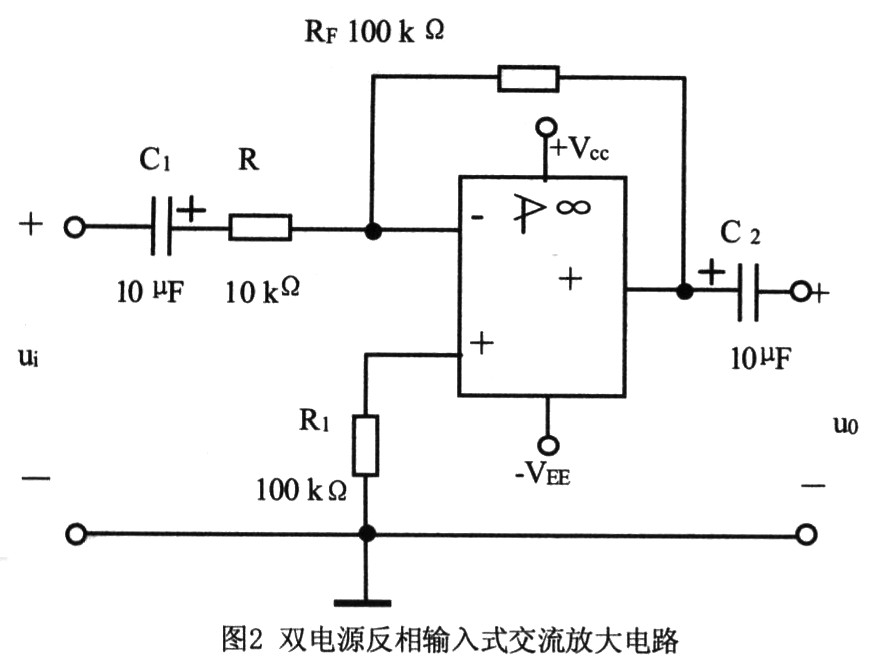

双电源反相输入式交流放大电路

双电源反相输入式交流放大电路

图2是使用双电源的反相输入式交流放大电路。两组电源电压VCC和VEE相等。RF引入直流和交流负反馈,C1隔直流,使直流形成全反馈

2009-10-25 10:42:32 2829

2829

2829

2829

CPLD逻辑电路

CPLD逻辑电路 图6是CPLD内部逻辑电路,CPLD选用的是LATTICE公司的ispLSI1016E,逻辑设计采用原理图输入法,主要功能是对MUX的通道进行选择、对A/D转换器进

2009-11-13 12:04:13 2502

2502

2502

2502

基于CPLD的脉冲密度功率调节高频逆变电源

基于CPLD的脉冲密度功率调节高频逆变电源

0 引 言 目前,高频感应加热电源的输出功率调整主要是通过改变逆变器的输出频率或改变逆变器的输入直流

2009-11-18 16:20:02 1271

1271

1271

1271

采用CPLD的光伏逆变器锁相及保护电路设计

采用CPLD的光伏逆变器锁相及保护电路设计

0 引言

在光伏并网系统的逆变器电路中,对电网电压的锁相是一项关键技术。由于电力系统在

2010-03-03 10:53:16 1573

1573

1573

1573

基于CPLD器件设计的单稳态电路

随着电子技术特别是数字集成电路技术的迅猛发展,市面上出现了FPGA、CPLD等大规模数字集成电路,并且其工作速度和产品质量不断提高。利用大规模数字集成电路实现常规的

2010-07-16 11:06:27 1698

1698

1698

1698

基于MAX7000系列CPLD的数据采集系统

CPLD是复杂的PLD,专指那些集成规模大于1000门以上的可编程逻辑器件。它由与阵列、或阵列、输入缓冲电路、输出宏单元组成,具有门电路集成度高、可配置为多种输入输出形式、多

2010-10-21 10:15:43 3038

3038

3038

3038

CPLD实现线阵CCD驱动电路

采用MAXⅡ器件的EPM240T100C5N为控制核心,以TCD1500C为例,设计了基于CPLD的线阵CCD驱动电路,完成了硬件电路的原理图的设计,并实现了软件调试。通过QuartusⅡ软件平台,对其进行了模拟仿真。实

2011-11-03 15:24:40 129

129

129

129基于CPLD器件的单稳态脉冲展电路

具体介绍了基于CPLD 器件设计单稳态窄脉冲展宽电路的详细过程和这种单稳态窄脉冲展电路的特点,给出了相应的时序仿真波形,提出了提高展宽脉冲宽度精确度的方法。

2011-12-17 00:23:00 35

35

35

35DC 输入滤波电路原理图

DC 输入滤波电路原理图如下所示: ① 输入滤波电路:C1、L1、C2组成的双型滤波网络主要是对输入电源的电磁噪声及杂波信号进行抑制,防止对电源干扰,同时也防止电源本身产生的高频

2012-05-31 10:37:22 9224

9224

9224

9224

输入过欠压保护电路原理图

输入过欠压保护电路原理图如下所示: 1、 原理图: 2、 工作原理: AC输入和DC输入的开关电源的输入过欠压保护原理大致相同。保护电路的取样电压均来自输入滤波后的电压。 取样电

2012-05-31 11:16:15 20964

20964

20964

20964

FPGA和CPLD的区别及其用途介绍

FPGA/CPLD能完成任何数字器件的功能,上至高性能CPU,下至简单的74电路,都可以用FPGA/CPLD来实现。 FPGA/CPLD如同一张白纸或是一堆积木,工程师可以通过传统的原理图输入

2017-10-09 09:52:20 14

14

14

14基于CPLD的振荡器实现设计应用

CPLD内部施密特触发器电器特性见表1。目前大部分使用的CPLD都需要两个电源VCC和VCCIO,VCC就是CPLD内部的核电压,VCCIO是CPLD所有I/O 引脚电压。

2018-05-11 08:22:00 1256

1256

1256

1256

基于fpga和cpld低频/最小逻辑ADC实现

数字系统的设计人员擅长在其印制电路板上用FPGA和CPLD将各种处理器、存储器和标准的功能元件粘合在一起来实现数字设计。除了这些数字功能之外,FPGA和CPLD还可以使用LVDS输入、简单的电阻电容(RC)电路和一些FPGA或CPLD的数字逻辑单元实现共模功能,从而构建模数转换器(ADC)。

2018-04-26 11:53:00 1121

1121

1121

1121

基于CPLD的看门狗电路电路设计实现

随着CPLD器件被广泛应用于各种仪器、仪表设备的设计中,而且CPLD几乎可模拟任何一种逻辑电路,所以,现在在设计时已完全没有必要再放置一片独立的看门狗器件,而完全可以将硬件看门狗电路整合于CPLD器件中,从而节省成本,降低系统的设计风险。下面具体介绍这种基于CPLD技术的看门狗电路的设计。

2018-03-05 16:58:01 2420

2420

2420

2420

在嵌入式设计中如何降低CPLD的功耗与电源电压管理技术分析

我们首先来了解在嵌入式设计中如何降低CPLD的功耗、电路板的面积和元器件成本。下一步,我们将看到在待机模式下如何尽量降低CPLD的功耗,不仅要仔细地选择器件,而且还要选择一个合适的总线驻留方案。器件工作期间,我们对节省功耗的探讨将包括选择逻辑门、智能I/O设计和精密的电源电压管理技术。

2018-12-04 09:09:00 2142

2142

2142

2142

基于CPLD的测试系统接口设计

介绍了一种用CPLD(复杂可编程逻辑器件)作为核心控制电路的测试系统接口,通过时cPLD和竹L电路的比较及cPLD在系统中实现的强大功能,论述了CPLD在测试系统接口中应用的可行性和优越性,简单介绍

2019-01-01 16:18:00 1472

1472

1472

1472

你需要知道基于CPLD节省电池能量的系统断电电路的设计

元件,实现一个节省电池能量的系统断电电路。在本例中,使用的CPLD是Altera EPM570-T100。使用一只外接P沟道MOSFET Q1和一只国际整流器公司 的IRLML6302(或等效器件),构成IC1 CPLD的一个电源控制开关。

2019-04-18 16:00:42 516

516

516

516

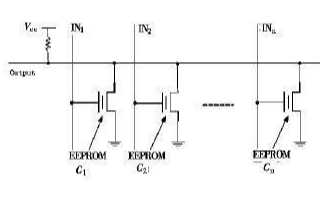

采用5管单元的SRAM结构实现CPLD可编程电路的设计

显然,设计基于SRAM编程技术的CPLD可以很好解决上述应用问题。CPLD的设计和实现的关键问题是核心可编程电路结构的实现。因此,本文主要探讨针对CPLD的核心可编程结构,如何设计具有相似功能且基于SRAM编程技术的电路结构,从而更好满足动态重构系统中实现复杂状态机和译码电路的应用。

2020-04-25 10:21:00 1687

1687

1687

1687

FPGA CPLD中的Verilog设计小技巧

FPGA CPLD中的Verilog设计小技巧(肇庆理士电源技术有限)-FPGA CPLD中的Verilog设计小技巧

2021-09-18 16:49:18 35

35

35

35cpld和单片机在脉冲开关电源中的应用

cpld和单片机在脉冲开关电源中的应用(通用电源技术_深圳有限公司)-cpld和单片机在脉冲磁铁开关电源中的应用.pdf

2021-09-29 16:39:06 20

20

20

20输入电源AD采样电路误差大及温度影响分析

输入电源AD采样电路误差大及温度影响分析一、 问题点软件实际测试过程中发现,16V时,测试到的IO口处的电压偏离理论最小值,不符合理论,导致电源管理功能异常。二、 电路三、 理论计算分析通过建立

2022-01-07 11:37:33 15

15

15

15输入电路的原理及常见电路

输入滤波电路:C1、L1、C2、C3组成的双π型滤波网络主要是对输入电源的电磁噪声及杂波信号进行抑制,防止对电源干扰,同时也防止电源本身产生的高频杂波对电网干扰。当电源开启瞬间,要对C5充电,由于瞬间电流大,加RT1(热敏电阻)就能有效的防止浪涌电流。

2023-04-16 10:26:29 1708

1708

1708

1708UPS电源的输入整流电路是啥,成分有很大改善

,而且又采用移相式控制,所以输入谐波电流较大,功率因数一般只有0.65左右。这种输入电路一般用在10kVA以下的UPS中。UPS电源的输入整流电路介绍另一种输入电路

2023-04-04 15:30:13 1005

1005

1005

1005

电子发烧友App

电子发烧友App

评论