介绍一种基于CPLD和嵌入式系统的高速数据采集系统,并详细阐述了系统的结构和软硬件的实现方案。

关键词:高速数据采集;CPLD;嵌入式系统

Design and Implementation of High?speed Data Sampling System Ba sed on

CPLD and Embedded System

CPLD and Embedded System

LIN Dehui, DAO Kegang, DENG Yonggang, CHEN Sen

Key words: high?speed data sampling; CPLD; embedded system

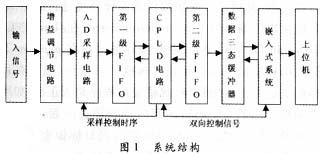

1系统结构

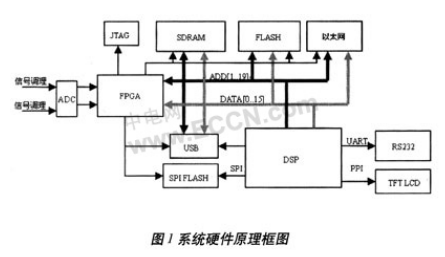

高速数据采集系统由高速ADC、CPLD、FIFO和嵌入式系统组成,系统结构如图1所示。

高速数据采集系统由高速ADC、CPLD、FIFO和嵌入式系统组成,系统结构如图1所示。

2.1嵌入式操作系统—Linux

Linux作为嵌入式操作系统有以下几大优点:

(1)可应用于多种硬件平台;(2)源代码公开;(3)微内核直接提供网络支持;(4)高度模块化使添加部件非常简单。

2.2硬件设计

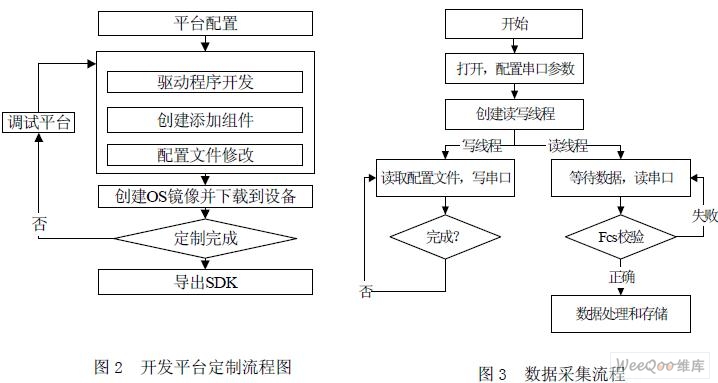

整个数据采集板采用双层设计,上层是嵌入式系统的核心板,包括嵌入式系统CPU、FLASH和SDRAM等系统基本配置。MPC860的控制总线与数据总线通过核心板100线×3的接口插座与下面的扩展板各芯片通讯。硬件的结构框图见图2。

Linux作为嵌入式操作系统有以下几大优点:

(1)可应用于多种硬件平台;(2)源代码公开;(3)微内核直接提供网络支持;(4)高度模块化使添加部件非常简单。

2.2硬件设计

整个数据采集板采用双层设计,上层是嵌入式系统的核心板,包括嵌入式系统CPU、FLASH和SDRAM等系统基本配置。MPC860的控制总线与数据总线通过核心板100线×3的接口插座与下面的扩展板各芯片通讯。硬件的结构框图见图2。

嵌入式系统的CPU选用Motorola的MPC860芯片。它内部集成了微处理器和一些控制领域的常用外围组件,特别适用于互联网络和数据通信。MPC860 PowerQUICC通信处理器可以根据用户的不同要求提供2~4个串行通信控制器、数据缓存,各种级别的网络协议支持。该处理器专为宽带接入设备如路由器、集线器、交换机和网关等设计。

2.2.2系统内存

系统内存由3部分组成,MPC860内部集成了4KB数据Cache,以及片外扩展的Flash和SDRAM。Flash为2片Am29LV160D,总容量为4MB×8bit,用来存放ppcboot.bin和linux.bin文件。SDRAM采用2片K4S641632F,总容量为16MB×8bit。

2.2.3通用外设

MPC860的4个串行通信控制器(SCC)支持以太网、HDLC/SDLC、HDLC总线(用以实现基于HDLC的局域网)、AppleTalk、UART、比特流透明传输、基于帧的透明传输(CRC可选)、支持PPP(Point to Point Protocol)的异步HDLC等标准协议,只需很少的外围芯片就可以实现串行口和USB Slave接口。MPC860外扩一片LXT905PC就方便地实现了一个10BASE?T的以太网接口。

2.2.4嵌入式系统调试

MPC860处理器支持BDM(背景调试模式),完成板卡硬件检测、下载、运行、烧写FLASH、内核调试、单步调试等最底层的调测功能。在背景调试模式下,通过向CPU发送命令,可以实现对寄存器、系统存储器的访问。

另外,在调试时还可以使用Motorola公司的Power TAP Pro仿真器和Code Warrior IDE for PowerPC编译环境在windows下进行应用程序的开发和调试。

2.2.5A/D转换和CPLD电路

A/D采样采用的器件为ADC08200,精度为8位,采样频率由20MSps至200MSps,本电路中的A/D采样频率为100MSps。CPLD芯片采用EPM3128ATC144-5,具有128个宏单元,可以提供2500个逻辑门,计数频率上限为192.3MHz。A/D采样时钟由CPLD提供。晶振频率为100MHz,直接接入到CPLD中,由CPLD产生累加电路的其他信号。

2.2.6CPLD器件的编程与调试

CPLD器件的编程采用VHDL语言。程序经过逻辑综合(逻辑综合的软件为Altera公司的QuartusⅡ 4.0)后即可利用下载线通过JTAG(联合测试行动组)接口将逻辑综合生成的*.pof文件烧写到CPLD器件中,然后即可测试芯片的功能。

2.2.7FIFO数据缓存电路

从图1可以看出,系统中包含两级FIFO。第一级FIFO芯片采用1片CY7C4251,容量为8KB×9bit,工作频率为100MHz。第二级FIFO采用2片CY7C4255并联,容量为8KB×36bit,但实际上只用了24bit数据宽度,因为8bit的A/D转换数据累加10000次,24bit就能满足系统的功能要求。

2.3软件开发

该数据采集系统的软件编程包括两部分,一部分是MPC860嵌入式系统的编程;另一部分是CPLD的编程。关于CPLD的编程模式见2.2.6,这里只介绍嵌入式系统的软件开发模式。

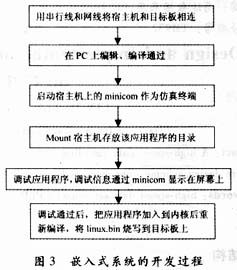

本系统采用交叉编译的方式进行Linux应用程序的开发和调试,先将应用程序在宿主机上调试通过后,再移植到目标板。这种模式适合于大型复杂的应用,优点是程序调试方便但移植需要做一些工作。其开发流程如图3所示。

2.2.2系统内存

系统内存由3部分组成,MPC860内部集成了4KB数据Cache,以及片外扩展的Flash和SDRAM。Flash为2片Am29LV160D,总容量为4MB×8bit,用来存放ppcboot.bin和linux.bin文件。SDRAM采用2片K4S641632F,总容量为16MB×8bit。

2.2.3通用外设

MPC860的4个串行通信控制器(SCC)支持以太网、HDLC/SDLC、HDLC总线(用以实现基于HDLC的局域网)、AppleTalk、UART、比特流透明传输、基于帧的透明传输(CRC可选)、支持PPP(Point to Point Protocol)的异步HDLC等标准协议,只需很少的外围芯片就可以实现串行口和USB Slave接口。MPC860外扩一片LXT905PC就方便地实现了一个10BASE?T的以太网接口。

2.2.4嵌入式系统调试

MPC860处理器支持BDM(背景调试模式),完成板卡硬件检测、下载、运行、烧写FLASH、内核调试、单步调试等最底层的调测功能。在背景调试模式下,通过向CPU发送命令,可以实现对寄存器、系统存储器的访问。

另外,在调试时还可以使用Motorola公司的Power TAP Pro仿真器和Code Warrior IDE for PowerPC编译环境在windows下进行应用程序的开发和调试。

2.2.5A/D转换和CPLD电路

A/D采样采用的器件为ADC08200,精度为8位,采样频率由20MSps至200MSps,本电路中的A/D采样频率为100MSps。CPLD芯片采用EPM3128ATC144-5,具有128个宏单元,可以提供2500个逻辑门,计数频率上限为192.3MHz。A/D采样时钟由CPLD提供。晶振频率为100MHz,直接接入到CPLD中,由CPLD产生累加电路的其他信号。

2.2.6CPLD器件的编程与调试

CPLD器件的编程采用VHDL语言。程序经过逻辑综合(逻辑综合的软件为Altera公司的QuartusⅡ 4.0)后即可利用下载线通过JTAG(联合测试行动组)接口将逻辑综合生成的*.pof文件烧写到CPLD器件中,然后即可测试芯片的功能。

2.2.7FIFO数据缓存电路

从图1可以看出,系统中包含两级FIFO。第一级FIFO芯片采用1片CY7C4251,容量为8KB×9bit,工作频率为100MHz。第二级FIFO采用2片CY7C4255并联,容量为8KB×36bit,但实际上只用了24bit数据宽度,因为8bit的A/D转换数据累加10000次,24bit就能满足系统的功能要求。

2.3软件开发

该数据采集系统的软件编程包括两部分,一部分是MPC860嵌入式系统的编程;另一部分是CPLD的编程。关于CPLD的编程模式见2.2.6,这里只介绍嵌入式系统的软件开发模式。

本系统采用交叉编译的方式进行Linux应用程序的开发和调试,先将应用程序在宿主机上调试通过后,再移植到目标板。这种模式适合于大型复杂的应用,优点是程序调试方便但移植需要做一些工作。其开发流程如图3所示。

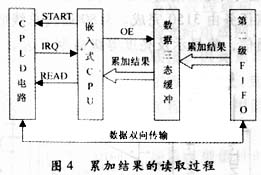

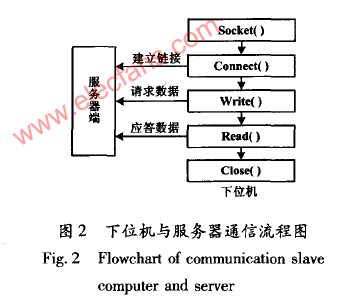

系统总的工作过程为:由MPC860发送一个START高电平给EPM3128,EPM3128接收到此信号后,产生2000个10ns的脉冲信号给ADC08200,采样后的数据存放在CY7C4251中。EPM3128产生CY7C4251的读脉冲依次读取FIFO中的数据并将其与从CY7C4255中取来的24位数据相加后再送回到CY7C4255中,每次累加在40ns中完成。这样循环10000次,就完成了数据的累加。累加完成后,EPM3128发送IRQ中断请求信号至MPC860,MPC860响应中断在IO口上产生READ低电平读信号,CPLD产生CY7C4255的读使能信号将数据读出送至三态缓冲器74F245,MPC860读取数据时发送OE信号选通数据三态缓冲器74F245将数据读出至MPC860数据总线,接收完数据通过 网口将数据发送给上位机处理。累加结果的读取过程如图4所示。

本文介绍的高速数据采集系统实现了分布式光纤温度传感器测温系统中噪声的有效抑制,具 有速度快、可靠性高的特点。另外由于CPLD的可编程性,可以对该电路板加以改造用在其他 的高速数据采集场合。

- 数据采集(112246)

相关推荐

5 Gsps高速数据采集系统该怎么设计?

高速实时频谱仪是对实时采集的数据进行频谱分析,要达到这样的目的,对数据采集系统的采样精度、采样率和存储量等指标提出了更高的要求。而在高速数据采集系统中,ADC在很大程度上决定了系统的整体性能,而它们的性能又受到时钟质量的影响。

2019-09-02 06:44:39

嵌入式系统采集图像数据的远程测量有什么优点?

随着后PC时代的到来和嵌入式的蓬勃发展,运用嵌入式系统实现远程数据采集已成为社会需求的趋势。本文采用嵌入式系统采集图像数据实现加工零件的远程测量,代替传统的人工检测。其特点有:网络化,准确性高,节约人力和物力。

2019-08-30 07:23:15

嵌入式系统怎么实现远程监控和升级?

通用分组无线服务技术GPRS(General Packet Radio Service)是一种移动数据业务,该技术能满足日常网络行为,具有广域覆盖、高速传输等优点。野外作业的数据采集嵌入式系统工作于

2019-08-02 06:49:24

嵌入式单片机视频报警系统的工作原理是什么?

利用以单片机应用系统为中心的小型嵌入式设备进行数据采集,并通过网络有效传输数据,已成为数据采集领域的研究焦点。由于嵌入式单片机系统集单片机和嵌入式系统为一体,因此嵌入式单片机系统广泛应用于那些对实时

2019-10-21 08:31:14

嵌入式多路信号数据采集系统有什么功能?

由于人们对数字形式信息的需求量越来越大,数据采集及其应用技术受到了越来越广泛的关注和应用。随着技术的发展,数据采集系统正向着高精度、高速度、稳定可靠和集成化的方向发展。目前,大多数的数据采集监控系统

2020-03-17 08:24:26

嵌入式电能计量及查询系统有什么功能?

本文设计了一个既能接入宿舍电量采集系统又能接入校内 Intranet 信息网络的嵌入式电能计量及查询系统,在电能数据采集终端 (ERTU)采用嵌入式ARM2410 芯片和嵌入式实时操作系统Linux

2019-09-26 07:08:15

嵌入式网络接入怎么实现?

的说法。利用该技术可以实现基于Internet的远程数据采集、远程控制、自动报警等功能,大大扩展嵌入式设备的应用范围;同时充分利用网络资源,实现更广泛的信息共享和更多信息服务。研究显示,截止2010年

2020-03-19 06:30:03

嵌入式视觉系统开发过程有什么技巧?

目前,关于视觉系统的研究已经成为热点,也有开发出的系统可供参考。但这些系统大多是基于PC机的,由于算法和硬件结构的复杂性而使其在小型嵌入式系统中的应用受到了限制。上述系统将图像数据采集后,视觉处理

2019-08-15 06:15:37

嵌入式视频数据采集的主要过程是什么?

卡驱动程序,V4L可以实现影像采集、AM/FM无线广播、影像CODEC、频道切换等功能。目前,V4L主要应用在影像串流系统与嵌入式影像系统里,其应用范围相当广泛。

2019-08-14 07:28:23

数据采集卡/分布式采集模块/无线通讯采集模块/嵌入式系统

无线通讯数据采集模块:GPRSZIGBEE4. 嵌入式系统:嵌入式主板平板电脑工控一体机QQ2693330939邮箱2693330939@qq.com 电话:*** 联系人江莽

2014-08-21 10:05:12

高速数据采集系统的硬件结构,CPLD在高速数据采集系统中的应用

高速数据采集系统的硬件结构MAX7000系列CPLD及其开发平台介绍CPLD在高速数据采集系统中的应用

2021-04-08 06:11:56

电子发烧友App

电子发烧友App

评论