宽频带数字锁相环的设计及基于FPGA的实现

数字锁相环(DPLL)技术在数字通信、无线电电子学等众多领域得到了极为广泛的应用。与传统的模拟电路实现的PLL相比,DPLL具有精度高、不受温度和电压影响、环路带宽和中心频率编程可调、易于构建高阶锁相环等优点。随着集成电路技术的发展,不仅能够制成频率较高的单片集成锁相环路,而且可以把整个系统集成到一个芯片上去。在基于FPGA的通信电路中,可以把全数字锁相环路作为一个功能模块嵌入FPGA中,构成片内锁相环。一般同步串行口通信方式的同步串行口之间的数据传输除了数据线外还必须有专门的同步时钟线,这种连接方式不但需要增加一条线路,同步性能受环境的影响还较大。利用数字锁相环可以从串行位流数据中恢复出接收位同步时钟。这样,串行口之间只用一根数据线就可以接收同步串行数据,简化了串行口的接口关系。本文介绍基于FPGA数字锁相环恢复串行数据位同步时钟的设计与实现及提高数字锁相环性能的措施。DPLL结构及工作原理

全数字锁相环路(DPLL)的基本结构如图1所示。主要由鉴相器DPD、数字环路滤波器DLF、脉冲加减电路(数控振荡器 DCO)和分频器(可控变模N)四部分构成。脉冲加减电路的时钟分别为2Nfc,fc为环路中心频率。DPLL是一种相位反馈控制系统。它根据输入信号fin与本地恢复时钟fout之间的相位误差(超前还是滞后)信号送入数字环路滤波器DLF 中对相位误差信号进行平滑滤波,并生成控制DCO 动作的控制信号DCS,DCO 根据控制信号给出的指令,调节内部高速振荡器的震荡频率,通过连续不断的反馈调节,使其输出时钟fout的相位跟踪输入数据fin的相位。

图1 全数字锁相环基本结构

环路模块具体功能及其电路实现

数字鉴相器的设计

常用的鉴相器有两种,异或门(XOR)鉴相器和边沿控制鉴相器(ECPD)。与一般DPLL的DPD设计不同,位同步DPLL的DPD需要排除位流数据输入连续几位码值保持不变的不利影响。本文采用改进型异或门鉴相器,它输出一个表示本地恢复时钟超前或滞后于输入信号的相位误差。如果本地恢复时钟超前于输入信号,则超前/滞后脉冲UD输出为高电平,反之UD输出为低电平,如图2所示。

图2 改进型异或门鉴相器的原理图及工作波形图

可见,在输出信号Fout为超前、滞后和同步于Fin时,PE脉冲的前沿距离Fin的上升沿相位是不等的。

数字环路滤波器的设计

数字环路滤波器(DLF)作用是消除鉴相器输出的相位差信号PE中的高频成分,保证环路的性能稳定,实际上可用一变模可逆计数器(设模数为K)来实现。K变模可逆计数器根据相差信号PE来进行加减运算。当PE为高电平时,计数器进行加运算,如果相加的结果达到预设的模值,则输出一个进位脉冲信号DP给脉冲加减电路;当PE为低电平时,计数器进行减运算,如果结果为零,则输出一个借位脉冲信号DP给脉冲加减电路。当Fout同步于Fin或只有随机干扰脉冲时,计数器加减的数目基本相等,计数结果在初始值处上下徘徊,不会产生进位和借位脉冲,滤除因随机噪声引起的相位抖动。计数器根据输出结果生成控制DCO 动作的控制指令。

K变模可逆计数器模值K对DPLL的性能指标有着很大的影响。计数器模值K的取值可根据输入信号的相位抖动而定,加大模值K,有利于提高DPLL 的抗噪能力,但是会导致较大的捕捉时间和较窄的捕捉带宽。减小模值K 可以缩短捕捉时间,扩展捕捉带宽,但是降低了DPLL 的抗噪能力。本设计中选择K=4。在初始时刻,计数器被置初值为K/2=2,这样可以DPLL捕捉速度很快。

数控振荡器的设计

数控振荡器( DCO)在数字锁相环路中所处的地位相当于模拟锁相环路中的电压控制振荡器。在本数字锁相环设计中使用数控振荡器是可变模式分频器。它的输出是调整可变分频器的模值N。该值的大小会随着每个Fin周期内(Fin=1时)鉴相输出PE进行调整。当UD为高电平时,将可变分频模值N增大,以调整分频输出使之相位滞后;当UD输出为低电平时,将可变分频模值N减小,已调整分频输出使之输出相位提前。如果数字环路滤波器没有控制脉冲信号DP输出,那么,分频模值N将保持不变,经除N分频后的输出本地恢复信号相位和输入信号相位处于同步状态。

本地高速时钟信号CLK由片外高速振荡器提供。时钟信号周期大小决定了DPLL 在锁定状态下相位跟踪的精度,同时,它还影响DPLL 的捕捉时间和捕捉带宽。为提高相位跟踪的精度以降低数据接收的误码率,时钟信号CLK的取值应尽量高。本设计中取高速时钟信号CLK的振荡频率为64MHz。数控振荡器可由一个可逆计数器实现。

N分频器的设计

N分频器则是一个简单的除N计数器。N分频器对脉冲加减电路的输出脉冲再进行N分频,得到整个环路的输出信号Fout。同时,因为Fout=CLK/2N=fc,因此通过改变分频值N可以得到不同的环路中心频率fc。另外,模值N的大小决定了DPLL的鉴相灵敏度为π/N。

环路实现

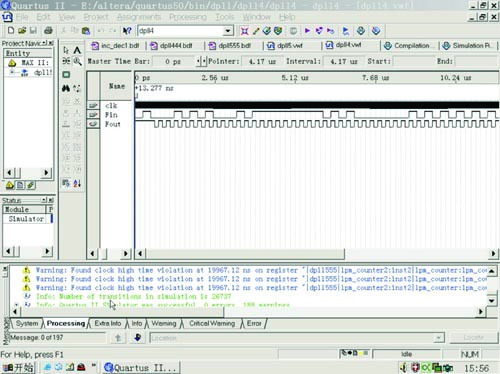

本设计在Altera公司QUARTUSII5.0 开发软件平台上,利用VHDL语言运用自顶向下的系统设计方法, 在Altera最新CPLD芯片MAXII240上设计全数字锁相环。将锁相环路设计完毕后,并通过QUARTUSII5.0集成环境进行仿真、综合、验证,DPLL设计结果如图3。

图3 改进型异或门鉴相器DPLL原理图

其中,可逆计数器counter2为环路滤波器DLF,预设初值为12,加法进位模值为4,减法进位模值为12。可逆计数器lmp_counter2为数控振荡器,其预置值为time[3..0],其输出即为锁相环路分频器的模值N,输出值大小随着控制脉冲信号DP的数目有关。在本设计中,fclk=64MHz,fin=2Mb/s,则time[3..0]=0100b=8。加法计数器lmp_counter2为模值N受控的锁相环路分频器。值得注意的是锁相环路分频器lmp_counter2的进位输出Cout不可直接作为分频输出,因为在仿真过程中发现随着fclk频率的升高,Cout容易产生冒险毛刺,影响锁相环的稳定性。因此外加一4输入或非门作为分频器输出判决。

在图4仿真结果中,fclk=64MHz,fin=2Mb/s。 仿真输入信号Fin为一任意的二进制码流信号。可见,对于多位连1或连0的码流信号,该锁相环的输出Fout都能准确恢复出同步所需的时钟。在第二个输入码位到来时本地恢复时钟Fout就已经进入同步状态,捕捉速度很快。相位锁定误差最大为π/2N=π/16。

图4 改进型异或门鉴相器DPLL仿真结果

捕获带宽的扩展

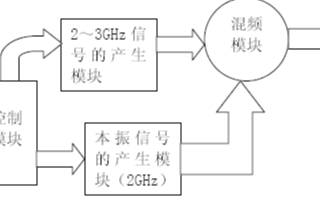

上述设计的数字锁相环虽然可以快速锁定,锁相精度也较高,但其捕捉范围较窄。该数字锁相环的最大相移调整能力为±π,一旦输入信号Fin的相位抖动超过这个范围或Fin的频率发生改变,锁相环无法自动完成捕捉锁定。因此,对该设计需进行扩展设计,以实现宽频带捕捉功能。 为实现宽频带捕捉,设置一专门电路,测定输入信号Fin每个比特的周期(或频率),并判定是否发生变化,若测得比特周期发生变化,就会去控制调整DCO的输出振荡频率,使其快速跟踪Fin的频率,再配合前述数字锁相环的相位跟踪,就可完成宽范围频率锁定。电路原理如图5。

图5 宽频带DPLL频率捕获电路原理图

将图5电路和图3上面的一个电路合并,即为完整的宽频带DPLL电路。测得输入信号Fin的周期信号time[3..0]被送往图3锁相环路分频器lmp_counter2,去控制DCO的输出振荡频率。该宽频带DPLL电路的捕获范围最高频率fcmax=fclk/4,最低频率fcmax=fclk/4M,M为N分频器的最大取值。本设计中,fclk =64MHz,M=16。所以锁相环的频率捕获范围理论值为16MHz-1MHz。对应于输入码流的速率为32MHz-2MHz。当Fin=16MHz和Fin=1.6MHz时的仿真结果如图6(1)(2)。

图6 (1)Fin=16MHz时的仿真波形

图6 (2) Fin=1.6MHz时的仿真波形

根据仿真结果,可实现稳定锁相的最低频率为1.2MHz,略高于理论值1MHz;可实现的最高锁相频率为16MHz。捕获时间1个Fin周期。

结语

在一般的数字锁相环设计中,“捕获时间”和“捕获带宽”这两项关键的性能指标是相互矛盾的,其中任何一项指标的提高都会牺牲另一项指标为代价。本文所介绍的宽频带范围数字锁相环采用较为简单的完成实现了捕获时间小而捕获带宽又相当宽的全数字锁相环,解决了“捕获时间”和“捕获带宽”指标相互矛盾的问题。其中“捕获带宽”指标可以通过提高工作时钟fclk的频率以及锁相环中的计数器的计数容量来进一步扩展。由于该数字锁相环可直接用于同步串行通信中二进制码流的同步时钟的恢复,可自动跟踪接收码流速率的变换,同时该设计是基于FPGA的模块化设计,便于其他数字系统设计的移植和集成,在其他数字应用系统特别是在基于FPGA的通信电路中有着重要的意义。

参考文献:

1. Kurt Aronow, Bela Geczy,FPGA-Based DPLL Approach Delivers Wide-Lock ange, 2005. 11,

2. 胡华春, 石玉. 数字锁相环原理与应用[M]. 上海科学技术出版社, 1990.

3. 方建邦, 董献忱, 王天玺. 锁相环原理及其应用[M]. 人民邮电出版社, 1988.

4. 潘松.黄继业. EDA技术与VHDL. 清华大学出版社, 2005.7

电子发烧友App

电子发烧友App

评论