ILGOO系列低功耗FPGA产品

Actel公司的ILGOO系列器件是低功耗FPGA产品,是在便携式产品设计中替代ASIC和CPLD的最佳方案。它在Flash*Freeze模式时的静态功耗最低可达到2µW,电池寿命是采用主流PLD的产品的5倍以上。针对I/O需求数目更多的低功耗应用,Actel可以提供IGLOO PLUS系列,规模分别是3万、6万和12.5万门。和相同封装的IGLOO器件相比,可以提供最多多出64%的I/O。其所有的器件都支持4个I/O Bank。在多电压应用环境中比较有利,并且支持热插拔和施密特触发器。Actel在IGLOO系列产品的开发过程中,对静态功耗的主要物理来源——漏电流方面做了改进。同时在生产过程中对产率、速度以及可靠性做了严密的监控。

采用IGLOO器件的低功耗优势从哪些方面获得呢?首先来自IGLOO器件本身对漏电流源头的控制,以及器件所提供的各种节省功耗的特性的实现和各种最少功耗数据存储技术的实现。除此之外,设计中采用一些低功耗技巧,也可以降低静态功耗。

IGLOO具有功耗友好的器件架构,能提供静态、睡眠、Flash*Freeze功耗模式,允许采用动态电压和频率调节技术来降低系统整体实际功耗。提供可选择的1.2V和1.5V的I/O和核电压,以方便用户平衡设计的性能和功耗之间的关系。IGLOO的时钟结构可以没有副作用的对全局信号和局部信号进行门控制。另外IGLOO的RAM模块具有LP和F*F端口来控制RAM本身的静态功耗。

系统温度及功耗概况

工业、汽车电子、军事, 甚至商业类客户都会对系统的温度和运行模式的概况有规定。这些概况指引我们在设计时要注意哪些地方以及精力该如何分配。IGLOO器件的低功耗工艺和硅片设计由Actel来保证,用户所要关注的是:关心器件的选型、掌握所使用的FPGA的架构、掌握PCB的板级布局(主要是电容及I/O的走线)。

对于同一系列的器件来说,器件的die越小,器件的功耗也会越小。也就是说,在选用器件的时候,应该尽量选择规模小的器件。选定器件后,可以在设计过程中,通过一些技巧尽可能的少占用资源,比如通过时分复用的方式少占用I/O,共享加法、乘法等算法逻辑,共享RAM等,同时也有必要了解所选用的FPGA的架构。

用户需要在功耗和速度之间做平衡,在对速度性能要求不高的时候,尽量使用低的核电压和低电压的I/O接口标准。根据设计工作的实际状况,在某些时候将当前不工作的资源关掉,比如通过控制SRAM的LP或BLK引脚,使其在不工作的时候可以被关断,或者是通过Flash Freeze端口进入Fresh Frezee模式以降低静态功耗。在PLL不需要工作的时候,通过Power Down引脚将其关掉,不过需要注意的是,需要考虑重新开启以后,PLL的锁定时间对系统是不是有影响。关掉没有输入总线的I/O Bank。

注意,不要滥用上拉/下拉电阻。在活动模式下,如果总线被反向模式驱动(如上拉的被“0”驱动,或下拉的被“1”驱动),那么每个I/O上的电流会增加。要预防被驱动的总线进入3态状态。除非FPGA的工作时间确实短,否则建议跟板子设计者沟通以确保对输入进行持续的驱动。

要降低设计的动态功耗,首先要了解影响动态功耗的因素。动态功耗通常和电压、信号翻转频率、容性负载正相关,设计所占用的逻辑资源越多、时钟频率越高、I/O和RAM越多,动态功耗就越大。同时也需要分析设计的动态功耗概况。

确定要降低的动态功耗的目标,如果要降低的动态功耗的目标是目前整个系统动态功耗的20%,那么选用Actel的IGLOO器件或许就可以实现所要达到的目标。如果目标是80%,那么除了选用IGLOO器件外,还需要从系统和架构上去考虑。

针对不同的系统功耗的概况,梳理动态功耗的重点,见图1。针对Case1中动态功耗的示意图,我们可以看出其功耗主要分布在逻辑、存储和时钟方面,这样我们的精力就不能放在如何降低I/O的功耗上去,而针对Case3这种情况,如果要降低动态功耗,就必须要解决I/O上的功耗问题。

图1 不同系统的动态功耗在线座谈精华

要减少RAM的功耗,除了对RAM的控制和时钟信号进行门控制以外,还需要知道RAM的读和写分别对功耗的影响有多少。地址变化、读写顺序、RAM级联方式对功耗的影响。

对RAM进行读操作涉及到:控制所存地址和控制锁存、行的预译码电路、读的列译码电路、行的最终译码电路、读的列译码控制、传感放大器、数据输出选择和锁存电路、Sense enable logic、读控制电路、Bit-line预充电电路等十个相关电路。而对RAM进行写操作需要涉及到的电路有:地址和控制锁存、行的预译码电路、写的列译码电路、行的最终解码控制、写的列译码控制、写驱动电路和Bit Line预充电电路。因此,相比较而言,读操作会比写操作消耗更多的功耗。

RAM的读写地址改变的方式,也会对功耗有不同的影响。连续操作地址之间的汉明距离越小,产生的功耗也越小。反之亦然。也就是说当前操作的地址和上次操作的地址之间变化的位数越少,所产生的功耗也会越小。

读写间隔操作和连续读、连续写操作相比,要产生多一些的功耗。从图2中分别对12块RAM、16块RAM和24块RAM做的测试结果看,同样的操作条件下,RAM块数越多,连续操作地址之间的汉明距离越长,功耗就越大。同样的块数和连续操作之间的汉明距离,写-读三次会比三次写三次读消耗的功耗要大。

图2 写读操作顺序vs.读序列后跟写序列操作

通过前面所述,我们可以通过调整RAM的访问顺序降低RAM的功耗。可能的话,对RAM少进行读操作,尽可能一次多读一些数据或者多写一些数据,少一些读写操作之间的切换。如果在连续相同操作的地址之间,汉明距离能保持最小的话更好。也可以考虑在反向时钟沿上对RAM进行读写操作,以降低RAM的峰值功耗。

不同的RAM级联架构所产生的功耗也不同。如果想获得一个4K×4的RAM,有许多不同的实现方式。从图3中可以看出,根据这些不同的实现方式,对每块RAM的读写时钟控制,进行门控制所产生的功耗是最低的。

图3 根时钟vs.叶时钟vs.门控允许

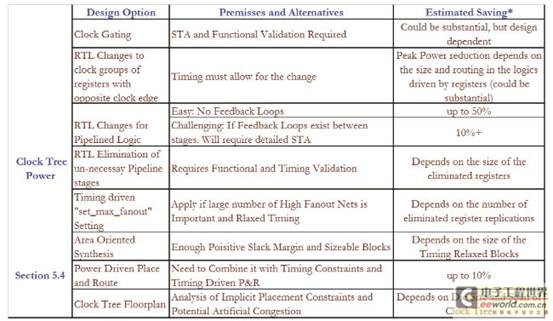

在降低时钟树的功耗方面,常用的方法有使用门控时钟,对常用的流水线时钟结构进行修改,尽量使用FPGA内部的全局时钟资源等。通过对常用的流水线时钟结构在RTL级进行修改,就像在图4中所看到的,做正反时钟沿间隔,这样时钟频率可以减慢一半,可以节省该时钟路径一半的功耗。同样可以通过人工对时钟域进行平面布局,来降低时钟树产生的功耗。这种方式对工程师的要求相对较高。Actel的设计师提供基于功耗驱动的布局布线策略。选择该策略,布局布线工具自动会在满足时序要求的情况下,尽可能的降低布局功耗。

图4 对常用的流水线时钟结构在RTL级做修改

要降低逻辑和走线的功耗,需要调整综合选项、了解算法/功能块的架构和功耗概况,通过减少信号的翻转来降低功耗。不同的综合选项和策略会对动态功耗有影响,基本上需要注意的是全局时序的设定以及set_max_fanout选项,以及是选用面积优先还是时序优先的综合策略。

通过对DesignWare和一些私有的加法器和不同频率下的功耗的评估,DesignWare下面的BK加法器在功耗方面是最友好的。针对同样5%到10%的速度降级,BK加法器和其他的私有加法器的核相比,可以减少10%到15%的面积和功耗。在选择乘法器的时候,必须要考虑乘法器的面积、功耗和速度。

计数器在设计中有不同的用法,有的用于计算事件发生的顺序或者用掉的时间,有的用于驱动类似于RAM的地址总线、数据总线、状态机的下一跳状态或者输出逻辑,有的用于当输出的值达到不同的解码值时做不同的设定的处理。根据不同的用途可以考虑用二进制顺序计数、格雷码计数、环形计数的实现方法。如果计数器只是用于产生一些标记,建议采用二进制的实现方式;如果计数器用于驱动一个大的负载总线,建议用格雷码计数器;如果多个计数器的值需要被解码,环形计数器是最佳选择(译码逻辑是最小的)。

通过降低逻辑的翻转率来降低动态功耗

首先在设计中,需要尽量避免不必要的翻转,可以通过下面几个步骤来实现这一目标:首先分析哪些逻辑的翻转是不必要的,随后对不必要的逻辑翻转的传播进行限制,展开逻辑翻转的时间。

减少逻辑可能产生的毛刺,先标识出翻转率高的网络以及它们的驱动,然后对驱动单元输入的最坏时序情况做评估,随后将毛刺的源往前调或往后调,然后对驱动单元的输入的最坏时序情况做评估,最后在驱动的逻辑后面插入一级触发器,根据先前的评估情况来决定用路径上其他时序元件的相同时钟沿或者相反的时钟沿来驱动触发器。即使是在单周期路径上面,如果有足够的slack来增加一个与门以及相关走线,那么就可以用与门的另外一个输入(毛刺源驱动寄存器)的反相时钟沿,从而减少毛刺。在某些情况下,可以通过伸展反转时间来降低毛刺的峰值功耗。

建议设计者要了解最终系统的运行模式,以及每种模式下系统的功耗概况。如果系统处于睡眠模式或者关闭模式的时间较长,需要观察浪涌电流和编程电流的影响,并处理好静态功耗。需要检查设计的动态功耗概况,找出功耗的主要瓶颈,根据概括表(图5~图8)找出最好的解决方法。

图5 RAM 动态功耗概括表

图6 I/O功耗概括表

图7 时钟树功耗概括表

图8 逻辑功耗概括表

在对照概括表之前,只要时序允许,可以修改RTL代码;保证修改以后的功能和时序有效性;也可以尝试调整综合选项以及使用基于功耗优先的策略来进行布局布线。

电子发烧友App

电子发烧友App

评论