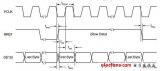

对于数据采集接收的一方而言,所谓源同步信号,即传输待接收的数据和时钟信号均由发送方产生。FPGA应用中,常常需要产生一些源同步接口信号传输给外设芯片,这对FPGA内部产生

2012-05-04 11:42:26 4167

4167

在时分复接通信系统中,位同步是收、发两端的时钟频率必须同频、同相,这样在接收端才能正确地判决发送端送来的每一个码元。为了达到收、发端频率同频、同相,在设计传输码型时,一般要考虑传输的码型中应含有发送

2020-07-30 18:02:44 1076

1076

时钟使能电路是同步设计的重要基本电路,在很多设计中,虽然内部不同模块的处理速度不同,但是由于这些时钟是同源的,可以将它们转化为单一的时钟电路处理。在FPGA的设计中,分频时钟和源时钟的skew不容易

2020-11-10 13:53:41 4795

4795

7系列FPGA时钟资源通过专用的全局和区域I/O和时钟资源管理符合复杂和简单的时钟要求。时钟管理块(CMT)提供时钟频率合成、减少偏移和抖动过滤等功能。非时钟资源,如本地布线,不推荐用于时钟功能。

2022-07-28 09:07:34 1276

1276 “全局时钟和第二全局时钟资源”是FPGA同步设计的一个重要概念。合理利用该资源可以改善设计的综合和实现效果;如果使用不当,不但会影响设计的工作频率和稳定性等,甚至会导致设计的综合、实现过程出错

2023-07-24 11:07:04 655

655

摘要:FPGA异步时钟设计中如何避免亚稳态的产生是一个必须考虑的问题。本文介绍了FPGA异步时钟设计中容易产生的亚稳态现象及其可能造成的危害,同时根据实践经验给出了解决这些问题的几种同步策略。关键词

2009-04-21 16:52:37

FPGA时钟问题 2010-06-11 15:55:39分类: 嵌入式1.FPGA的全局时钟是什么?FPGA的全局时钟应该是从晶振分出来的,最原始的频率。其他需要的各种频率都是在这个基础上利用PLL或者其他分频手段得到的。

2021-07-29 09:25:57

我们的设计用到了FPGA和AD9789进行CMOS电平的数字通信。fpga的时钟跟AD9789的时钟是异步的,不知道这样的设计会不会导致fpga和ad9789的通信不稳定,如何避免。fpga和ad9789是如何同步的?通信速率fs=18.284MHz,fdac=2.395204GHz。谢谢!

2023-12-21 08:29:25

PART 1

同步是基本需求

时钟同步,对于无线网络来说至关重要。从2G到5G,不同的无线接入技术对频率同步和相位同步的精度都有着不同的要求。

同步的基本原理和对表类似。

每个

2023-05-10 17:09:50

视频信号(包括数据与时钟,其中数据位宽16位,时钟1位,最高工作频率148.5MHZ).2.遇到的问题时钟相对于数据的延时,也就是信号的建立与保持时间在经过FPGA后出现偏移。造成后端的DA不能正确的采集到数据。

2014-02-10 16:08:02

系统中频率最高的信号; ⑶ 时钟信号通常是负载最重的信号,所以要合理分配负载。 出于这样的考虑在 FPGA 这类可编程逻辑器件内部一般都设有数量不等的专门用于系统时钟驱动的全局时钟网络。这类网络

2012-03-05 14:29:00

拉票第一名,所以直接获得试用机会项目描述:位同步时钟提取现在本科阶段平时喜欢钻研,征战了2016TI杯电子设计竞赛,并获得省二,对FPGA以及Verilog HDL有一定程度的了解,自己通过FPGA

2016-08-29 15:40:44

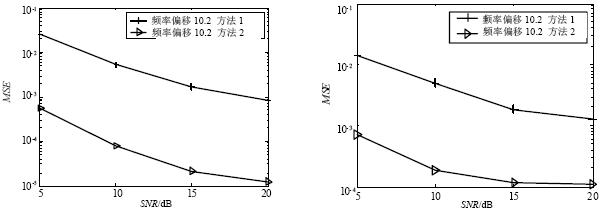

估计法(Kay法)比较具有代表性,它在高信噪比条件下可达到Cramer-Rao界(CRB),并且运算量不大,适于硬件实现。本文以Kay频率估计法为基础构建了一种适用于脉冲信号的载波频率同步环,并通过计算机仿真和FPGA实现来验证其有效性。

2023-09-20 08:28:04

我在我的同学面前炫耀FPGA是做高速处理的,可是,当人家问我,我的时钟频率能达到多少时,我说利用PLL能拉到200MHz,他说,这么低啊?我的手机频率都是1.5G的呢。我无语。。。后来才了解到,他

2012-03-08 17:11:08

呢?一般根据关系的紧密程度分为“频率同步”和“相位同步”这两个级别。频率同步是指两个基站的时钟的变化频率一致,而相位则不一定一致,可以保持相对固定的差值。

假设两个基站内部各有一个钟表,在某一

2023-05-10 16:06:10

?一般根据关系的紧密程度分为“频率同步”和“相位同步”这两个级别。频率同步是指两个基站的时钟的变化频率一致,而相位则不一定一致,可以保持相对固定的差值。

假设两个基站内部各有一个钟表,在某一

2023-05-06 12:37:03

将造成30μm的运动误差。高速加工中心中加工速度为120m/min时,伺服电机之间1μs的时间同步误差,将造成2μm的加工误差,影响了加工精度的提高。分布式网络中节点的时钟通常是采用晶振+计数器的方式

2019-09-19 08:14:19

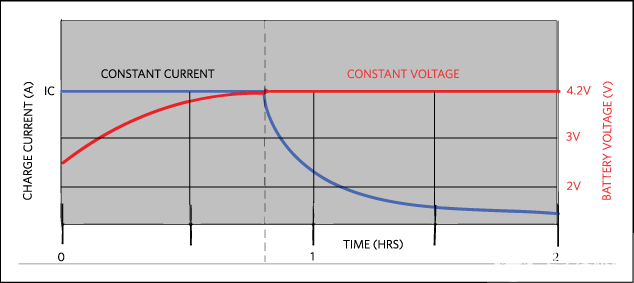

YB2414高效率同步降压转换器

概述:

YB2414是一款高效率500 kHz同步降压DC-DC转换器,能够提供4A/5A电流。 YB2414可在4.5V至18V的宽输入电压范围内工作,并集成

2024-01-13 12:14:59

必须适当地与所有数据位的到达保持同步。如果接收器使用发射时钟,可能会要求延迟从发送端到接收端的时钟信号。 有时设计可能需要一个更高的时钟频率来运行FPGA上的逻辑。但是,只有低频率输出的时钟源可以用

2020-04-25 07:00:00

,降低AFE灵敏度。频率同步的作用频率同步可用于控制开关谐波的位置,并最小化否则会降低系统灵敏度的开关拍频率。这种技术经常用于负载点直流调节的开关模式电源(开关电源),其中功率调节器与外部时钟源同步

2020-01-06 15:50:31

具有外部频率同步的LTC3728LCUH 5V / 4A,3.3V / 5A稳压器的典型应用电路。 LTC3728L是双路高性能降压型开关稳压控制器,可驱动所有N沟道同步功率MOSFET级

2020-06-15 09:39:00

演示电路DC1598A是一款固定频率同步降压 - 升压转换器,具有扩展的输入和输出范围。独特的4开关单电感架构可在高于,低于或等于输出电压的输入电压下提供低噪声和无缝操作

2020-08-10 09:40:04

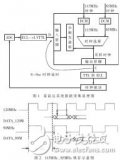

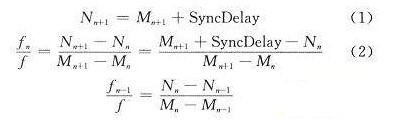

本文研究了一种可对频率进行动态调整的时钟,通过对时钟频率的动态修正,实现主从时钟频率的同步,进而实现时间同步。

2021-04-08 06:23:43

摘要:随着石油勘探的发展,在地震勘探仪器中越来越需要高精度的同步技术来支持高效采集。基于这种目的,采用FPGA技术设计了一种时钟恢复以及系统同步方案,并完成了系统的固件和嵌入式软件设计。通过室內测试

2019-06-18 08:15:35

STEVAL-ISA077V2,基于L6920D的高效率同步整流升压转换器演示板。基于L6920D的高效率同步整流升压转换器演示板

2020-07-30 07:25:55

我想做多个FPGA的时钟同步,目前的想法是用一个FPGA的内部时钟,复制到外接IO口,接到另一个FPGA的外部时钟引脚,波形有较小的相移但是可以保证同步。想问一下可以复制多次,驱动多个FPGA的同步吗。对驱动能力有什么要求?其中每一个FPGA都用的是一个EP4CE的最小系统板。

2019-01-21 15:07:41

本文研究了一种可对频率进行动态调整的时钟,通过对时钟频率的动态修正,实现主从时钟频率的同步,进而实现时间同步。

2021-05-10 07:01:08

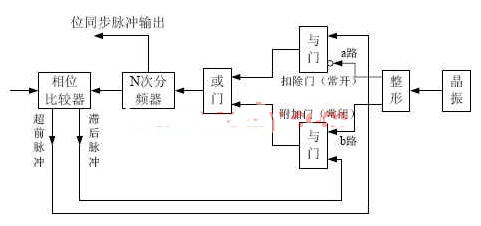

信息。自同步法又可以分为两种,即开环同步法和闭环同步法。开环法采用对输入码元做某种变换的方法提取位同步信息。闭环法则用比较本地时钟和输入信号的方法,将本地时钟锁定在输入信号上。闭环法更为准确,但是也更为复杂。那么,我们该怎么利用FPGA设计提取位同步时钟DPLL?

2019-08-05 06:43:01

方法并没有从根本上解决时钟频率的不同步问题,因此要进一步提高同步精度很困难。 如何设计使主从时钟频率同步?这个问题急需考虑!

2019-08-06 06:34:51

灵敏度。频率同步的作用频率同步可用于控制开关谐波的放置并最小化切换拍频,否则会降低系统灵敏度。该技术通常用于开关模式电源(SMPS),用于负载点DC-DC调节,其中功率调节器与外部时钟源同步。SMPS

2019-03-25 21:49:46

,否则会降低系统灵敏度。该技术通常用于开关模式电源(SMPS)中,以实现负载点DC-DC调节,其中电源调节器与外部时钟源同步。SMPS因其高效率而被普遍使用,但它们也带来了独特的排放挑战。频率同步在

2020-11-21 09:50:48

本文主要研究了一种基于FPGA、自顶向下、模块化、用于提取位同步时钟的全数字锁相环设计方法。

2021-05-06 08:00:46

的代码时,都需要调整采样时钟的相位才能够进行正确的采样,有时调整相位也采样不正确。这是采样时钟与数据不同步造成的么?我在网上看了一些资料,说可以使用idelay增加时钟的延时,我的FPGA

2016-08-14 16:58:50

计算FPGA外部引脚的频率。我需要将其与内部FPGA时钟同步吗?内部参考时钟以60Mhz运行,外部频率在10khz到15khz之间变化,不同步的外部频率是否会导致错误或问题?以上来自于谷歌翻译以下

2019-06-18 09:37:29

需要一款小功率同步电机,以及驱动板,去哪里购买比较合适?

2014-09-18 12:00:43

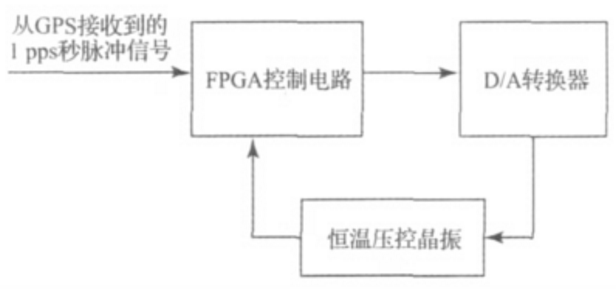

在介绍了GPS 同步时钟基本原理和FPGA 特点的基础上,提出了一种基于FPGA 的GPS同步时钟装置的设计方案,实现了高精度同步时间信号和同步脉冲的输出,以及GPS 失步后秒脉冲的平

2009-07-30 11:51:45 40

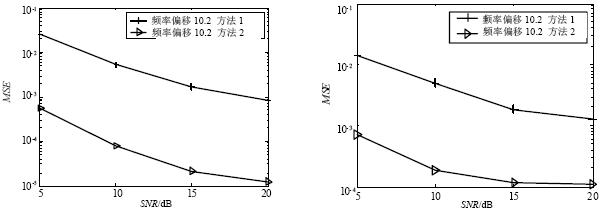

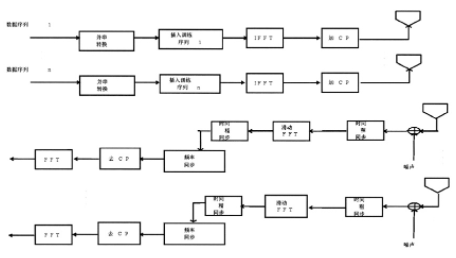

40 FMT系统的频率同步算法:提出了一种基于训练符号的FMT系统的频率同步算法,并分析了其性能.仿真结果表明,采用辅助数据的频率同步算法,改进了SCA算法,在快衰落环境

2010-03-18 16:22:09 25

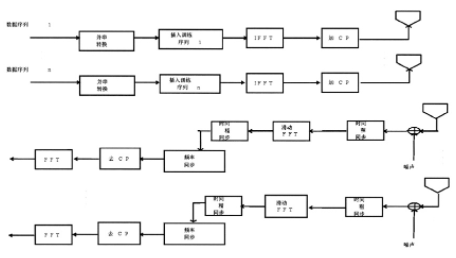

25 针对OFDM技术中的载波频率同步问题,分析了载波频率偏差对OFDM系统造成的影响,总结了基于IEEE802.11标准的三种常见的频偏估计算法:基于循环前缀的最大似然算法、基于训练序列

2010-10-08 16:32:13 18

18 OFDM的频率同步算法

文中提出的频率同步方法是在取得时间同步后,将接收的每PN序列长度的数据与本地PN序列作相关,共得L个值,分别为c1

2009-03-01 16:43:00 978

978

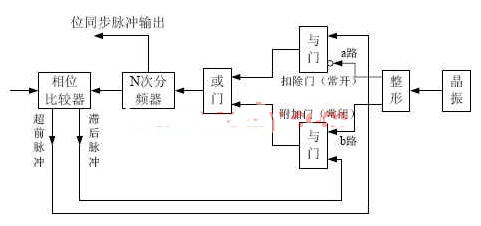

基于FPGA的提取位同步时钟DPLL设计

在数字通信系统中,同步技术是非常重要的,而位同步是最基本的同步。位同步时钟信号不仅用于监测输入码元信号,确保收发

2010-01-25 09:36:18 2890

2890

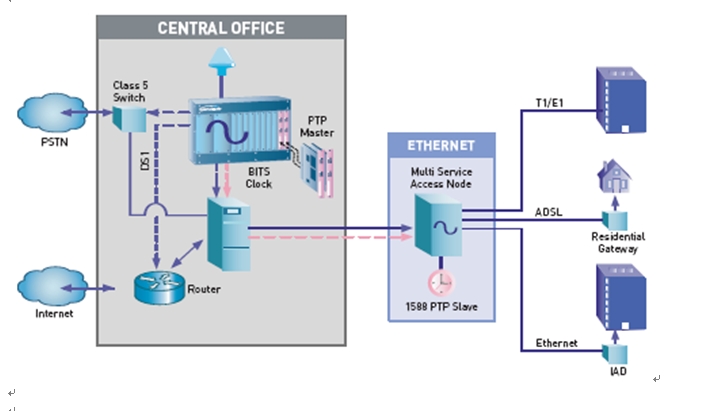

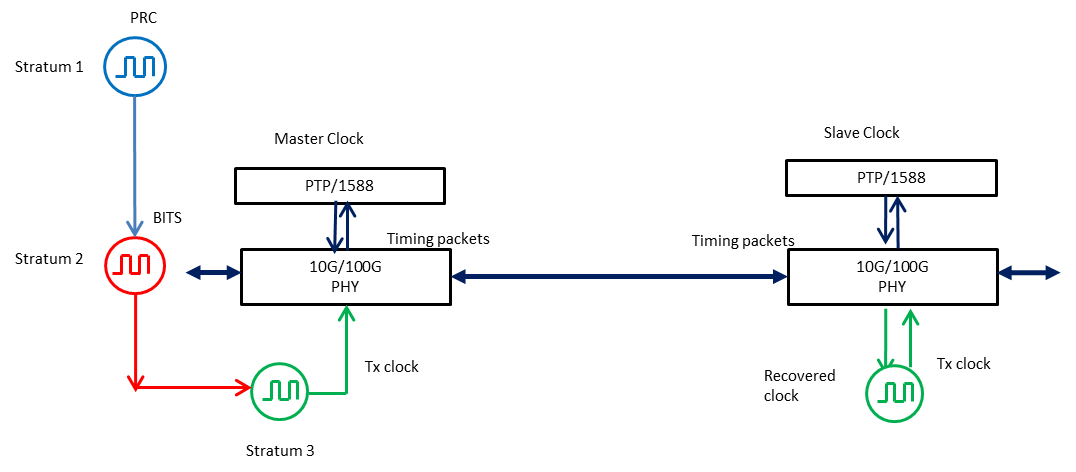

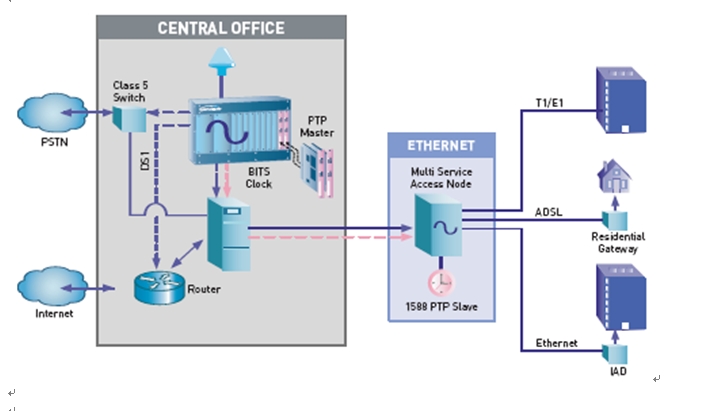

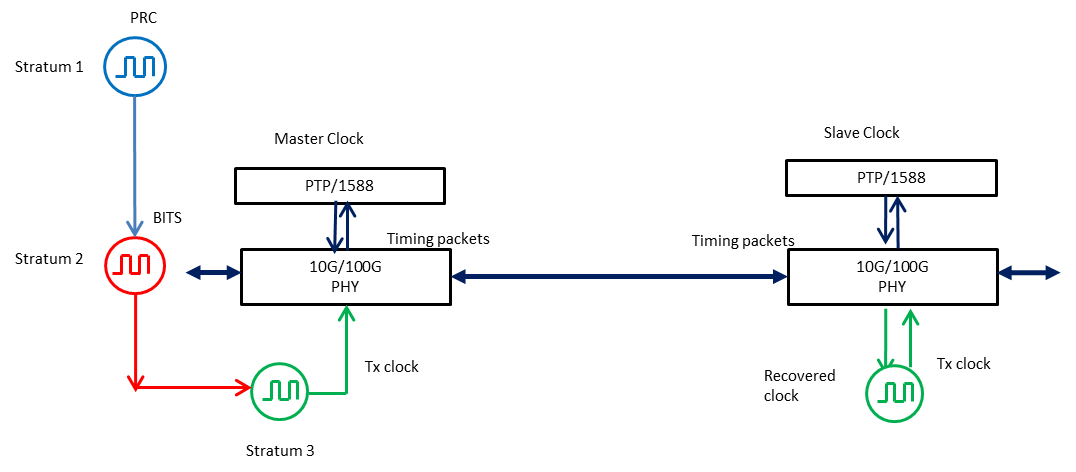

IEEE 1588精密时间协议—分组网络上的频率同步

电信网络正在从电路交换技术快速转向分组交换技术,以满足核心网和接入网对带宽需求的迅速扩大。传统的电路交换TDM

2010-02-03 09:25:53 4542

4542

同步网时钟及等级

基准时钟 同步网由各节点时钟和传递同步定时信号的同步链路构成.同步网的功能是准确地将同步定时信号从基

2010-04-03 16:27:34 3661

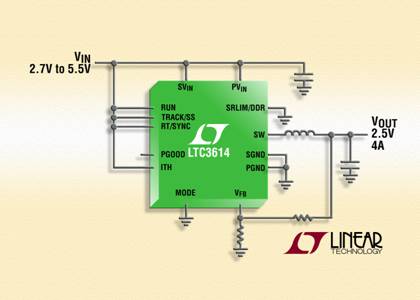

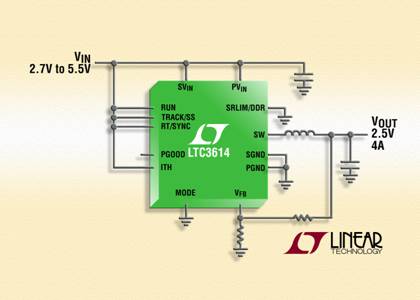

3661 高效率同步降压型稳压器LTC3614(Linear)

LTC3614器件采用恒定频率、电流模式架构,能够实现高达 4MHz 的开关频率。低电阻内部开关

2010-04-17 10:21:55 892

892

基于fpga的锁相环位同步提取电路

该电路如图所示,它由双相高频时钟

2010-10-08 12:00:23 1483

1483

一,单频网的同步过程 上一章所谈的同频网的频率效率及功率效率的代价是实现广播网内的发射机的同步工作,也就是在单频网中实现频率,时间以及比特的三同步。 (1)频率同步

2011-05-11 08:28:23 14

14 凌力尔特公司 (Linear Technology Corporation) 推出具备非线性控制、差分输出电压检测和时钟同步功能的固定频率同步降压型 DC/DC 控制器 LTC3867

2011-08-13 14:33:37 1211

1211

在FPGA设计中,为了成功地操作,可靠的时钟是非常关键的。设计不良的时钟在极限的温度、电压下将导致错误的行为。在设计PLD/FPGA时通常采用如下四种类型时钟:全局时钟、门控时钟

2011-09-21 18:38:58 3472

3472

鉴于电网频率具有正常波动范围, 因而实时数据采集构成对电网的电量进行分析、实时监测的关键环节。分析了同步采样和准同步采样两种频率跟踪技术, 系统采用了同步采样方法中的硬

2011-10-28 15:40:49 69

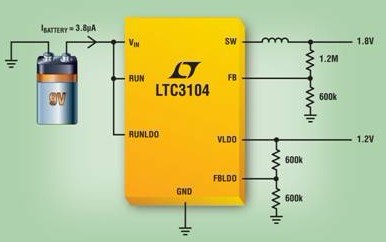

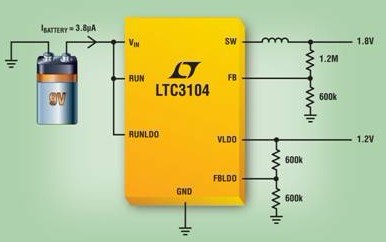

69 凌力尔特公司 (Linear Technology Corporation) 推出 15V、固定频率同步降压型转换器 LTC3103 和 LTC3104,

2011-11-29 17:07:58 1011

1011

FPGA 异步时钟设计中如何避免亚稳态的产生是一个必须考虑的问题。本文介绍了FPGA 异步时钟设计中容易产生的亚稳态现象及其可能造成的危害,同时根据实践经验给出了解决这些问题的

2011-12-20 17:08:35 63

63 永磁同步电机(PMSM)可以用一个与电源频率同步的恒定速度进行旋转,而不受负载和线路电压的影响。电机运行可以保持恒定的,与电源频率同步的速度,只要转矩不超过电机的极限运

2012-02-03 17:11:02 0

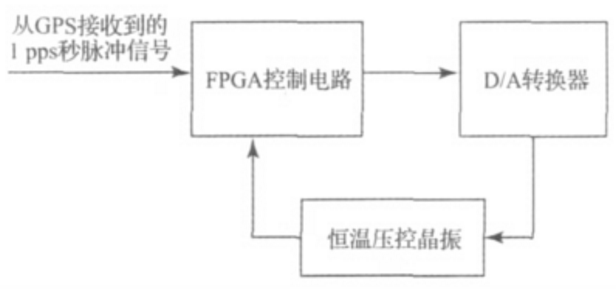

0 文章结合高精度晶振无随机误差和GPS秒时钟无累计误差的特点,采用GPS测量监控技术,对高精度晶体振荡器的输出频率进行精密测量和调节,使晶振的输出频率同步在GPS系统上,从而提

2012-08-09 14:07:29 5152

5152

2016年1月12日,致力于亚太地区市场的领先半导体元器件分销商---大联大控股宣布,其旗下友尚推出业内首款具有频率同步功能的TI的20A和30A同步DC/DC降压转换器---TPS544B25和TPS544C25。

2016-01-12 16:24:54 921

921 致力于亚太地区市场的领先半导体元器件分销商---大联大控股宣布,其旗下友尚推出业内首款具有频率同步功能的TI的20A和30A同步DC/DC降压转换器---TPS544B25和TPS544C25

2016-01-13 15:02:32 1298

1298

目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。

2017-02-11 11:34:11 4223

4223 时钟频率(又译:时钟频率速度,英语:clock rate),是指同步电路中时钟的基础频率,它以“若干次周期每秒”来度量,量度单位采用SI单位赫兹(Hz)。它是评定CPU性能的重要指标。一般来说主频数字值越大越好。外频,是CPU外部的工作频率

2017-11-10 14:21:26 23331

23331

介绍了精密时钟同步协议(PTP)的原理。本文精简了该协议,设计并实现了一种低成本、高精度的时钟同步系统方案。该方案中,本地时钟单元、时钟协议模块、发送缓冲、接收缓冲以及系统打时标等功能都在FPGA

2017-11-17 15:57:18 6196

6196

异步复位同步释放 首先要说一下同步复位与异步复位的区别。 同步复位是指复位信号在时钟的上升沿或者下降沿才能起作用,而异步复位则是即时生效,与时钟无关。异步复位的好处是速度快。 再来谈一下为什么FPGA设计中要用异步复位同步释放。

2018-06-07 02:46:00 1989

1989 本文主要介绍了基于FPGA的压控晶振同步频率控制系统的研究与设计。利用GPS提供的1pps秒脉冲信号,为解决上述问题,在FPGA的基础上利用干扰秒脉冲信号消除和偏差频率平均运算等方法,减少外围电路

2018-03-02 14:55:59 4473

4473

FPGA输入数据与FPGA内部时钟的相对相位关系不确定;在时钟频率可变的情况下,相对相位关系还会随频率变化。在FPGA内部一般采用D触发器实现对输入数据的采样。为了避免亚稳态 ,D触发器要求输入数据相对时钟

2018-08-02 16:03:00 1858

1858

分布式网络中节点的时钟通常是采用晶振+计数器的方式来实现,由于晶振本身的精度以及稳定性问题,造成了时间运行的误差。时钟同步通常是选定一个节点时钟作为主时钟,其他节点时钟作为从时钟。主节点周期性地通过

2019-05-05 08:17:00 11795

11795

基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统。但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免。如果对跨时钟

2018-09-01 08:29:21 5302

5302

交换网络提供更高质量的同步与定时机制。传统以太网没有内置时钟的分布能力,同步以太网对现有以太网做了一种扩展,类似TDM网络在物理层发布时钟,实现了设备间时钟频率同步。但是还有一些应用需要时间上的同步

2020-01-13 16:29:21 3387

3387

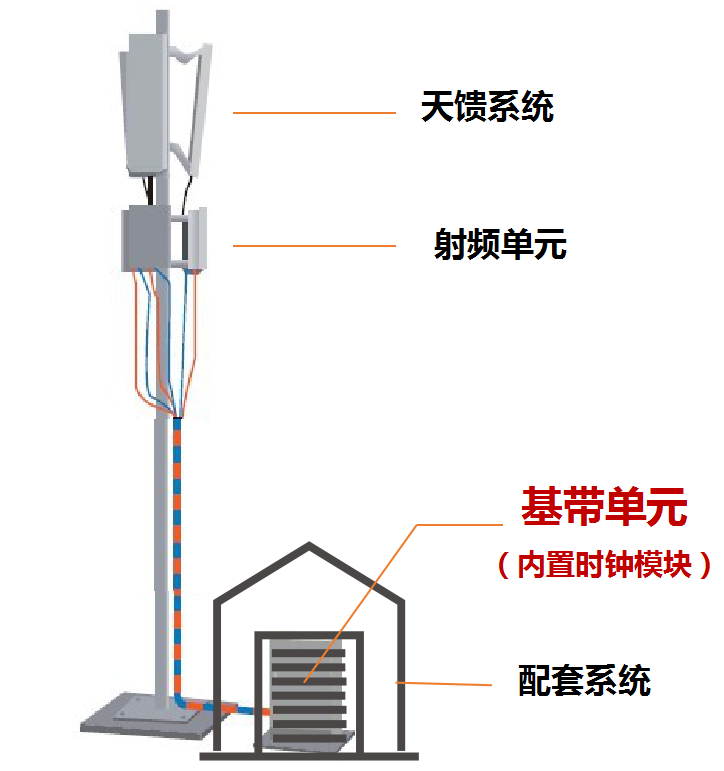

PART1同步是基本需求时钟同步,对于无线网络来说至关重要。从2G到5G,不同的无线接入技术对频率同步和相位同步的精度都有着不同的要求。

2020-10-18 09:41:27 5731

5731

对于 FPGA 来说,要尽可能避免异步设计,尽可能采用同步设计。 同步设计的第一个关键,也是关键中的关键,就是时钟树。 一个糟糕的时钟树,对 FPGA 设计来说,是一场无法弥补的灾难,是一个没有打好地基的楼,崩溃是必然的。

2020-11-11 09:45:54 3656

3656 PLL 是一种用来同步输入信号和输出信号频率和相位的相位同步电路,也可用来实现时钟信号的倍频(产生输入时钟整数倍频率的时钟)。在 FPGA 芯片上,PLL 用来实现对主时钟的倍频和分频,并且 PLL

2020-11-16 17:04:44 3292

3292 区域(Region):每个FPGA器件被分为多个区域,不同的型号的器件区域数量不同。

FPGA时钟资源主要有三大类:时钟管理模、时钟IO、时钟布线资源。

时钟管理模块:不同厂家及型号的FPGA

2020-12-09 14:49:03 20

20 界。应用数字下变频技术和Kay算法实现载波频率的精确估计。设计实例的仿真结果表明了该环路的有效性,环路可在短对同内完成高精度的载波频率同步。

2021-02-05 17:35:53 36

36 传统的异步采集方法会影响采集到的功耗信息的信噪比,降低功耗分析的成功率。针对异步采集的问题提出一种新的时钟同步功耗信息采集方法。该采集方法基于现场可编程门阵列(FPGA)的时钟同步采集平台

2021-03-31 15:50:21 6

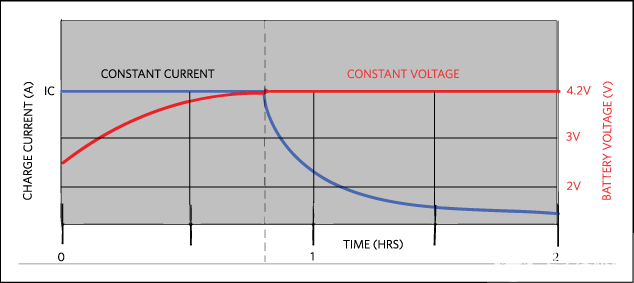

6 电子发烧友网为你提供带有频率同步的电池充电电路设计资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-22 08:46:26 2

2 LTM4608A:低VIN,8A DC/DCμ模块(电源模块)稳压器,带跟踪、余量和频率同步数据表

2021-04-22 17:10:08 8

8 对于一个设计项目来说,全局时钟(或同步时钟)是最简单和最可预测的时钟。只要可能就应尽量在设计项目中采用全局时钟。FPGA都具有专门的全局时钟引脚,它直接连到器件中的每一个寄存器。这种全局时钟提供器件中最短的时钟到输出的延时。

2021-04-24 09:39:07 5827

5827

LTM4618:6A带跟踪和频率同步功能的DC/DCμ模块(电源模块)稳压器数据表

2021-04-27 13:01:56 11

11 LTM4608:8A,低VIN DC/DCµ模块(电源模块),带跟踪、余量、多相和频率同步数据表

2021-05-13 16:22:50 1

1 对MIMO-OFDM系统来说,时间同步方面,接收端需要对各个天线上的信号分别进行延时估计和调整。频率同步方面,接收端需要对各个天线上的信号分别进行频率偏移估计和补偿。传统的MIMO-OFDM同步算法

2021-06-17 16:34:29 2266

2266

同步,从字面意思上看,是指两个或两个以上随时间变化的量在变化过程中保持一定的相对关系。到底是怎么样的相对关系呢?一般根据关系的紧密程度分为“频率同步”和“相位同步”这两个级别。频率同步是指两个基站

2021-09-28 15:43:23 7417

7417 SyncE。同步以太网通过从串行数据码流中恢复出发送端的时钟,从而实现网络时钟同步。但SyncE不能提供时间同步。IEEE1588v2是统一提供时间同步和频率同步的方法,能适合于不同传送平台的时频传

2022-01-15 14:35:31 2389

2389 晶振频率是晶体振荡器的固有频率,而时钟频率是以时间为准的振荡频率,一个时钟周期等于两个振荡周期,所以晶振频率等于2倍时钟频率。那么这两个频率之间有什么区别?

2022-01-29 16:57:00 9435

9435 CDC(不同时钟之间传数据)问题是ASIC/FPGA设计中最头疼的问题。CDC本身又分为同步时钟域和异步时钟域。这里要注意,同步时钟域是指时钟频率和相位具有一定关系的时钟域,并非一定只有频率和相位相同的时钟才是同步时钟域。异步时钟域的两个时钟则没有任何关系。这里假设数据由clk1传向clk2。

2022-05-12 15:29:59 1334

1334 业界首款 20-A 和 30-A 同步 DC/DC 降压转换器具有频率同步功能,可实现低噪声和降低的 EMI/EMC,以及用于自适应电压调节 (AVS) 的 PMBus 接口。

2022-08-29 09:25:09 430

430 本文描述了在以太网络上时钟频率同步特性的需求和技术关键点以及华为数通CX产品的实现。

2022-10-24 15:31:37 0

0 工作频率,这确实是一个很重要的方法,今天我想进一步去分析该如何提高电路的工作频率。 我们先来分析下是什么影响了电路的工作频率。 我们电路的工作频率主要与寄存器到寄存器之间的信号传播时延及clock skew 有关。在 FPGA 内部如果时钟走

2022-11-16 12:10:02 713

713 该电路是一款具有频率同步功能的高压、高效率、开关模式电池充电器。该电路适用于对谐波发射敏感的电池供电应用。

2023-01-11 10:01:35 529

529

本节介绍小功率同步电机的基本概念本节介绍永磁式、磁阻式、磁滞式同步电机的结构、原理、机械特性、优缺点本节介绍电磁减速同步电机的结构、原理文章

主要作为发电机运行(绝大部分电都是由同步发电机发出来

2023-03-28 09:58:04 0

0 提供时间同步和频率同步的方法,能适合于不同传送平台的时频传送,既可以基于1588v2的时间戳以基于分组的时间传送(TOP)方式单向传递频率,也可使用IEEE1588v2的协议实现时间同步。

2023-03-30 09:38:09 908

908

时钟信号的同步 在数字电路里怎样让两个不同步的时钟信号同步? 在数字电路中,时钟信号的同步是非常重要的问题。因为在信号处理过程中,如果不同步,就会出现信号的混淆和错误。因此,在数字电路中需要采取一些

2023-10-18 15:23:48 771

771 fpga与dsp通讯怎样同步时钟频率?dsp和fpga通信如何测试? 在FPGA与DSP通讯时,同步时钟频率非常重要,因为不同的设备有不同的时钟频率,如果两者的时钟频率不同步,会导致通讯数据的错误

2023-10-18 15:28:13 1060

1060 。 一、频率同步 在传送网中,频率同步是指网络中的各个节点之间的时钟频率保持一致,以便实现数据传输的精确同步。在频率同步的实现过程中,一般采用以下两种方法: 1.1. 时钟信号同步 传送网中的设备一般都有自己的时钟源,通过时钟

2024-01-16 14:42:48 228

228 USB设备之间是怎么同步时钟的?是所有USB设备的时钟频率都是一致的吗? USB设备之间的时钟同步是通过USB协议中的帧同步机制实现的。USB设备的时钟频率并不一定完全一致,但是USB协议通过

2024-01-16 14:42:52 485

485 晶振频率和时钟频率本质上有何区别呢?时钟频率有什么作用? 晶振频率和时钟频率是两个相关但又有所不同的概念。下面我们将逐一介绍这两个概念的含义、区别和作用。 首先,我们来了解晶振频率。晶振是一种

2024-01-24 16:11:35 307

307

正在加载...

电子发烧友App

电子发烧友App

评论