我们在设计和使用各种开发板卡时都会遇到各种扩展接口类型,近日Opal Kelly公司宣布推出SYZYGY开放式I/O接口标准,它是在成本和性能都介于Pmod接口连接器和FMC接口连接器之间的一种接口类型

2017-10-10 09:13:14 5905

5905 VIRTEX-5 - DC and Switching Characteristics - Xilinx, Inc

2022-11-04 17:22:44

嗨, 我使用LUT在Virtex-5 FPGA中编写用于环形振荡器的代码(不涉及顺序逻辑)。我将环形振荡器输出直接连接到FPGA输出LED引脚,观察振荡器上LED的波形。我观察到环形振荡器的波形是纯

2019-04-02 13:21:08

Virtex-5 OpenSPARK快速入门手册下载区http://www.winanycom.com/html/support/download.shtml[此贴子已经被作者于2010-2-24 9:54:38编辑过]

2010-02-24 09:50:47

Virtex-5 SXT系列中正常工作?我还仔细检查了我的引脚,结果发现我没有将Bank0 RSVD线连接到GND。这会导致问题吗?

2020-06-03 12:00:54

大家好,我正在研究包括3个不同时钟域的设计。我已经阅读了这个帖子,我发现与virtex-II和virtex-4相比,virtex-5在MTBF中是最差的。对于较低和实用的MTBF,我没有在同步器链

2020-06-12 09:27:03

嗨,我一直在Virtex-5上使用系统监视器一段时间,我只是想知道系统监视器本身的功耗是多少?我试图将它与一些基于RO的功率测量方法进行比较,所以如果有人知道实际的统计数据将是一个很大的帮助。谢谢,HX

2020-07-08 07:36:41

)Init_B没问题。CE_N很低,比较高BUSYs最初很高,然后继续保持低位。M [2:0} = 100。PROGAM_B很高(3.3V)。CCLK是FPGA的2MHZ。FPGA / PROM的设置符合Virtex-5 FPGA配置用户指南的图2-7。你有什么建议吗?

2020-05-27 13:35:05

如题,求virtex-5 XF5VLX330的电源配置解决方案

2013-01-06 17:04:00

喜 我正在使用xcv5sx95t,我正在使用一个时钟速度为150mhz的qdr ram作为我的记忆,这个界面我想从外部给一个150 mhz的时钟到virtex-5,以便与其他设备正确同步(而不是

2020-06-03 14:24:38

嗨,我刚刚开始学习VHDL,我正在一个在FPGA上实现TDC的项目。我有很多问题,我在这里写了一些。virtex-5能支持NIM信号还是TTL?我在数据表中看到我可以使用LVTTL,但我可以使用TTL吗?提前致谢。begar。

2020-06-19 08:55:56

Stratix III FPGA与Xilinx Virtex-5的体系结构对比Stratix III FPGA与Xilinx Virtex-5的性能对比

2021-05-07 07:00:14

嗨,出于移植和维护的原因,我需要安装Xilinx ISE 10.1 Foundation,完全支持所有FPGA,尤其是Virtex-5 XC5VFX70T。我有这个版本的有效许可证(即注册ID)但我

2018-11-15 11:30:24

为什么推出Virtex-5LXT FPGA平台和IP解决方案?如何打造一个适用于星形系统和网状系统的串行背板结构接口FPGA?

2021-04-29 06:18:31

关于Virtex-5 FXT平台的知识点看完你就懂了

2021-05-06 06:48:57

各位前辈好!我在用Xilinx Virtex5 FPGA做通过千兆网和上位机通信,有几个问题想请教:1、tri-mode ethernet mac 和 virtex-5 embedded

2016-05-31 22:41:53

嗨,我可以在Virtex-5的任何片中实现CFGLUT5原语,还是仅限于SLICE_M中的LUT?谢谢,Hooman

2020-05-28 06:32:38

使用xilinx xps-edk 12.4和virtex-5板(xupv5-lx110t).................!感谢致敬....................以上来自于谷歌翻译以下为原文

2019-02-28 13:38:14

我有两张标有“Vivado Design Suite 2013.2”和“ISE Design Suite 14.6”的光盘,我之前在Virtex-5设计上使用过Win7。最近将操作系统

2018-12-29 13:53:01

没有使用启动mig,任何人都可以给我一个关于virtex-5中ddr2的mpmc约束的例子吗?

2019-11-07 09:50:13

在VIRTEX-5 fpga中使用LVDCI端接时,添加50欧姆电阻(VRN和VRP)的目的是什么?如果没有连接特定的电阻会有什么影响?

2020-06-11 08:49:19

嗨,我正在开发一个项目,我们正在使用Virtex-5 FPGA从ADC捕获信号,样本存储在128K x 256 SRAM上,数据样本由PC采集。我相信Virtex-5为BRAM提供了一个选项,虽然我

2020-06-17 11:31:47

PCIe是什么?有什么核心优势?Xilinx的PCIe端点模块的显著优势包括哪些?基于Virtex-5 LXT FPGA的PCIe端点该怎样去设计?

2021-05-26 06:39:11

回避的挑战。为了应对串行背板设计中的这一系列挑战,Xilinx推出了Virtex-5LXT FPGA平台和IP解决方案。串行背板解决方案面向串行背板应用的Xilinx Virtex-5LXT FPGA

2019-04-12 07:00:11

不可回避的挑战。为了应对串行背板设计中的这一系列挑战,Xilinx推出了Virtex-5LXT FPGA平台和IP解决方案。 串行背板解决方案面向串行背板应用的Xilinx Virtex-5

2019-04-16 07:00:07

与 ISERDES 模块中的系统时钟 (CLK0) 保持同步。读数据通路包括两个阶段:读数据采集和读数据重新采集。两个阶段均在各个 Virtex-5 I/O 的内置 ISERDES 中实现。途经

2019-04-22 07:00:07

嗨....我正在使用Virtex-5板来学习。我想编程到SPI Flash M25P80型号。板上有一个SPI程序头模块,该模块有七个引脚:INIT,TMS,TCK,TDI,TDO,GND,VCC。我的问题是什么意思是INIT Pin?以及如何连接INIT引脚?谢谢.....

2020-06-19 07:57:21

大家好,我正在使用DMC为LX50T Virtex-5内的触发器生成时钟。我在CLKIN和CLKO之间有一个很大的延迟,即DCM内的Feddback延迟元件无法调整。这个器件的两个时钟(CLKIN

2020-06-16 14:04:42

嗨, 我使用的是Virtex-5 FPGA,DDR2 MIG,我的ISE版本是13.2。 我的phy_init_done信号没有被断言。我发现校准序列卡在阶段2.阶段3从未到达。请提供有关上述原因的信息?

2020-06-15 11:52:03

如何利用Virtex-5器件去实现QDR II SRAM接口?

2021-04-30 06:02:32

如何利用Virtex-5系统监控器加强系统管理和诊断?

2021-04-29 06:28:56

。依托于国家“863”计划Gbps 无线传输关键技术与试验系统研究开发项目,我们究竟该如何利用Virtex-5 FPGA设计Gbps无线通信基站?

2019-08-07 07:05:49

根据Virtex-5用户指南:扩展LVDS提供更高的驱动能力和电压摆幅(350-750),但如何实现扩展LVDS而不是通用LVDS。非常感谢。

2020-05-27 11:38:18

我在Virtex-5上使用了三个GTP磁贴,并且每个磁贴上的每个收发器都有来自所有用户时钟,有很多时钟耗费了大量的DCM和BUFG。由于这三个GTP磁贴都是从相同的MGTREFCLK引脚驱动的(彼此

2020-06-16 07:51:39

嗨......任何人都可以指导我如何将Virtex-5 I / O引脚用于差分对输入???在这种情况下如何终止发射器和接收器????我必须使用Verilod HDL编写代码。等待回应..以上

2019-02-14 13:05:41

嗨,关于Virtex-5与具有LVDS DDR信令的并行高速ADC接口的任何应用说明。我担心数据偏斜,因此需要静态和动态相位对齐。最接近的appnote是xapp860,但它不使用并行源,更像

2020-06-19 06:48:36

嗨,大家好,我是Xilinx的新手,我有兼容性问题,我已经安装了完整许可证的ISE系统构建器,但我在设备列表中找不到Virtex-5。我的问题是,如果我能够将此软件与旧设备一起使用,如果是,那么我如何将Virtex-5板添加到设备列表中。谢谢。萨利姆。

2020-03-16 06:56:52

您好,我想将SPANSION S29GLxxxPflash连接到VIRTEX-5,以便在BPI模式下加载比特流。有没有像xapp973,forSPANSION S29GL-P这样的指南?或者有人有示意图?

2020-06-01 06:27:48

我有Xilinx XUPV5-LX110T评估平台。现在我需要Virtex-5 XC5VLX110T(FF1136 / FFG1136)引脚排列,但在打开此地址后:http

2019-10-25 09:17:18

大家好,我使用带有virtex-5 xc5vsx95t的sundance板。当我尝试构建我的设计时出现以下错误。地址:543 - 由于放置限制,无法放置以下5个组件。组件的相对偏移显示在组件名称旁边

2020-05-27 16:58:18

嗨我正在寻找两个应用笔记-Virtex-5 SEU关键位信息:扩展Virtex-5 SEU控制器和新一代Virtex-5SEUController的能力,但我找不到它们。有没有人见过他们?请帮助

2020-06-15 09:47:18

数据表中未给出virtex-5 FPGA的输出负载电容。任何人都可以让我知道在哪里找到它?

2020-06-19 07:02:26

亲爱的专家我想知道有必要使用microblaze来使用Virtex-5以太网mac包装器核心吗?Furthr我无法获得什么是以太网mac配置寄存器?等待回复!

2020-06-10 16:03:34

亲爱的朋友们,我正在研发Virtex-5 ML510主板。对于我的项目,我需要应用差分时钟,这在ML510板上是不可用的。所以任何人都可以建议我使用哪个时钟发生器,我应该买正确的工作。感谢致敬,桑杰库马尔

2020-06-11 15:55:35

对于XQR5VFX130空间级virtex-5 fpga,可以使用2个XQF32P完成配置。但它似乎已经过时了。有没有相应的?或者配置的替代方法是什么?

2020-06-19 13:58:13

Virtex-5 - 通过DRP动态重新配置DCM的地址和值是什么?我有PLL的电子表格,但没有DCM的电子表格。

2020-06-16 16:25:11

在UG191(Virtex-5配置用户指南,第135页)中,它显示“帧从左到右编号,从0开始。对于每个块,除时钟列外,编号为0到25的帧访问该列的互连这是否意味着编号为26到35的帧是SRL或

2020-06-16 16:36:58

有人可以请我参考可以与ML505板上的Virtex-5一起使用的散热器/风扇吗? (部件号/供应商/数据表)这些是提到可以使用的“煎饼扇”的一些文件,但没有给出部件号。ML505 / 506 SGMII设计创作ML505 / 506/507概述和设置

2019-08-16 10:08:54

UG190 Virtex-5 用户指南

2008-07-28 15:46:50 65

65 Xilinx公司的Virtex-5 FXT FPGA器件在业界率先集成了嵌入式PowerPC 440处理器模块、高速RocketIO GTX收发器和专用XtremeDSP 处理能力。作为65nm Virtex-5系列的第四款平台,Virtex-5 FXT提供了极高的

2009-11-24 11:17:22 32

32 赛灵思宣布开始向市场交付针对高性能数字信号处理(DSP)而优化的65 nm Virtex-5 SXT现场可编程门阵列(FPGA)器件的首批产品。SXT平台创造了DSP性能的行业新纪录--550MHz下性能达352 GMAC

2009-11-28 14:08:02 23

23 Virtex-5, Spartan-DSP FPGAs Application Note

This application note demonstrates how efficient

2010-03-08 09:47:48 71

71 Virtex-5 Embedded Tri-Mode Ethernet Core应用手册

This application note describes a system using

2010-05-13 13:51:18 44

44 引言

本文探讨在Virtex-5 FPGA中实现设计的一些难题,然后用一个项目作为示范来详解充分利用其功能集的

2010-11-12 09:44:40 827

827

摘要:数字融合在当今信息时代是对数字信号处理的渴求,因而需要提高数字信号处理的性能。本文介绍了数字信号处理的Virtex-5 SXT解决方案,并对三个示例进行分析。 关键词:数字信号处理,数字融合,Virtex-5 SXT

2011-02-27 14:24:13 37

37 Virtex-5 FPGAs are available in -3, -2, -1 speed grades,with -3 having the highest

2011-08-04 14:32:51 30

30 Xilinx Virtex-5 SXT FPGA 平台提供了独特的单芯片解决方案,充分利用大规模并行计算达到超高性能,同时将功耗降到最低。

2011-08-20 15:22:35 994

994

为了解决下一代无线通信基站中多天线(MIMO)信号处理所带来的巨大数据吞吐量要求,本文基于Virtex-5 FPGA的GTP单元给出了一种在高级电信计算架构(ATCA)机箱内实现单对差分线进行3.125Gbps串

2011-08-25 10:37:12 1001

1001

本文基于Virtex-5 FPGA的GTP单元给出了一种在高级电信计算架构(ATCA)机箱内实现单对差分线进行3.125Gbps串行传输的设计方案。

2011-09-16 09:52:19 1733

1733

Virtex-5 系列可提供 FPGA 市场中最新最强大的功能。Virtex-5 系列采用第二代高级芯片组合模块 (ASMBLTM) 列式架构,包含 5 个截然不同的平台(子系列),是 FPGA 系列中选择最为丰富的系列

2012-01-17 15:11:06 7

7 由于Virtex-5 器件的基础架构与以往的FPGA 器件不同,因此,要为特定设计选择合适的Virtex-5 器件并非易事。大多数情况下,设计应采用类似的阵列大小(器件数量)并且比以前的目标器

2012-01-17 17:36:22 33

33 Virtex-5 器件包括基于第二代高级硅片组合模块 (ASMBL) 列架构的多平台 FPGA 系列。集成了为获得最佳性能、更高集成度和更低功耗设计的若干新型架构元件,Virtex-5 器件达到了比以往更高

2012-02-17 14:39:56 51

51 xilinx virtex-5 技术参数 供芯片选型之用

2015-11-30 17:44:45 1

1 Opal Kelly公司总部位于俄勒冈州波特兰的 Opal Kelly 公司专门从事基于FPGA的USB模块开发,曾大量推出基于赛灵思 FPGA的USB模块,比如:基于Virtex-5 FPGA

2017-02-16 17:42:39 1315

1315 (GbE)),为设计面向计算机和数据处理市场的低成本、高性能产品创造了可能性。Xinlinx Virtex-5 现场可编程门阵列 (FPGA) 系列,为设计具备更强功能和更低功耗的片上系统 (SoC) 解决方案奠定了基础。 Virtex-5 架构具有一系列关键特性,能够大大简化 TCP 和

2017-11-06 11:17:53 2

2 本文探讨在Virtex-5 FPGA中实现设计的一些难题,然后用一个项目作为示范来详解充分利用其功能集的技法。设计过程包括几个步骤,从针对应用选择适合的Virtex-5开始。为便于本文叙述,我们假定IP模块已经过汇编,并且已经就绪备用或已经用CORE Generator生成。

2017-11-24 20:40:51 1126

1126

SelectIO™技术相结合,能够让用户与各种网络设备进行连接。Virtex-5器件中,以太网MAC 模块作为一个硬件块集成在FPGA内部。

2018-07-22 09:28:00 2384

2384

该电源被设计成为Xilinx、Virtex-5、LXT和FXT平台中的收发器提供电源。

2018-05-18 16:30:10 11

11 该电源被设计成为Xilinx、Virtex-5、LXT和FXT平台中的收发器提供电源。

2018-05-18 16:33:58 13

13 virtex-5系列提供了fpga市场上最新最强大的功能。使用第二代asmbl™(高级硅模块化块)基于列的架构,virtex-5系列包含五个不同的平台(子系列),这是所有fpga系列提供的最多

2019-10-21 08:00:00 26

26 Genesys Virtex-5 FPGA开发板集成了功能强大的Xilinx Virtex®-5 FPGA,为广大用户带来了一个功能强大、方便实用的设计平台。板上还有千兆以太网,高速内存,高分辨率

2019-11-14 17:01:37 3832

3832

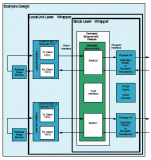

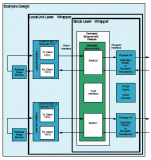

了SDRAM、Flash、SSRAM,电源以及大量I/O。通过OPAL KELLY公司的FrontPanel软件以及API可以实现模块控制。XEM3050可以用在逻辑量繁重的器件到计算机的集成,如图像捕获和信号处理,数据采集以及数字通信。

2020-08-30 08:49:00 643

643 Virtex-5 RocketI0TM GTP是Xilinx公司根据高速串行接口开发市场对高性能GTP的特殊要求而开发的一款具有通用性、易用性、低功耗和低成本特性的GTP收发器。文章针对

2021-06-24 16:10:42 2510

2510

基于直流和开关特性的Virtex-5 FPGA产品介绍

2021-07-12 14:11:09 18

18

电子发烧友App

电子发烧友App

评论