DSP+FPGA部分 FPGA + DSP结构,DSP采用TMS320C6455,FPGA采用XC5VSX95T-1FF1136T具备CPCI接口,PCI为32bit 33MHzDSP具有千兆网络DSP

2014-06-24 14:01:53

公司的 RapidIO Switch; DSP之间通过 RapidIOX4互联,Hyperlink X4 互联,SGMII互联,每片DSP外挂 1GB DDR3 ,32MB Nor Flash

2015-09-22 16:09:34

公司的Spartan XC3S200AN 配置芯片;一片 IDT 公司的 RapidIO Switch; DSP之间通过 RapidIOX4互联,Hyperlink X4 互联,SGMII互联,每片

2015-05-15 17:34:08

RapidIO X4 EDMA 中断 数据传输。 5) FPGA 完整的 DDR2控制、网络数据收发传输。 6) FPGA Rocket 光纤数据传输测试程序。 7) DSP与FPGA的RapidIO

2015-05-19 17:34:31

TMS320C6678芯片,支持DDR3, Nor Flash, 以太网接口,DSP之间通过HyperLink互联。DSP 的TSIF1外接连接器。 3) FPGA部分支持8路光纤 2.5Gbps

2015-09-17 14:38:59

TMS320C6678芯片,支持DDR3, Nor Flash, 以太网接口,DSP之间通过HyperLink互联。DSP 的TSIF1外接连接器。 3) FPGA部分支持8路光纤 2.5Gbps 输入输出

2015-09-11 16:55:46

一、板卡概述 板卡由我公司自主研发,基于VPX架构,主体芯片为两片 TI DSP TMS320C6678,两片Virtex-6 XC6VSX315T-ff1156 FPGA,1个RapidIO

2014-05-30 11:36:40

RapidIO X4 EDMA 中断 数据传输。 5) FPGA 完整的 DDR2控制、网络数据收发传输。 6) FPGA Rocket 光纤数据传输测试程序。 7) DSP与FPGA

2015-05-11 17:14:29

RapidIO X4 EDMA 中断 数据传输。 5) FPGA 完整的 DDR2控制、网络数据收发传输。 6) FPGA Rocket 光纤数据传输测试程序。 7) DSP与FPGA的RapidIO

2015-09-14 11:56:15

RapidIO X4 EDMA 中断 数据传输。 5) FPGA 完整的 DDR2控制、网络数据收发传输。 6) FPGA Rocket 光纤数据传输测试程序。 7) DSP与FPGA的RapidIO

2015-09-18 15:24:37

各出一个千兆网口,另外2个网络连于背板。前面板FPGA出两个千兆网口,6个SFF模块光纤,支持5Gbps前面板出4个指示灯,1个复位按钮。DSP与FPGA之间 RapidIOX4互联,DSP的Uart

2015-05-14 17:56:53

各出一个千兆网口,另外2个网络连于背板。前面板FPGA出两个千兆网口,6个SFF模块光纤,支持5Gbps前面板出4个指示灯,1个复位按钮。DSP与FPGA之间 RapidIOX4互联,DSP的Uart

2015-09-11 16:11:46

各出一个千兆网口,另外2个网络连于背板。前面板FPGA出两个千兆网口,6个SFF模块光纤,支持5Gbps前面板出4个指示灯,1个复位按钮。DSP与FPGA之间 RapidIOX4互联,DSP的Uart

2015-09-15 15:34:38

大家好,我现在在画一块28335的板子,想实现与FPGA之间的通信,但是不知道该怎样设计,包括FPGA与DSP连接的引脚、通过内部什么模块实现数据通信,现在一头雾水,请大家帮忙。谢谢。

2018-12-03 15:55:34

DSP代码大部分使用C语言编写,实现了所需的功能,现在想移植到FPGA板子上,不知道该怎么办?需要全部转换Verilog代码吗?有没有简便一点的方法。。。

2015-01-23 13:35:51

用的贵公司的TL138F-EVM A2开发板。想利用SPI协议实现FPGA和DSP通信。看了核心板引脚说明 没有看到FPGA这边SPI协议要用的接口,是不是这块板子不能实现DSP和FPGA的SPI通信。麻烦床龙工程师指导下。还有其他方法吗?

2020-04-24 06:46:47

本人刚入门FPGA,不知道如何实现FPGA+DSP,FPGA+ARM接口设计,网上查询有的说FPGA+DSP可以通过EMIF,IP核实现,FPGA+ARM可以通过SPI,有没有具体硬件参考的?

2016-08-27 11:30:26

各位高手,小弟想实现FPGA下的网络数据包抓取,应该怎么实现?功能与Sniffer相似!

2013-01-22 06:54:09

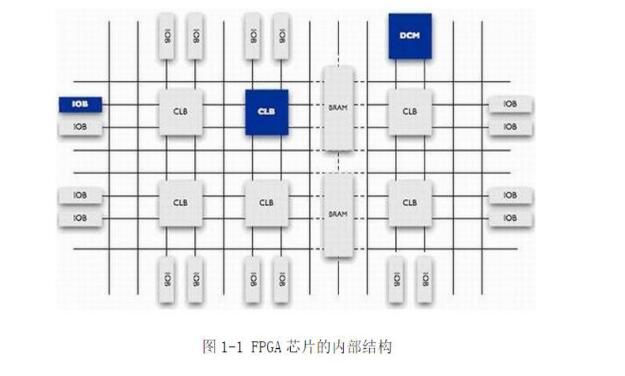

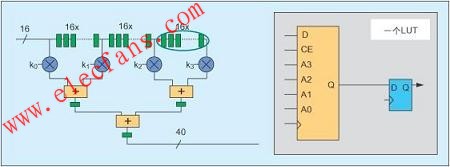

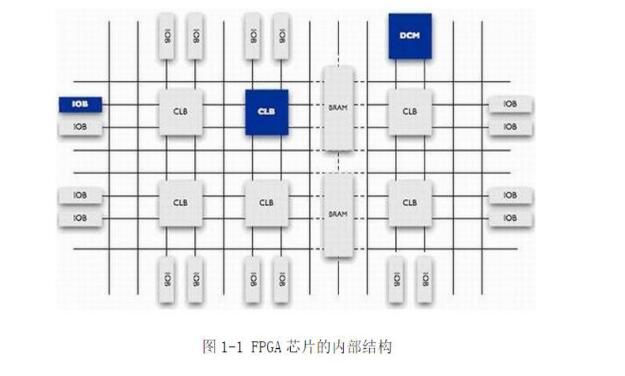

、功能多个角度解析两者的不同。1、FPGA与DSP的特点FPAG的结构特点片内有大量的逻辑门和触发器,多为查找表结构,实现工艺多为SRAM。规模大,集成度高,处理速度快,执行效率高。能完成复杂的时序

2019-05-07 01:28:40

和比较,并给出了FPGA与这两种DSP芯片进行链路口通倍的具体方法。在FPGA内部实现了DSP链路口的设计,同时给出了DSP进行链路口通信的具体设置方法。由于实时处理中数据的重发会严重影响处理的实时性

2019-06-19 05:00:08

和比较,并给出了FPGA与这两种DSP芯片进行链路口通倍的具体方法。在FPGA内部实现了DSP链路口的设计,同时给出了DSP进行链路口通信的具体设置方法。由于实时处理中数据的重发会严重影响处理的实时性,故

2018-12-04 10:39:29

一般涉及到数字处理和逻辑控制都用DSP加FPGA实现,最近想用FPGA实现数字处理和逻辑控制,听搞通信的说多加几个门就可以了,数字处理时钟要求25MHZ,请高手指点一下。

2013-04-05 10:01:31

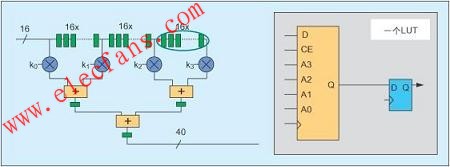

的数目之外,就是采用可编程逻辑器件,主要是FPGA芯片来实现。本课程以DSP设计在FPGA芯片上的开发为主线,遵照由浅入深的基本步骤和思路进行详细讲解,每一个知识点都给出了基于ISE(HDL语言

2009-07-21 09:22:42

FPGA实现和编程的一个方法是采用知识产权(IP)的模块或核心。例如,大多数标准DSP功能都在Xilinx库中以可参数配置的DSP核心的形式实现了,它们通过Xilinx公司的CORE生成器提供。包括

2011-02-17 11:21:37

FPGA设计之浮点DSP算法实现,DSP算法是很多工程师在设计过程中都会遇到的问题,本文将从FPGA设计的角度来讲解浮点DSP算法的实现。FPGA设计之浮点DSP算法实现是赛灵思工程师最新力作,资料不可多得,大家珍惜啊1FPGA设计之浮点DSP算法实现[hide][/hide]

2012-03-01 15:23:56

fpga+dsp 4路ad采集系统,you尝,rapidio pcieddr3 各种高速外围接口 代码有偿。qq2715957785

2018-02-24 08:34:21

本人使用virtex 5 与dsp c6678 srio通信,fpga是从模式,一直使用的1x。现在调试4x的时候遇到问题,4x会自动变成1x通信,或者:dsp成4x,fpga也训练成4x,但是此时

2018-06-21 00:10:20

DSP各出一个千兆网口,另外2个网络连于背板。前面板FPGA出两个千兆网口,6个SFF模块光纤,支持5Gbps前面板出4个指示灯,1个复位按钮。DSP与FPGA之间 RapidIOX4互联,DSP

2021-11-01 11:23:03

) 通过本地总线、RapidIO与DSP连接; 7) 提供主FPGA所有接口代码的封装库;DSP子系统规格 1) 选用TI公司8核DSP,型号TMS320C6678,工作主频1GHz; 2) 外挂1

2019-09-06 10:15:41

反复编程使用。DSP、FPGA芯片虽成本略微高于ASIC芯片,但具有货源畅通、可多次编程使用等优点。在中小批量通信产品的设计生产中,用FPGA和DSP实现HDLC功能是一种值得采用的方法。HDLC的帧

2011-03-17 10:23:56

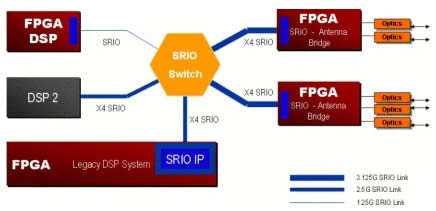

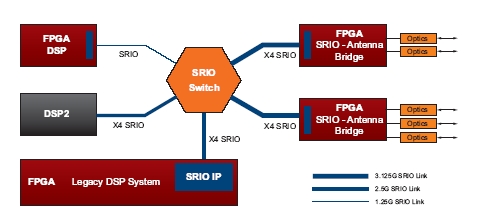

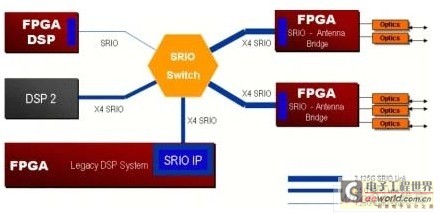

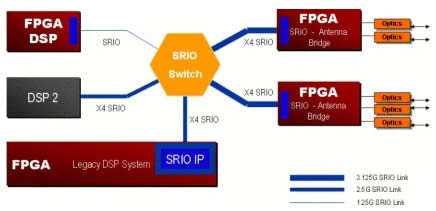

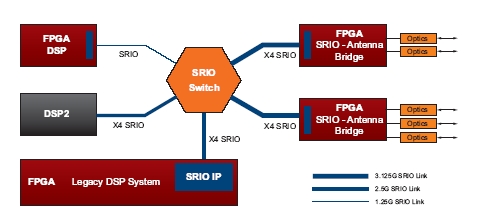

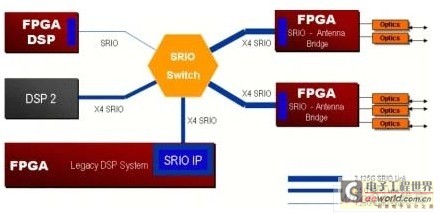

RapidIO正是满足这些要求的最佳选择。以无线基站为例,在SRIO出现之前,无线基站的基带处理的典型框图如图7所示。图7 传统无线基站基带处理框图在传统的基站中,DSP与ASIC或FPGA之间的互连一般用外部

2016-12-09 11:24:30

本人在北京工作7年以上,从事FPGA外围接口设计,非常熟悉Serial RapidIO协议,设计调试了多个基于Serial RapidIO接口的DSP和PowerPC信号处理卡.本人非常

2014-08-23 13:27:47

处理器的数目之外,就是采用可编程逻辑器件,主要是FPGA芯片来实现。本课程以DSP设计在FPGA芯片上的开发为主线,遵照由浅入深的基本步骤和思路进行详细讲解,每一个知识点都给出了基于ISE(HDL语言

2009-07-21 09:20:11

处理器的数目之外,就是采用可编程逻辑器件,主要是FPGA芯片来实现。本课程以DSP设计在FPGA芯片上的开发为主线,遵照由浅入深的基本步骤和思路进行详细讲解,每一个知识点都给出了基于ISE(HDL语言

2009-07-24 13:07:08

PowerPC,dsp和fpga实现,fpga负责接收E1口,K口等数据,通过dsp的mcbsp接口传输到dsp,进行话音编解码处理,然后通过HPI接口与PowerPC交互,或者通过dsp的网口直接收发数据。整个设备相当于一个路由器,它可以接入各种电台!

2015-09-10 11:15:14

容量

•FPGA 外挂2组FMC HPC 连接器;

•FPGA 引出1路QSPF+,数据速率25GbpsX4/s;

•FPGA与DSP之间通过RapidIO互联 。

•VPX 连接器上外接FPGA

2023-10-16 11:12:06

以上,从事FPGA外围接口设计,非常熟悉Serial RapidIO协议,设计调试了多个基于Serial RapidIO接口的DSP和PowerPC信号处理卡.本人非常熟悉Spartan-6

2015-11-11 15:06:39

随着通讯系统的数据处理量日益增大,过去总线形式的体系结构逐渐成为约束处理能力进一步提升的瓶颈。本文首先简单介绍了嵌入式设计中总线结构的演化过程,从而引出新一代点对点串行交换结构RapidIO。

2019-11-01 06:05:21

要跟上日益提高的性能需求,还得注意保持成本低廉有效利用基于串行RapidIO的FPGA作为DSP协处理器就能达到这些目的。那么,我们该怎么做呢?

2019-08-07 06:47:06

运算平台之间是如何连接的?SRIO系统的应用实例有哪些?如何利用串行RapidIO去实现FPGA协处理?

2021-04-29 06:17:59

本文讨论了一种基于RapidIO的具有双主机节点的嵌入式系统互联设计,给出系统设计方案及驱动软件设计,并在具体应用环境中对设计方案进行了系统验证。

2021-05-24 06:24:37

随着通讯系统的数据处理量日益增大,过去总线形式的体系结构逐渐成为约束处理能力进一步提升的瓶颈。本文首先简单介绍了嵌入式设计中总线结构的演化过程,从而引出新一代点对点串行交换结构RapidIO。

2019-09-02 07:10:22

视频图像方面,VGA格式和LVDS格式的视频图像叠加、旋转和缩放;3. 高低速接口方面,rapidIO、PCIE-DMA、10G以太网GTX、DDR3、SPI、UART、I2C、CAN接口,与DSP

2016-07-02 15:31:38

在雷达信号处理机的设计中,RapidIO接口可以可靠地实现芯片与芯片之间、板卡与板卡之间和系统与系统之间的高速低延迟通信,具有很大的应用前景。

2013-03-17 13:34:01

我在做fpga与dsp的SRIO通信,我用的是论坛上提供的SRIO test程序,目前dsp端能够实现端口0的外部回环测试。fpga端的协议还没做通,我想用dsp直接给fpga发包,fpga根据收到

2018-06-21 10:45:13

我们设计的系统里面需要实现DSP28377和ARM之间的高速互联,目前拟定的方案有双口RAM并行总线互联和SPI总线互联,请问还有其它高速总线互联方式吗?

2018-09-20 14:14:15

TI 相关技术支持专家 你们好 : 我在一个项目中使用了DM385 作为视频的解压缩方案,现在要将压缩后的视频流传输到fpga 基带,通过无线发送。想问一下,dm385 能不能通过u*** 实现互联

2020-08-18 07:03:22

Hi,Ti guys,我在使用自己板上的c6678,利用论坛上keystone_srio程序调试dsp和fpga端的通信。同事从fpga(v6,srio核)看来收发地址都是34卫的,但我调DSP互联

2018-12-28 11:08:14

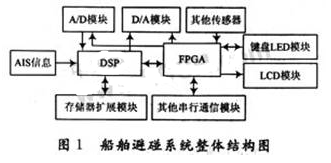

,数字控制信号经过 DA转换后输出模拟控制电压到后端控制电路,实现对七路温度的闭环控制。 4.FPGA与外围电路之间的通信接口 FPGA与外围电路之间的通信接口主要包括与温度传感器,DSP,232接口

2020-08-19 09:29:48

DSP芯片是专门为实现各种数字信号处理算法而设计的、具有特殊结构的微处理器,其卓越的性能、不断上升的性价比、日渐完善的开发方式使它的应用越来越广泛。将计算机网络技术引入以DSP为核心的嵌入式系统

2019-06-20 05:00:04

DSP芯片是专门为实现各种数字信号处理算法而设计的、具有特殊结构的微处理器,其卓越的性能、不断上升的性价比、日渐完善的开发方式使它的应用越来越广泛。将计算机网络技术引入以DSP为核心的嵌入式系统

2019-06-20 05:00:05

针对传统总线PCI存在的问题,提出异步FIFO存储转发模式的串行RapidIO-PCI转接桥方案,介绍RapidIO高速总线的体系结构及其性能优势,根据PCI和RapidIO协议,给出转接桥关键部分结构的设

2009-04-01 09:34:02 33

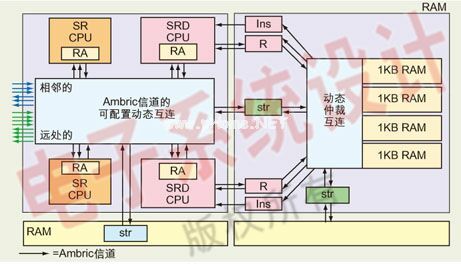

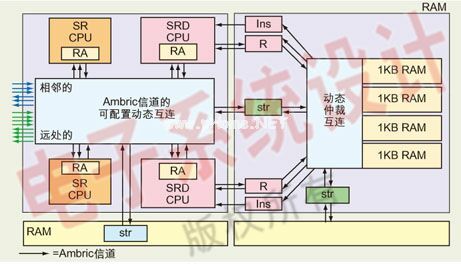

33 具有系统级性能的FPGA在半导体工艺的线宽达到深亚微米后更进一步按信号处理的要求改进器件结构和性能,不仅可实现VLSI DSP,且具有系统内可再编程的特性,可用流水和并行处

2009-05-09 12:57:35 16

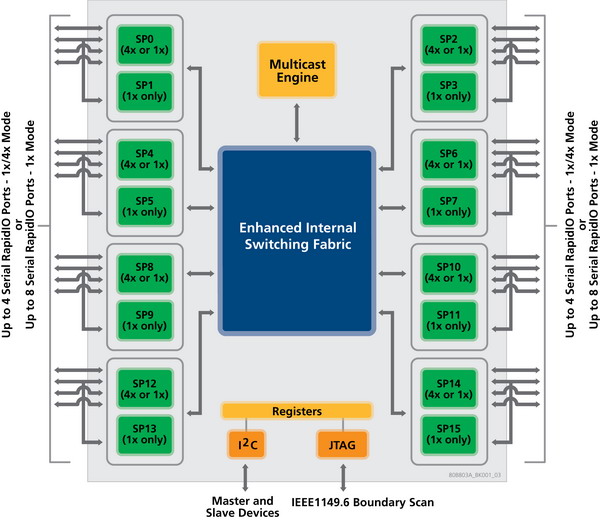

16 RapidIO 互连构架是一个开放的标准,可应用于连接多处理器、存储器和通用计算平台。本文简要介绍了基于Tundra 公司TSI568 芯片的RapidIO 交换模块的设计原理和实现方法,并对一些

2010-01-06 16:47:48 40

40 本文首先简单的介绍了总线的发展,从而引出一种新型的串行点对点交换结构RapidIO。DSP 在高性能处理系统中的重要性毋庸置疑,但是目前的很多DSP 并没有RapidIO接口。本文提出了

2010-01-25 14:25:19 32

32 FPGA实现DSP应用

摘要:具有系统级性能的FPGA在半导体工艺的线宽达到深亚微米后更进一步按信号处理的要求改进器件结构和性能,不仅可实现VLSI DSP,且具有系统

2010-04-01 15:39:54 14

14 FPGA的DSP应用

近年来由于多媒体技术和无线通信的发展,对DSP应用的要求不断地增长,但是这些应用对信号处理要求高,需要采用处理速度高的硬件来实现DSP,所以,随着CMOS工艺的

2010-04-07 14:25:58 16

16 用可再配置FPGA实现DSP功能

2010-07-16 17:56:43 10

10 比较了多种DSP芯片的互连性能,给出了一种简单高性能DSP网络结构。针对构成DSP网络通讯接口的链路口,分析其基本特点,并且提出了在FPGA中实现的设计原理。最后给出了设计仿真图和

2010-07-27 16:46:46 22

22 乘累加器在DSP算法中有着举足轻重的地位。现在,很多前端DSP算法都通过FPGA实现。结合FPGA具体的硬件结构,提出了乘累加器在FPGA中实现的改进方法:流水线技术、CSD编码、DA算法,

2010-08-06 14:41:38 29

29 分析当前高速互连网络中同时存在的TCP/IP, GAMMA, InfiniBand, SCI 等技术的实现机制,介绍RapidIO 高性能总线技术。研究RapidIO 协议和MPC8548 处理器的相关技术,提出在RapidIO 高速互连网

2010-09-22 08:35:11 20

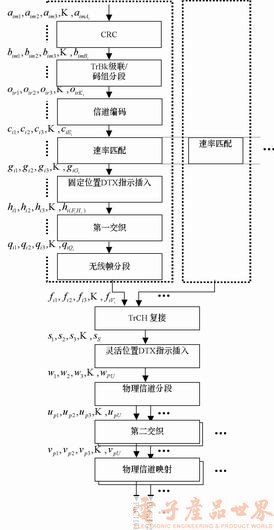

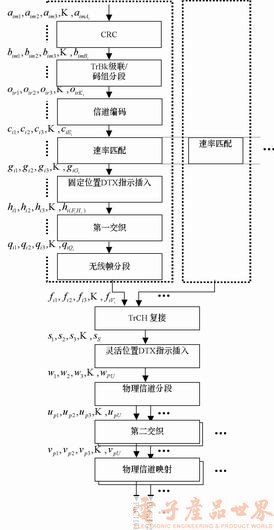

20 摘 要: 本文在分析WCDMA系统基带处理方案的基础上,结合DSP和FPGA性能的比较,提出了一种在性能、灵活性和性价比上都比较理想的DSP+FPGA基带发送的实现方案。 引言 随

2006-03-11 13:29:42 670

670

基于DSP和FPGA的通用图像处理平台设计

摘要:设计一种基于DSP和FPGA架构的通用图像处理平台,运用FPGA实现微处理器接口设计,并对图像数据进行简单预处理,利用DSP

2010-02-01 11:10:21 1379

1379

利用串行RapidIO实现FPGA协处理

为了支持“三重播放”应用,人们对高速通信和超快速计算的需求日益增大,这向系统开发师、算法开发师和硬件工程师等人员提出了新

2010-02-25 17:06:55 1216

1216

用RapidIO提高DSP阵列的性能

“采用SERDES(串行/解串器)技术后只需少量引脚就能获得很高的带宽。由于硬件全部承担了协议栈的处理,RapidIO减少了原来仅用于在系统中传

2010-03-01 10:36:39 1318

1318

串行RapidIO交换器的应用优势

EMIF6? 是由 Texas Instruments 开发的一款专利接口,在业内应用多年,反响良好。但是,EMIF6? 现正用于从未尝试的 DSP 至 DSP 连接等应用。本文

2010-03-03 15:54:10 795

795

采用串行RapidIO连接功能增强DSP协处理能力

目前,对高速通信与超快计算的需求正与日俱增。有线和无线通信标准的应用随处可见,数据处理架构每天都在扩展。较为普

2010-03-03 16:01:25 1134

1134

利用串行RapidIO实现FPGA协处理

为了支持“三重播放”应用,人们对高速通信和超快速计算的需求日益增大,这向系统开发师

2010-03-25 14:48:25 1389

1389

Spartan-3FPGA能以突破性的价位点实现嵌入式DSP功能。本文阐述了Spartan-3 FPGA针

2010-12-17 11:31:23 675

675

捅要:为了实现是弹武器瞄准自动化,本文设计了基于DSP和FPGA的高速高精确度双通道CCD图像采集系统,采用QUartuBn在AJtera的FPGA器件CYCLONEII上设计了CCD驱动时序电路,采用PsPICE设计了可以

2011-02-25 13:48:05 187

187 摘要:为了实现高速HDLC通讯协议,设计了DSP+FPGA结构的485通讯接口,接口包括DSP、FPGA、485转换等硬件电路,以及DSP与FPGA之间的数据交换程序和FPGA内部状态机;其中DSP用于实现数据控制,FPGA用于实现HDLC通讯协议,DSP与FPGA之间采用XINTF方式,通过双FI

2011-02-25 17:24:34 98

98 摘要:针对数控系统的工作特点和要求,通过对TI公司新推出的DSP芯片TMS320F2812和ALTERA公司的FPGA芯片EP1K30功能和特点的深入分析,给出了一种基于DSP和FPGA的运动控制卡的设计与实现。在充分考虑上述芯片特点和资源的基础上,该卡采用DSP和FPGA取代单片机

2011-02-27 13:29:19 104

104 【摘要】本文论述了FPGA在DSP应用上的优缺点,比较了FPGA芯片和DSP芯片之间的差别,介绍了解决隔阂的方案--Xtreme DSP软件包和平台级的Virtex Ⅱ芯片。最后,对Xtreme和VirtexⅡ芯片的特点进行了详细说明。 关键词:数字信号处理;可编程门阵列;芯片

2011-02-28 13:09:41 59

59 System Generator 工具由 MathWorks 与 Xilinx 合作开发而成,DSP 设计人员可使用 MATLAB 和Simulink 工具在 FPGA 内进行开发和仿真来完善 DSP 设计。 该工具为系统级 DSP 设计与 FPGA 硬件实现的融合起

2011-05-11 18:36:23 224

224 为满足导航系统设计的小型化、实时性要求,本文提出了一种基于FPGA + DSP 的实现方案。该方案的设计思路是:将FPGA 映射到DSP EMIF 的一段地址空间,并用FPGA 来完成多通道信号的采集; DSP 根

2011-09-13 14:32:08 77

77 该方案采用Altera公司的IP核和Cyclone系列FPGA,建立了串行RapidIO(SRIO)接口通信系统,并对其功能进行验证。详细分析了RapidIO应用系统及其验证模型的功能结构和运行原理,为提高嵌入式

2011-12-23 14:47:22 38

38 介绍了RapidIo总线的特点,以及RapidIo总线初始化过程中面临的系统网络结构探测和最短路径路由选择问题。针对该问题,本文研究了深度优先(DFS)网络拓扑探测方法在RapidIo总线枚举过

2013-03-13 16:15:14 74

74 基于FPGA和DSP的图像多功能卡的设计与实现

2016-09-22 12:32:08 28

28 DSP与FPGA高速的数据传输有三种常用接口方式: EMIF, HPI 和 McBSP 方式。而采用 EMIF 接口方式, 利用 FPGA ( 现场可编程逻辑门阵列) 设计 FIFO的接口电路,即可实现高速互联。

2017-02-11 14:16:10 2487

2487

基于FPGA和DSP网络单向时延测量系统设计与实现_唐旭

2017-03-19 11:38:26 0

0 基于FPGA的高速DSP与液晶模块接口的实现

2017-10-19 13:46:23 3

3 基于DSP的FPGA配置方法研究与实现

2017-10-19 16:15:19 36

36 摘要 利用异步FIFO实现FPGA与DSP进行数据通信的方案。FPGA在写时钟的控制下将数据写入FIFO,再与DSP进行握手后,DSP通过EMIFA接口将数据读入。文中给出了异步FIFO的实现

2017-10-30 11:48:44 1

1 出于以下几个原因,你可能会考虑使用FPGA来实现DSP解决方案。首先是为了提高性能,尽管今天的DSP处理器很快,并对许多DSP应用来说很有用,但仍有一些应用要求性能再进一步提升,而FPGA提供了更高

2017-11-06 11:47:52 0

0 结构,同时为满足大数据存储要求设计了可方便网络控制的数据存储模块。模块之间可以通过自定义LVDS接口实现互联,组成一个系统。

2017-11-17 06:11:40 2373

2373

本文首先分析了FPGA是否会取代DSP,其次介绍了FPAG结构特点与优势及DSP的基本结构和特征,最后阐述了FPGA与DSP两者之间的区别。

2018-05-31 09:51:25 35711

35711

高性能 DSP 上的串行 RapidIO 接口

2018-06-12 03:44:00 3784

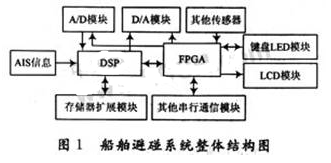

3784 的I/O功能,实现外围输入输出接口如其他串行口、ADC数据采集缓存等硬件电路,使部分数据采集和数据通信的I/O任务由DSP和FPGA协同承担,从而使DSP减轻负担,可以更专注于避碰的复杂算法。FPGA还可以实现

2020-05-13 07:57:00 1705

1705

某鱼雷声自导的硬件系统使用了百兆网络交换机实现DSP之间的互联。交换机在MAC和PHY之间的接I=I是RMII,但DSP没有相应的外围设备与它匹配。因此必须在FPGA中设计RMII的通讯模块,完成DSP数据格式向RMII数据格式的转化。在设计中将该通讯模块分为发送状态机和接收状态机两部分

2018-10-18 16:46:51 64

64 通过分析网卡基本通信过程控制和数字信号处理器( DSP)对网卡直接编程方法, 成功设计基于DSP的网络通程序,从而最终实现DSP系统数字化和网络化的融合。

2020-08-14 15:55:00 7

7 RapidIO交换芯片是一种基于RapidIO协议的专用交换芯片,它能够实现高速、低延迟的数据传输和交换,广泛应用于嵌入式系统、数据中心、网络通信等领域。RapidIO协议本身是一种基于包交换的互连技术,具有高速、高效、可靠等特点,因此RapidIO交换芯片在数据传输和交换方面具有很高的性能优势。

2024-03-16 16:40:09 1532

1532

电子发烧友App

电子发烧友App

评论