VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工业标准硬件描述语言,是随着可编程逻辑器件(PLD)的发展而发展起来的。它是一种面向设计、多层次的硬件描述语言,是集行为描述、RTL描述、门级描述功能为一体的语言,并已成为描述、验证和设计数字系统中最重要的标准语言之一。由于VHDL在语法和风格上类似于高级编程语言,可读性好,描述能力强,设计方法灵活,可移植性强,因此它已成为广大EDA工程师的首选。目前,使用VHDL语言进行CPLD/FPGA设计开发,Altera和Lattice已经在开发软件方面提供了基于本公司芯片的强大开发工具。但由于VHDL设计是行为级设计,所带来的问题是设计者的设计思想与电路结构相脱节,而且其在设计思路和编程风格等方面也存在差异,这些差异会对系统综合后的电路整体性能产生重要的影响。

在VHDL语言电路优化设计当中,优化问题主要包括面积优化和速度优化。面积优化是指CPLD/FPGA的资源利用率优化,即用尽可能少的片内资源实现更多电路功能;速度优化是指设计系统满足一定的速度要求,即用更多的片内资源换取更快的处理速度,常用于视频信号采集系统和通信系统之中。面积优化和速度优化通常是一对矛盾,一般情况下,速度指标是首要的,在满足速度要求的前提下,尽可能实现面积优化。因此,本文结合在设计超声探伤数据采集卡过程中的CPLD编程经验,提出串行设计、防止不必要锁存器的产生、使用状态机简化电路描述、资源共享,利用E2PROM芯片节省片内资源等方法对VHDL电路进行优化。

1 VHDL电路优化设计的方法

优化设计是可编成逻辑设计的精华所在,如何节省所占用的面积、如何提高设计的性能是可编成逻辑设计的核心,这两点往往也成为一个设计甚至项目成败的关键因素。下面结合超声探伤数据采集卡设计过程中,并基于Altera公司的EPM7192 CPLD芯片的编程经历来论述VHDL电路的优化方法。

1.1 采用串行设计代替并行设计

串行设计是指把原来单个时钟周期内完成的并行操作的逻辑功能分割出来,提取相同的功能单元,在时间上分时复用这些功能单元,在满足系统速度要求的前提下,用多个时钟周期来完成单个时钟周期即可完成的功能。

根据项目的要求,超声探伤数据采集卡要有5个模拟通道,每隔125μs就会采集到330个点。如果等5个超声通道采样结束后再进行数据处理和传输,几乎是不可能满足该超声探伤系统的实时性要求,而且数据量也远远超过ARM板上总线接口的传输速率2 MB/s。对于这么高的实时性要求,最好的解决办法是在CPLD内部进行数据压缩,即边采集边压缩,以满足系统使用的ARM板的总线速率要求。经过系统评估,每个超声通道只需保留一个最大值即可满足系统的性能要求。在这里,通过在三个8位数A,B,C中找出最大值的例子来说明串行设计方法的优势,代码如下所示。

程序一是用并行方法设计,而程序二是采用串行方法设计。从表1的实验数据可见,采用串行方法以后,电路的优化效果比较明显。优化前,程序一需要消耗38个宏单元(Micro Cell),一个时钟周期即可完成找最大值操作;优化后,实现相同的逻辑功能程序二仅需要12个宏单元,但需要3个时钟周期才能完成一次运算,优化率达68.4%。值得注意的是,此方法是以速度换取资源的方法,只适用于对速度要求不高的系统。

1.2 防止不必要锁存器的产生

在VHDL设计中,使用语句不当也是导致电路复杂化的原因之一,这使得综合后的电路当中存在很多不必要的锁存器,降低电路的工作速度。因此,在设计一个逻辑电路时,设计人员应该避免由于VHDL使用习惯的问题,无意识地在电路中添加不必要的锁存器。由于IF或者CASE语句较容易引入锁存器,所以当语句的判断条件不能覆盖所有可能的输入值的时候,逻辑反馈就容易形成一个锁存器。当然,随着高级编译软件的出现,如QuartusⅡ7.2,这样的问题通过编译软件已经得到很好的解决。对一个设计人员而言,有意识地防止不必要锁存器的产生可以加快编译速度。

在超声探伤数据采集卡VHDL程序设计当中,涉及10 MHz系统时钟clk的同步D触发器的设计,即每当clk时钟信号的上升沿到来时,将输入信号in的值赋给输出信号out,代码如下所示。

通过对比,程序四比程序三只多了一条空语句,但这样做可有效防止综合器生成不必要锁存器,并提高电路的工作速度。

1.3 使用状态机简化电路描述

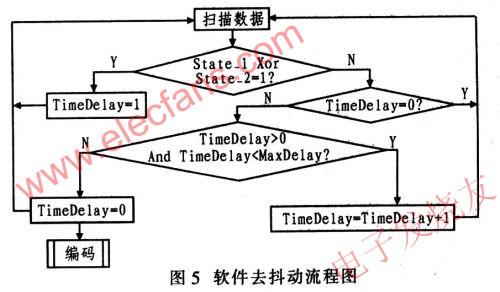

由于状态机的结构模式简单,有相对固定的设计模板,特别是VHDL支持定义符号化枚举类型状态,这就为VHDL综合器充分发挥其强大的优化功能提供了有利条件。因此采用状态机比较容易地设计出高性能的时序逻辑模块,在超声探伤数据采集卡的CPLD程序设计中,使用有限元状态机(FSM)设计CY7CA225 1K×16 b FIFO芯片的读写控制模块,并且达到很好的效果,逻辑转换图如图1所示。实践证明,实现相同的逻辑功能,使用状态机设计能使设计的电路得到更好的优化。

1.4 资源共享

资源共享的思想是通过使用数据缓冲器或多路选择器等方法来共享数据通道中占用资源较多的模块,如算法单元。通过共享电路单元模块可有效提高芯片内部资源的利用率,达到优化电路的目的。

1.5 利用E2PROM芯片节省片内资源

在用VHDL进行项目开发的过程中,经常需要存储一些配置参数值。理论上讲,每存储一个字节的配置参数需要使用8个CPLD宏单元,因此在CPLD内部存储这些参数并不是好的方案,除非使用的CPLD芯片已集成了E2PROM存储单元。例如,在设计超声探伤系统的数据采集卡的过程中,每个通道的采样数都需要保存在CPLD里面。由于项目初期芯片选型不当,选择一款EPM7192S160-15,该款芯片内部只有192个宏单元,因此考虑把参数存储在外扩的E2PROM芯片24WC02中。经实验证明,在CPLD内部实现一个I2C控制器仅需要43个宏单元。由此可见,当初始化参数大于5个的时候,通过外扩E2PROM芯片来存储配置参数是可行的,只需在CPLD/FPGA芯片内实现I2C控制器即可方便地读写E2PROM存储芯片。

2 结语

使用VHDL进行CPLD/FPGA电路设计时,要根据实际项目的具体情况,合理地划分项目功能,并用VHDL实现相应的功能模块。用模块来构建系统,可有效地优化模块间的结构和减少系统的冗余度,并在模块设计过程中始终贯彻以上的优化设计原则,借助于强大的综合开发软件进行优化,才能达到最优化电路的目的。

采用CPLD/FPGA的VHDL语言电路优化原理设计

- FPGA(591969)

- cpld(168088)

相关推荐

15份CCD驱动的文献资料合集(基于FPGA、CPLD设计与实现)

时序发生器的设计,基于CPLD和VerilogHDL语言的一种线阵CCD驱动时序电路的设计,基于CPLD和Verilog的高精度线阵CCD驱动电路设计,基于CPLD和VHDL的一种线阵CCD驱动时序电路

2019-06-03 16:45:25

CPLD/FPGA有哪些设计工具?

它们的基本设计方法是借助于 EDA 设计软件,用原理图、状态机和硬件描述语言等方法,生成相应的目标文件,最后用编程器或下载电缆,由 CPLD/FPGA 目标器件实现。 生产 CPLD/FPGA

2019-03-04 14:10:13

CPLD系统设计及VHDL语言的视频教程

各位好,请问哪里有免费下载的 CPLD系统设计及VHDL语言的视频教程?是天祥的。淘宝里有好多卖的,可是要淘宝帐户和钱呀?

2008-07-20 10:29:10

FPGA CPLFPGA CPLD 数字电路设计经验分享

FPGA CPLFPGA CPLD 数字电路设计经验分享FPGA/CPLD数字电路设计经验分享摘要:在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应

2012-08-11 10:17:18

FPGA|CPLD|ASIC学习书籍集锦【独家奉送】

7-5606-1132-X/TP·0574本书介绍了FPGA的相关基础知识, VHDL硬件描述语言,FPGA开发软件的使用;器件配置与调试;FPGA设计中的基本问题和电路设计实例等。 《CPLD

2012-02-27 11:31:10

FPGA与CPLD的区别

CPLD的电路规模、功能、性能等方面强化之后的产物。(特权同学版权所有)一般而言, FPGA与CPLD之间的区别如表1.1所示。(特权同学版权所有)表1.1 FPGA和CPLD的比较总而言之,FPGA

2019-02-21 06:19:27

FPGA与CPLD的概念及基本使用和区别

/O单元互连结构,可由用户根据需要生成特定的电路结构,完成一定的功能.由于 CPLD内部采用固定长度的金属线进行各逻辑块的互连,所以设计的逻辑电路具有时间可预测性,避免了分段式互连结构时序不完全预测

2020-08-28 15:41:47

FPGA中文VHDL语言基础教程

希望在今后的学习中大家多多帮助,先来几个基础的verilog 教材吧 现在我用到了FPGA关键分配的知识。 不过还是想系统的学习一下。那就先从软件的使用和语法开始学习吧。 完整的pdf格式文档电子发烧友下载地址(共31页): FPGA中文VHDL语言教程.pdf

2018-07-04 01:11:32

FPGA入门:Verilog/VHDL语法学习的经验之谈

算得上简单实用,但随着逻辑规模的不断攀升,这种落后的设计方式已显得力不从心。取而代之的是代码输入的方式,当今绝大多数的设计都采用代码来完成。FPGA/CPLD开发所使用的代码,我们通常称之为硬件描述语言

2015-01-29 09:20:41

FPGA实战演练逻辑篇3:FPGA与CPLD

CPLD的电路规模、功能、性能等方面强化之后的产物。(特权同学版权所有)一般而言, FPGA与CPLD之间的区别如表1.1所示。(特权同学版权所有)表1.1 FPGA和CPLD的比较总而言之,FPGA

2015-03-12 13:54:42

FPGA实现直接数字频率合成(DDS)的原理、电路结构和优化...

FPGA实现直接数字频率合成(DDS)的原理、电路结构和优化方法介绍了利用现场可编程逻辑门阵列FPGA实现直接数字频率合成(DDS)的原理、电路结构和优化方法。重点介绍了DDS技术在FPGA中的实现

2012-08-11 18:10:11

FPGA毕业论文选题大全

基于VHDL语言的数字钟系统设计 基于FPGA的交通灯控制 采用可编程器件(FPGA/CPLD)设计数字钟 数字锁相环法位同步信号 基于FPGA的码速调整电路的建模与设计 误码检测仪

2012-02-10 10:40:31

FPGA的VHDL有哪些优点?怎么理解VHDL?

VHDL 主要用于描述数字系统的结构、行为、功能和接口。除了含有许多具有硬件特征的语句外,VHDL 在语言形式、描述风格和句法上与一般的计算机高级语言十分相似。VHDL 的程序结构特点是将一项

2018-09-07 09:04:45

FPGA的学习与设计

FPGA的编程更偏向于硬件(Verilog VHDL)。一般的说,FPGA是一种数字系统,输入输出由编程内容确定。本课程将学习使用Quartus软件,采用Verilog HDL语言进行编程,来使得编程后

2017-10-24 14:59:23

cpld与flash配置fpga

用vhdl实现cpld配置fpga,配置成功后在usermode下设置一个重新配置信号,当信号有效时对fpga进行重新配置;fpga配置程序放在flash内;现在遇到的问题是,上电cpld能够正常配置fpga并且进入usermode ,但是加上重新配置语句过后就不能成功配置fpga,求高人指点~

2013-01-17 22:35:39

vhdl是什么

超高速集成电路硬件描述语言,主要是应用在数字电路的设计中。它在中国的应用多数是用在FPGA/CPLD/EPLD的设计中。当然在一些实力较为雄厚的单位,它也被用来设计ASIC。VHDL主要用于描述数字系统的结构

2015-09-30 13:48:29

采用高级语言开发FPGA的探索

门阵列)。本文主要探索CPU协同FPGA的异构计算方式。传统的FPGA开发方式是采用硬件描述语言Verilog/VHDL,开发难度高,为了在FPGA上实现类似CPU/GPU的开发运行体验, FPGA两大

2017-09-25 10:06:29

ALTERA FPGA/CPLD高配学习指南:入门和高级篇,教程十讲全集

大家熟悉在CPLD/FPGA 开发中一个关键的技术——状态机,并且简单介绍了一下RTL 视图的使用。第三讲:加/减计数器例程,讲解了计数器的VHDL 语言的设计过程,以及硬件下载的方法,并且可以通过

2020-05-14 14:50:30

[下载]天祥 十天学会CPLD FPGA VHDL视频教程(3.12G完整版)

,让大家熟悉在CPLD/FPGA开发中一个关键的技术——状态机,并且简单介绍了一下RTL视图的使用。 第三讲:加/减计数器例程,讲解了计数器的VHDL语言的设计过程,以及硬件下载的方法

2009-03-26 16:38:29

multisim12能不能进行FPGA/CPLD的VHDL仿真??

如题,multisim12能不能进行FPGA/CPLD的VHDL仿真??各位大神,multisim12到底能不能进行VHDL的仿真呢?看上multisim的直观,可惜好像不能使用里面的FPGA器件。。各种忧伤啊。。。。。求助。。。

2013-09-22 17:09:04

【下载】《CPLD/FPGA的开发与应用》

的边界扫描测试第5章 Xilinx Foundation应用基础第6章 Foundation高级应用第7章 VHDL语言简介第8章 CPLD/FPGA在数字系统设计中的应用第9章 CPLD/FPGA在通信

2018-03-29 17:11:59

【案例分享】玩转FPGA必学的复杂逻辑设计

,FPGA允许无限次的编程。(二)]FPGA的基础就是数字电路和VHDL语 言,想学好FPGA的人,建议床头都有一本数字电路的书,不管是哪个版本的,这个是基础,多了解也有助于形成硬件设计的思想。在语言

2019-08-11 04:30:00

【电子书】《CPLD_FPGA的开发与应用》PDF电子档

`CPLD、Spartan可编程器件的基础知识,VHDL语言基础,Foundation编辑工具使用,高级应用以及CPLD/FPGA在数字系统设计的应用。`

2021-04-06 11:43:55

双向数据转换器的VHDL程序设计

(专用集成电路)技术的不断完善,EDA(电子设计自动化)技术在现代数字系统和微电子技术应用中显示出了越来越重要的作用,而现代EDA技术的重要特征是采用了硬件描述语言,即VHDL描述。VHDL(Very High

2016-05-08 06:18:34

基于CPLD和FPGA的VHDL语言电路优化设计

其在设计思路和编程风格等方面也存在差异,这些差异会对系统综合后的电路整体性能产生重要的影响。在VHDL语言电路优化设计当中,优化问题主要包括面积优化和速度优化。面积优化是指CPLD/FPGA的资源

2019-06-18 07:45:03

天祥 十天学会CPLD FPGA VHDL视频教程(3.12G完整版)

自从天祥电子推出40小时的“十天学会单片机和C语言编程”视频教程后,受到了广大电子爱好者的好评,并希望我们能够赶紧推出“CPLD器件及VHDL程序设计”的视频教程,为了能够满足大家的要求,提供更多

2009-02-07 11:34:24

天祥十天学会CPLD/FPGA 系统设计全集

,同时包括编写后如何查找和修改错误。教程介绍:第一讲:主要讲解CPLD 系统开发的基本概念,介绍了CPLD 和FPGA 的各自特点、 生产厂家和相应的软件以及开发相关的硬件描述语言。以分频器为例,让

2012-09-29 21:32:44

如何采用CPLD/FPGA优化VHDL语言电路设计?

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工业标准硬件描述语言,是随着可编程逻辑器件(PLD)的发展而发展起来的。

2019-10-18 08:20:51

如何利用FPGA和VHDL语言实现PCM码的解调?

利用现场可编程门阵列(FPGA)和VHDL 语言实现了PCM码的解调,这样在不改变硬件电路的情况下,能够适应PCM码传输速率和帧结构变化,从而正确解调数据。

2021-05-07 06:58:37

学好VHDL的重要性-夏路易

淘汰的今天,作为一个电类专业的毕业生应该熟悉VHDL语言和CPLD、FPGA器件的设计,阎石教授新编写的教材也加入了VHDL语言方面的内容,可见使用VHDL语言将数字系统集成到一块集成电路中是现在

2009-10-22 15:44:59

怎么利用CPLD/FPGA的VHDL语言优化电路?

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工业标准硬件描述语言,是随着可编程逻辑器件

2019-08-28 08:05:46

怎么设计优化VHDL语言电路?

在语法和风格上类似于高级编程语言,可读性好,描述能力强,设计方法灵活,可移植性强,因此它已成为广大EDA工程师的首选。目前,使用VHDL语言进行CPLD/FPGA设计开发,Altera和Lattice

2019-08-08 07:08:00

有关FPGA开发语言VHDL和Verilog的疑惑

本人小菜鸟,开始学FPGA的时候学的Verilog语言,后来因为课题组前期的工作都是VHDL就该学VHDL了。最近听了几个师兄的看法,说国内用VHDL的已经很少了,建议我还是坚持用Verilog,小菜现在好纠结,请问到底应该用哪种语言呢?望各位大神指点!

2015-07-08 10:07:56

模拟IC设计与使用VHDL语言设计IC的区别

感觉模拟IC设计就应该是设计模拟电路.设计运放等,通过设计电路、在硅片上搭建TTL.CMOS......从而做成IC芯片;而我经常看到说IC设计就是使用VHDL语言设计IC,写好VHDL语言后烧录到FPGA.CPLD.......从而做成芯片。我想问的是这两者有什么区别?

2018-08-29 09:45:43

用FPGA/CPLD设计UART

),有时我们不需要使用完整的UART的功能和这些辅助功能。或者设计上用到了FPGA/CPLD器件,那么我们就可以将所需要的UART功能集成到FPGA内部。使用VHDL将UART的核心功能集成,从而使整个设计更加紧凑、稳定且可靠。本文应用EDA技术,基于FPGA/CPLD器件设计与实现UART。

2012-05-23 19:37:24

硬件描述语言VHDL课件

硬件描述语言VHDL课件 硬件描述语言VHDL 数字系统设计分为硬件设计和软件设计, 但是随着计算机技术、超大规模集成电路(CPLD

2008-09-11 15:47:23

详解CPLD/FPGA设计流程

只要有数字电路的基础,还是能较容易和快速地学会利用 CPLD/FPGA 设计数字系统的。 数字系统的基本部件比较简单,它们是一些与门、或门、非门、触发器和多路选择器等,宏器件是一些加法器、乘法器等

2019-02-28 11:47:32

vhdl语言教程下载

第1章 绪论 1.1 关于EDA 1.2 关于VHDL 1.3 关于自顶向下的系统设计方法 1.4 关于应用 VHDL的 EDA过程 1.5 关于在系统编程技术 1.6 关于FPGA/CPLD的优势 1.7

2008-06-04 10:24:06 1679

1679

1679

1679Altera FPGA/CPLD设计(高级篇)

《Altera FPGA/CPLD设计(高级篇)》结合作者多年工作经验,深入地讨论了Altera FPGA/CPLD的设计、优化技巧。在讨论FPGA/CPLD设计指导原则的基础上,介绍了Altera器件的高级应用;引领读者

2009-02-12 09:19:12 4799

4799

4799

4799EDA/VHDL多媒体教学课件

EDA/VHDL讲座主要内容一、EDA、EDA技术及其应用与发展二、硬件描述语言三、FPGA和CPLD四、EDA工具软件五、电子设计竞赛几个实际问题的讨论六、VHDL语言初步七

2009-03-08 10:54:10 39

39

39

39A CPLD VHDL Introduction

A CPLD VHDL Introduction

This introduction covers the fundamentals of VHDL as applied to Complex

2009-03-28 16:14:37 25

25

25

25FPGA与VHDL快速工程实践从入门到提高

FPGA/VHDL技术是近年来计算机与电子技术领域的又一场革命。本书以AAltera公司的FPGA/CPLD为主详细介绍了FPGA、CPLD为主详细介绍了FPGA的相关知识,MAX+PLUSⅡ开发环境和VHDL语言基础,并

2009-07-11 15:06:42 58

58

58

58用VHDL语言在CPLD/ FPGA上实现浮点运算

介绍了用VHDL 语言在硬件芯片上实现浮点加/ 减法、浮点乘法运算的方法,并以Altera

公司的FLEX10K系列产品为硬件平台,以Maxplus II 为软件工具,实现了6 点实序列浮点加/ 减法

2009-07-28 14:06:13 85

85

85

85基于CPLD的计数及LED译码电路

本文采用VHDL语言设计了基于CPLD的计数及LED译码电路,该设计方法符合电子系统设计的发展方向。关键词:计数器;LED译码;CPLD;VHDL在各种检测与控制系统及仪表中,对发生的事

2009-08-24 08:32:39 28

28

28

28VHDL语言描述数字系统

VHDL语言描述数字系统:本章介绍用 VHDL 描述硬件电路的一些基本手段和基本方法。 VHDL 语言是美国国防部在 20 世纪 80 年代初为实现其高速集成电路计划(VHSIC)而提出的

2009-09-01 09:02:40 37

37

37

37基于CPLD的多通道数据采集系统设计

设计了以CPLD 为核心处理芯片的多路数据采集系统,按照正确的时序直接控制AD676和双端口RAM的工作, 所有这些功能都采用VHDL语言进行描述。关键词:CPLD, AD676, VHDL语言, 双端口R

2009-09-01 10:26:41 25

25

25

25基于CPLD的某BIT系统研制

介绍了基于CPLD 和EDA 技术的BIT(机内测试)系统的实现。本系统以CPLD 为控制核心,在MAX+PLUSII 环境下采用VHDL 语言实现了系统接口及测频电路。该系统具有集成度高、灵活性强、易于开

2009-09-03 09:30:51 9

9

9

9VHDL 语言程序的元素

VHDL 语言程序的元素:本章主要内容:VHDL语言的对象VHDL语言的数据类型VHDL语言的运算符VHDL语言的标识符VHDL语言的词法单元

2009-09-28 14:32:21 41

41

41

41基于CPLD的频谱电平显示电路设计与实现

本文基于VHDL硬件描述语言,利用CPLD器件EPM570T100C5和LED点阵屏实现了对音频信号的频谱显示,给出了设计过程、VHDL语言源程序和实验结果,拓展了CPLD在显示领域的应用。

2010-02-24 14:46:45 28

28

28

28基于FPGA/CPLD芯片的数字频率计设计

基于FPGA/CPLD芯片的数字频率计设计摘要:详细论述了利用VHDL硬件描述语言设计,并在EDA(电子设计自动化)工具的帮助下,用大规模可编程逻辑器件(FPGA/CPLD)实现

2010-04-30 14:45:13 132

132

132

132基于CPLD、FPGA的半整数分频器的设计

简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5和1.5的分频器的设计为例,介绍了在MaxPlusII开发软件下,利用VHDL硬件描述语言以及原理图的输入方式来设计数字逻辑电路的过

2010-07-17 17:55:57 36

36

36

36基于CPLD的频谱电平显示电路设计与实现

本文基于VHDL硬件描述语言,利用CPLD器件EPM570T100C5和LED点阵屏实现了对音频信号的频谱显示,给出了设计过程、VHDL语言源程序和实验结果,拓展了CPLD在显示领域的应用。

2010-07-17 18:07:40 25

25

25

25基于CPLD的电梯控制器的设计

探讨电梯控制技术的发展历史和技术现状,仔细研究CPLD器件的工作原理,开发流程以及VHDL语言的编程方法;采用单片CPLD器件,在MAX+plusⅡ软件环境下,运用VHDL语言设计一个16楼层单

2010-12-27 15:27:35 56

56

56

56基于CPLD/FPGA的半整数分频器的设计

摘要:简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5的半整数分频器的设计为例,介绍了在MAX+plus II开发软件下,利用VHDL硬件描述语言以及原理图的输

2006-03-13 19:36:44 869

869

869

869

用VHDL语言实现3分频电路

用VHDL语言实现3分频电路

标签/分类:

众所周知,分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁相

2007-08-21 15:28:16 5527

5527

5527

5527VHDL语言的组合电路设计

实验八、VHDL语言的组合电路设计一 实验目的1掌握VHDL语言的基本结构及设计的输入方法。2掌握VHDL语言的组合电路设计方法。二 实验设备与仪器

2009-03-13 19:26:58 2368

2368

2368

2368VHDL语言在FPGA/CPLD开发中的应用?

【摘 要】 通过设计实例详细介绍了用VHDL(VHSIC Hardware DescriptionLanguage)语言开发FPGA/CPLD的方法,以及与电路图输入和其它HDL语言相比,使用VHDL语言的优越性。

2009-05-10 19:47:30 1111

1111

1111

1111

Verilog HDL语言在FPGA/CPLD开发中的应用

摘 要:通过设计实例详细介绍了用Verilog HDL语言开发FPGA/CPLD的方法,并通过与其他各种输入方式的比较,显示出使用Verilog HDL语言的优越性。

2009-06-20 11:51:28 1857

1857

1857

1857

用VHDL语言在CPLD上实现串行通信

摘 要: 串行通信是实现远程测控的重要手段。采用VHDL语言在CPLD上实现了串行通信,完全可以脱离单片机使用。

关键词:

2009-06-20 12:43:50 570

570

570

570

基于CPLD/FPGA的半整数分频器的设计

摘要:简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5的半整数分频器的设计为例,介绍了在MAX+plus II开发软件下,利用VHDL硬件描述语言以及原理图的输

2009-06-20 12:45:00 627

627

627

627

用VHDL语言实现3分频电路(占空比为2比1)

用VHDL语言实现3分频电路(占空比为2比1)

分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁

2009-06-22 07:46:33 7831

7831

7831

7831基于VHDL语言的智能拨号报警器的设计

基于VHDL语言的智能拨号报警器的设计

介绍了以EDA技术作为开发手段的智能拨号报警系统的实现。本系统基于VHDL语言,采用FPGA作为控制核心,实现了远程防盗报警。该

2009-10-12 19:08:43 1167

1167

1167

1167

基于FPGA和VHDL语言的多按键状态识别系统

这里提出一种利用FPGA的I/0端口数多和可编程的特点,采用VHDL语言的多按键状态识别系统,实现识别60个按键自由操作,并简化MCU的控制信号。

2 系

2010-08-25 17:16:28 1025

1025

1025

1025

PLD/FPGA硬件语言设计verilog HDL

在我国使用Verilog HDL的公司比使用VHDL的公司多。从EDA技术的发展上看,已出现用于CPLD/FPGA设计的硬件C语言编译软件,虽然还不成熟,应用极少,但它有可能会成为继VHDL和Verilog之后,设计大规模CPLD/FPGA的又一种手段。

2011-03-12 11:21:20 1686

1686

1686

1686VHDL语言在状态机电路中的设计

简要介绍了 VHDL 语言进行工程设计的优点,并详细说明了利用VHDL语言设计状态机电电路的过程,最后进行了仿真,仿真结果证明该设计能够实现状态机电路的功能。

2011-07-18 10:31:20 83

83

83

83基于CPLD的VHDL语言数字钟(含秒表)设计

利用一块芯片完成除时钟源、按键、扬声器和显示器(数码管)之外的所有数字电路功能。所有数字逻辑功能都在CPLD器件上用VHDL语言实现。这样设计具有体积小、设计周期短(设计过

2011-09-27 15:08:56 366

366

366

366基于CPLD/FPGA的VHDL语言电路优化设计

VHDL(Very High Speed Integrated CIRCUITHARDWARE DESCRIPTION Language)是IEEE工业标准硬件描述语言,是随着可编程逻辑器件(PLD)的发展而发展起来的。

2012-03-02 09:16:05 3822

3822

3822

3822

基于Quartus II FPGA/CPLD数字系统设计实例(VHDL源代码文件)

本资料是关于基于Quartus II FPGA/CPLD数字系统设计实例(VHDL源代码文件),需要的可以自己下载。

2012-11-13 14:03:36 907

907

907

907FPGA和CPLD的区别及其用途介绍

,或是硬件描述语言自由的设计一个数字系统。通过软件仿真,我们可以事先验证设计的正确性。在PCB完成以后,还可以利用FPGA/CPLD的在线修改能力,随时修改设计而不必改动硬件电路。 使用FPGA/CPLD来开发数字电路,可以大大缩短设计时间,减少PCB面积,提高系统的可靠性。 FPGA/CPLD还

2017-10-09 09:52:20 14

14

14

14VHDL硬件描述语言的学习

在小规模数字集成电路就要淘汰的今天,作为一个电类专业的毕业生应该熟悉VHDL语言和CPLD、FPGA器件的设计,阎石教授新编写的教材也加入了VHDL语言方面的内容,可见使用VHDL语言将数字系统集成

2017-12-05 09:00:31 20

20

20

20如何使用FPGA CPLD 和VHDL语言设计一个交通灯控制系统

用VHDL语言设计交通灯控制系统,并在MAX+PLUS II系统对FPGA/CPLD芯片进行下载,由于生成的是集成化的数字电路,没有传统设计中的接线问题,所以故障率低、可靠性高,而且体积小。体现了EDA技术在数字电路设计中的优越性。

2018-11-05 17:36:05 23

23

23

23FPGA视频教程之FPGA和CPLD与VHDL基础知识的详细资料说明

本文档的主要内容详细介绍的是FPGA视频教程之FPGA和CPLD与VHDL基础知识的详细资料说明。主要的目的是:1.VHDL入门,2.设计单元,3.体系结构建模基础,4.VHDL逻辑综合,5.层次

2019-03-20 14:35:19 9

9

9

9什么是vhdl语言_简述vhdl语言的特点

什么是vhdl语言 VHDL 的英文全名是VHSIC Hardware Description Language(VHSIC硬件描述语言)。VHSIC是Very High Speed

2020-04-23 15:58:49 10242

10242

10242

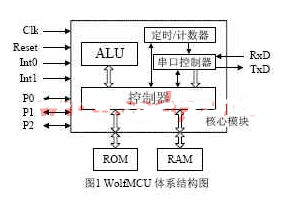

10242采用VHDL语言在FPGA上实现WolfMCU体系结构的设计

基于以上讨论,可以看出ASIP+FPGA设计模式可以从很大程度上解决引言中提到的两个难题。为了进行更深入的研究,我们对该设计模式进行了尝试,用VHDL硬件描述语言在FPGA上实现了一个8位微处理器

2020-07-28 17:44:49 562

562

562

562

fpga用什么编程语言_fpga的作用

经常看到不少人在论坛里发问,FPGA是不是用C语言开发的?国外有些公司专注于开发解决编译器这方面问题,目的让其能够达到用C语言替代VHDL语言的目的,也开发出了一些支持用c语言对FPGA进行编程的开发工具。但在使用多的FPGA编程语言还是verilog和VHDL语言,一般不使用C语言进行编程。

2020-07-29 16:37:37 23118

23118

23118

23118常用FPGA/CPLD设计思想与技巧

都是FPGA/CPLD逻辑设计的内在规律的体现,合理地采用这些设计思想能在FPGA/CPLD设计工作种取得事半功倍的效果。

2023-05-18 08:56:57 350

350

350

350

fpga用的是什么编程语言 fpga用什么语言开发

和VHDL都是用于逻辑设计的硬件描述语言,并且都已成为IEEE标准。它们能形式化地抽象表示电路的结构和行为,支持逻辑设计中层次与领域的描述,具有电路仿真与验证机制以保证设计的正确性,并便于文档管理和设计重用。 fpga用什么语言开发 FPGA(现场可编程逻辑门阵列)的开发主要使用硬件描述语言(HD

2024-03-14 17:09:32 223

223

223

223fpga语言是什么?fpga语言与c语言的区别

功能,从而实现对数字电路的高效定制。FPGA语言主要包括VHDL(VHSIC Hardware Description Language)和Verilog等,这些语言具有强大的描述能力,能够精确地定义硬件的每一个细节,从而实现复杂的数字系统设计。

2024-03-15 14:50:26 166

166

166

166 电子发烧友App

电子发烧友App

评论