数据采集板作为雷达信号处理系统中的接收前端,必须面对越来越高的要求,为后续信号处理提供可靠的保证。将数据采集板独立设计提高了通用性,降低了系统的研制时间,因此成为雷达信号处理系统设计的发展趋势。采用ADC和FPGA设计了基于CPCI总线的数据采集板,实现了8路信号同时中频采样及处理,并已应用于雷达系统中。

关键词: 数据采集板;ADC;FPGA;CPCI

The Design and Realization of the Data Sampling Board

Abstract:

With the development of modern radar,the data sampling board used as the receiver of a system of radar signal processing must face the increasingly high requirements,and guarantee the reliability of posterior signal processing.The data sampling board is designed specially,which improves the generality and shortens the time for design,so that it has become the development trend of signal processing system design.This paper adopts FPGA and ADC to design a data sampling board for signal processing based on the CPCI Bus,which accomplishes eight channels of IF signal sampling and processing,and has been used in some radar systems.

Keywords: data sampling board;ADC;FPGA;CPCI

随着先进雷达功能多样化、复杂化, 要求研制、装备周期越来越短, 有必要设计一种通用性强、功能强大的数据采集板, 以支持雷达技术发展的需要, 这无论是在硬件还是软件编程的实现方面, 都为其可通用性打下坚实的基础。在实现技术上, 近些年来, 一改以往传统的模拟处理方法, 多采用数字中频正交采样技术, 这种做法直接对模拟中频信号进行单路采样, 再以一定方法实现数字下变频, 得到所需的两路正交信号。由于两路信号是经数字处理得到的, 因此可以达到较高的精度,两路正交信号的幅度和相位一致性都较好。

文中所设计的系统正是基于上述几点应用而生的, 采用的核心器件是Analog Devices公司的A /D芯片和Altera 高端高密度、低功耗、低成本的FPGAStratix II, 设计了基于CPCI总线的数据采集板, 实现了单板8路信号的中频采样及数据的实时处理, 并在某雷达系统中进行了实际应用。

1 系统设计

所要设计的系统可以同时接收8 路中频模拟信号, 并在FPGA中同时对8路数字信号进行下变频处理, 得到所需要的检波信号, 然后送往后端继续进行处理。实际硬件设计实现中, 系统大致可分为模拟和数字两部分, 模拟部分实现中频采样, 核心器件采用的是AD6645ASQ; 数字部分实现数字下变频(DDC) ,通过FPGA (EP2S60)来实现。

模拟部分选用美国Analog Devices公司的模数转换芯片AD6645ASQ, 它是一个完整的14 位集成ADC, 功耗115 W, 芯片结构采用的是串/并行编码相结合的方法, 兼顾速度与成本, 其主要特性在于:中频采样最高能到200MHz; 输入时钟和模拟信号都采用差分电平格式, 降低了干扰; 器件信噪比高; 而且其工作温度范围(环境) : - 40~ + 85°C[ 7 ] , 能够满足一般雷达系统对环境温度要求 。数字部分选用的是Altera 公司采用112 V,90 nm, 9层金属走线、全铜SRAM工艺制造的中高端FGPA产品Stratix II系列的EP2S60, 采用全新的逻辑结构: 自适应逻辑模块(ALM) , 兼有“窄”逻辑结构的高利用率和“宽”逻辑结构的高性能, 实际中可以根据用户的需求由设计工具自动配置成需要的模式。它内含144个18 ×18的定点硬件乘法器, 24 176个自适应逻辑模块以及215MB的内嵌RAM, 丰富的硬件资源足以实现其对系统的8路中频信号进行实时处理成为可能。

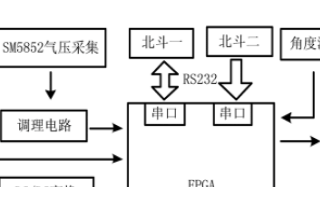

系统硬件总体结构, 如图1所示。

图1 系统硬件总体架构

8路模拟信号经由50Ω匹配电路, 通过A /D直接对中频信号进行采样和幅度量化, 再由FPGA得到正交双通道数据的方法来实现正交相干检波, 处理后数据经并/串转换送往CPC I_J5 口供后端继续处理,处理时所需的控制信号同样由此接口输入; 各芯片工作所用的时钟信号由中间的时钟电路统一产生, 保证各时钟的相位基本一致。

2 数字正交采样在数据采集板上的系统实现

211 数据采集板中频采样的实现一个中频窄带信号可以表示为

30MHz的线性调频信号, 设计系统时M 值取为2,则时钟设计所定的fs = 40 MHz, 通过FPGA实测得到中频采样数据, 如图2所示。

图2 FPGA实测中频采样数据

2 12 数据采集板数字下变频的实现

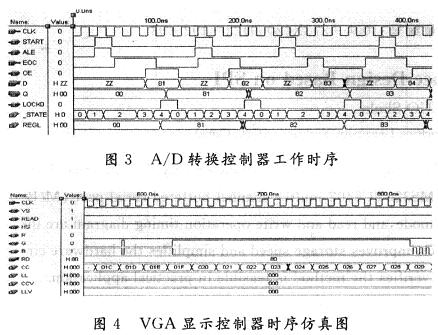

对中频实信号进行采样后, 下一步是进行数字混频和滤波处理, 使信号变为零中频正交信号(零中频正交信号即是回波信号的复包络, 包含了回波的所有有用信息) , 即为数字下变频, 其作为雷达信号处理中的关键技术之一, 这里采用低通滤波法来实现, 低通滤波法包括正交插值、低通滤波和抽样3个部分。数字下变频的算法框图, 如图3所示。

图3 数字下变频算法框图

相比于传统的模拟处理方法, 本方法从根本上解决I, Q两路正交误差和幅度不平衡, 提高了镜频抑制比。

其中混频, 即点乘的实现, 根据中频带通采样定理有

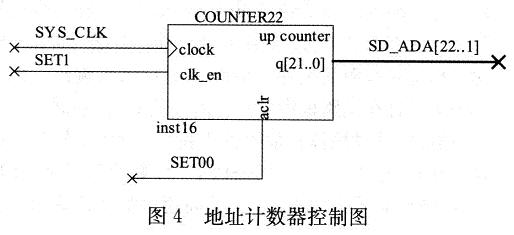

这是以{1, 0, - 1, 0}和{0, 1, 0, - 1}为周期循环的两个序列。当外部数据进来时根据不同时刻输出不同的数据, 主要包括原值、原值取反和0。其FPGA实现电路, 如图4所示。

图4 数字混频的FPGA实现电路

在整个正交相干检波过程中, 除了ADC的量化影响外, 整个正交检波系统的性能, 由低通滤波器的设计决定。由于镜频分量处于滤波器的阻带, 因而阻带衰减决定了镜频的抑制程度。文中采用的低通滤波器为24阶F IR滤波器, 其阻带衰减> 70 dB镜频分量得到了较好的抑制 。24阶FIR滤波器的频率特性, 如图5所示。

输入时宽带宽积为55的线性调频信号, 实测的I路与Q路波形, 如图6所示。

把实测数据导到Matlab进行分析, 得到镜频抑制比满足系统的要求, 如图7所示。

图7 系统实测数据, 低通滤波法频率归一化后的镜频抑制比数据采集板实物图, 如图8所示。

3 结束语

文中设计的基于CPCI总线的数据采集板, 8路信号同时采集并处理, 兼备强大的数据处理能力和高实时性。整个系统实现的是数字正交采样, 无论是中频采样, 还是数字下变频, 都有一定的通用性, 在以后类似的应用中, 无需重新设计, 只需通过资源分配和算法的再实现, 足以达到预期的效果, 保证可靠性的同时也大大的缩短了研制周期。

图8 数据采集板实物图

实时性。整个系统实现的是数字正交采样, 无论是中频采样, 还是数字下变频, 都有一定的通用性, 在以后类似的应用中, 无需重新设计, 只需通过资源分配和算法的再实现, 足以达到预期的效果, 保证可靠性的同时也大大的缩短了研制周期。

参考文献

[ 1 ] Analog Devices. AD6645 14 bit, 80 /105 MSPS A /D ConverterData Sheet [ Z]. USA: Analog Devices, 2005.

[ 2 ] Altera Corporation. Stratix III Handbook [ Z]. USA: Altera Corporation, 2008.

[ 3 ] 郑君里, 应启珩, 杨为理. 信号与系统[M ]. 2版. 北京: 人民邮电出版社, 2002.

[ 4 ] 何海兴. 多模式雷达中正交检波和脉冲压缩的研究与实现[D ]. 西安: 西安电子科技大学, 2007.

[ 5 ] 王本明. 基于CPCI总线的通用FPGA信号处理板设计[D ]. 西安: 西安电子科技大学, 2009.

[ 6 ] 胡成冈. FPGA在雷达信号处理中的应用[D ]. 西安:西安电子科技大学, 2007.

电子发烧友App

电子发烧友App

评论