1 引 言

MPEG(活动影像专业人员组织)是为数字音频确定单一编码和解码(压缩/解压缩)方法于1988年建立的。1992年,国际标准组织(ISO)和国际电工委员会(IEC)为音频和视频编码建立了MPEG1(ISO/IEC11172)标准。这使得业内在处理新数字世纪出现的各种类型音频/视频媒体时统一在单一格式上。

随着以数字形式存储和播放音乐的MPEG Audio Layer3(MP3)格式的发展,个人数字播放机市场开始出现巨大的发展机会。非压缩的音频磁轨的MP3数字文件只有原来磁轨大小的1/10。能保持74分钟数字音频录音时间的650Mbytes读写CD可以保持740分钟MP3压缩音频数据。

数字播放机的一般解决方案是采用软件形式(如基于Windows或其他OS基础上的“Internet Audio Player”)或硬件形式(如“Portable MP3 Player”)。如Diamond Multimedia公司的Rio PMP300和Rio PMP500 MP3数字播放机分别采用Actel公司的A40MX04和A40MX09 FPGA实现其特殊应用功能。FP GA能满足整个系统的价格、功耗和性能要求。A40MX04提供547个逻辑模块,它们可配置做为组合逻辑或273个触发器和实现接口逻辑的69个I/O。A40MX04和A40MX09很容易满足48MHz速度要求。它们灵活的结构使系统设计人员能在每种MP3播放机中最佳地实现各种功能。

2 MP3数字播放机系统要求

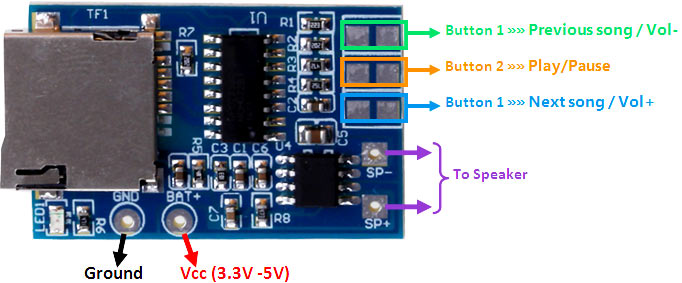

MP3播放机有两个基本工作模式:下载模式和播放模式。在下载模式中,在PC上运行的软件允许用户下载MP3文件到播入机中的闪存卡。一旦把所有文件下载完,播放机与PC断开,并通过耳机收听下载的音乐。MP3播放机有不同的播放选择控制,如播放、快进、快倒、停止/暂停、音量控制、随机播放和重复播放功能。

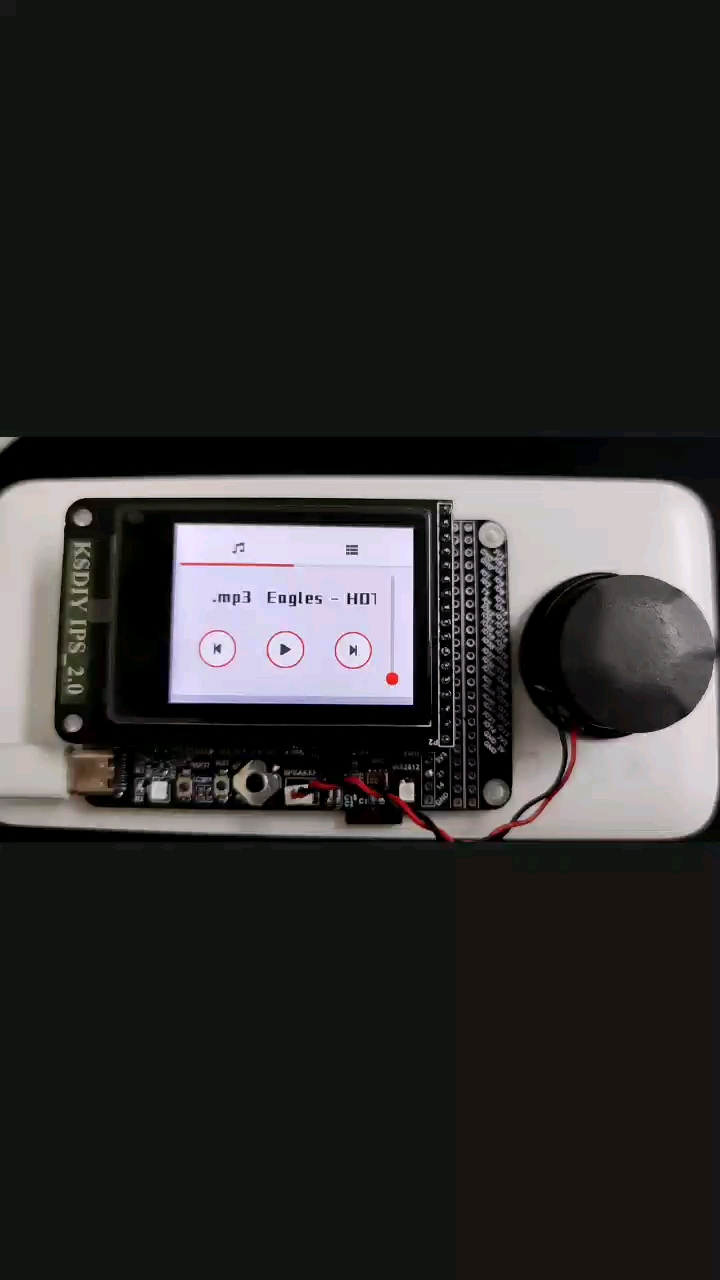

MP3播放机包含可输入到PC的软件。软件提供用户接口以便通过PC并行端口选择、定序和下载不同音乐的MP3文件到播放机。图1示出系统级框图。

通过并行端口下载音乐到播放机,其速率大约为每1MB编码音乐10秒。MP3播放机的小尺寸对所有元件的物理尺寸有严格限制。另外,MP3播放机是便携、电池供电装置,需要工作在大约180mW低功率下。这两个因素对功能设计的元件选择有很大的影响。

3 用FPGA实现MP3系统

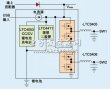

图2示出Rio PMP500系统框图,其中A42MX09 FPGA做为接口FPGA,它包含CPU接口、带ECC(Error Correcting Code)支持的闪存和灵巧存储器接口、时钟产生逻辑、功能控制逻辑和键功能检测逻辑单元。

A42MX09中的CPU I/F单元提供与系统CPU(NECD78P064GC微控制器,带集成LCD控制器)的通信通路。CPU运行在2.5MHz,控制整个系统的工作。对于任何所需要的操作,CPU唤醒系统并设置整个系统。CPU存取系统存储器和管理整个闪存的配置、编程和存取。CPU有一个到MP3处理器的接口。MP3从闪存读的数据由CPU写到MP3处理器。MP3处理器译码MP3数据并把数据送到DAC,以便模拟输出到耳机。

A42MX09中的灵巧存储器接口单元是连接灵巧存储器卡的接口。灵巧存储器卡是一个外部闪存,用来增加整个系统存储器以便在播放机中存储更多的歌曲。到灵巧存储器卡的信号接口非常类似于闪存接口。

闪存接口单元用于控制闪存,闪存保存通过并行端口下载的MP3文件。另外,ECC用Hamming码函数实现。Hamming码是一种FEC(Forward Error Correction)工具,当所用数据通过噪声媒体时FEC能校正错误。原始数据具有额外的校验位附加在每个字组以生成一个码字。这些额外位用“Block Parity”机理计算。采用模2运算用数据位来生成矩阵G得到Hamming码字。这需要乘法功能,而用A42MX09中的逻辑模块的组合功能很容易实现乘法功能。

A42MX09中的时钟产生器从48MHz输入时钟产生驱动器件内部不同逻辑单元所需的不同时钟。时钟产生逻辑单元由触发器和组合逻辑构成分频器。A42MX09中的键盘检测单元用于改变播放机的设置。键盘接口单元一般由检测键盘阵列中连接点(根据按键)的逻辑单元构成并把按键转变为与该键相关的功能。根据按键检测执行适当的功能。阵列由寄存器、锁存器和组合逻辑实现。

Rio MP3播放机的功率由MAX1M1705器件控制,而1705由FPGA功耗控制单元控制。MP3播放机一般由单节1.5V电池供电。电池最少应能维持12小时听所有下载的音乐。功率控制是Rio MP3播放机的一个显著的特点。功率控制器件有两种功率工作模式:PFM(脉冲频率调制)和PWM(脉宽调制)模式。

PFM模式是低静态电流待机模式,此模式提供120mA总输出电流并降低静态功耗到500uW。PWM模式是高功耗模式,能提供高达450mA输出电流。当MP3播放机处于停机状态时,CPU编程写FPGA的一个寄存器,从而产生MODE信号置MAX1M器件进入PFM低功率模式。在PFM模式Rio MP3播放机功耗只有2mW~3mW。当MP3播放机工作时,MODE信号改变MAX1M器件到PWM模式。Rio MP3播放机工作状态时的总功率大约在180mW左右。

4 下一代MP3系统

下一代MP3系统将改变现在的系统,能提供更快的下载、更多的用于播放的音乐文件和更多的用户从接口/键面板选择。更快的下载可通过采用高速并行端口模式(见IEEE1284)或USB端口实现。采用高密度闪存连同本地SDRAM基歌曲高速缓冲存储器可提供更多音乐文件播放并可提供另外的选择,如快速播放、快进、慢播放、编程播放等。其他选择可包括红外收发器,可使用户从播放机到播放机来回发射数据或执行某些远程控制操作。整个系统可用一个FPGA实现,不需要CPU。在FPGA中的音频DAC控制器逻辑单元可提供I2C接口来控制音频DAC,音频DAC通过I2C接口取串行音频数据并变换为模拟音频提供给耳机。

其他新的压缩方法正在涌现,其中ATRAC3(Adaptive Transform Acoustic Coding—自适应变换声频编码)标准可压缩CD音乐数据10:1而又能保持CD音质。

ATRAC3特点是:

1、通过频带分裂滤波器和MDCT(Modified Discrete Cosine Transforms—改进式离散余弦变换)对信号分析获得的。

2、位率压缩。利用ATRAC3技术,能实现音乐信号的高效率压缩。

MPEG(活动影像专业人员组织)是为数字音频确定单一编码和解码(压缩/解压缩)方法于1988年建立的。1992年,国际标准组织(ISO)和国际电工委员会(IEC)为音频和视频编码建立了MPEG1(ISO/IEC11172)标准。这使得业内在处理新数字世纪出现的各种类型音频/视频媒体时统一在单一格式上。

随着以数字形式存储和播放音乐的MPEG Audio Layer3(MP3)格式的发展,个人数字播放机市场开始出现巨大的发展机会。非压缩的音频磁轨的MP3数字文件只有原来磁轨大小的1/10。能保持74分钟数字音频录音时间的650Mbytes读写CD可以保持740分钟MP3压缩音频数据。

数字播放机的一般解决方案是采用软件形式(如基于Windows或其他OS基础上的“Internet Audio Player”)或硬件形式(如“Portable MP3 Player”)。如Diamond Multimedia公司的Rio PMP300和Rio PMP500 MP3数字播放机分别采用Actel公司的A40MX04和A40MX09 FPGA实现其特殊应用功能。FP GA能满足整个系统的价格、功耗和性能要求。A40MX04提供547个逻辑模块,它们可配置做为组合逻辑或273个触发器和实现接口逻辑的69个I/O。A40MX04和A40MX09很容易满足48MHz速度要求。它们灵活的结构使系统设计人员能在每种MP3播放机中最佳地实现各种功能。

2 MP3数字播放机系统要求

MP3播放机有两个基本工作模式:下载模式和播放模式。在下载模式中,在PC上运行的软件允许用户下载MP3文件到播入机中的闪存卡。一旦把所有文件下载完,播放机与PC断开,并通过耳机收听下载的音乐。MP3播放机有不同的播放选择控制,如播放、快进、快倒、停止/暂停、音量控制、随机播放和重复播放功能。

MP3播放机包含可输入到PC的软件。软件提供用户接口以便通过PC并行端口选择、定序和下载不同音乐的MP3文件到播放机。图1示出系统级框图。

通过并行端口下载音乐到播放机,其速率大约为每1MB编码音乐10秒。MP3播放机的小尺寸对所有元件的物理尺寸有严格限制。另外,MP3播放机是便携、电池供电装置,需要工作在大约180mW低功率下。这两个因素对功能设计的元件选择有很大的影响。

3 用FPGA实现MP3系统

图2示出Rio PMP500系统框图,其中A42MX09 FPGA做为接口FPGA,它包含CPU接口、带ECC(Error Correcting Code)支持的闪存和灵巧存储器接口、时钟产生逻辑、功能控制逻辑和键功能检测逻辑单元。

A42MX09中的CPU I/F单元提供与系统CPU(NECD78P064GC微控制器,带集成LCD控制器)的通信通路。CPU运行在2.5MHz,控制整个系统的工作。对于任何所需要的操作,CPU唤醒系统并设置整个系统。CPU存取系统存储器和管理整个闪存的配置、编程和存取。CPU有一个到MP3处理器的接口。MP3从闪存读的数据由CPU写到MP3处理器。MP3处理器译码MP3数据并把数据送到DAC,以便模拟输出到耳机。

A42MX09中的灵巧存储器接口单元是连接灵巧存储器卡的接口。灵巧存储器卡是一个外部闪存,用来增加整个系统存储器以便在播放机中存储更多的歌曲。到灵巧存储器卡的信号接口非常类似于闪存接口。

闪存接口单元用于控制闪存,闪存保存通过并行端口下载的MP3文件。另外,ECC用Hamming码函数实现。Hamming码是一种FEC(Forward Error Correction)工具,当所用数据通过噪声媒体时FEC能校正错误。原始数据具有额外的校验位附加在每个字组以生成一个码字。这些额外位用“Block Parity”机理计算。采用模2运算用数据位来生成矩阵G得到Hamming码字。这需要乘法功能,而用A42MX09中的逻辑模块的组合功能很容易实现乘法功能。

A42MX09中的时钟产生器从48MHz输入时钟产生驱动器件内部不同逻辑单元所需的不同时钟。时钟产生逻辑单元由触发器和组合逻辑构成分频器。A42MX09中的键盘检测单元用于改变播放机的设置。键盘接口单元一般由检测键盘阵列中连接点(根据按键)的逻辑单元构成并把按键转变为与该键相关的功能。根据按键检测执行适当的功能。阵列由寄存器、锁存器和组合逻辑实现。

Rio MP3播放机的功率由MAX1M1705器件控制,而1705由FPGA功耗控制单元控制。MP3播放机一般由单节1.5V电池供电。电池最少应能维持12小时听所有下载的音乐。功率控制是Rio MP3播放机的一个显著的特点。功率控制器件有两种功率工作模式:PFM(脉冲频率调制)和PWM(脉宽调制)模式。

PFM模式是低静态电流待机模式,此模式提供120mA总输出电流并降低静态功耗到500uW。PWM模式是高功耗模式,能提供高达450mA输出电流。当MP3播放机处于停机状态时,CPU编程写FPGA的一个寄存器,从而产生MODE信号置MAX1M器件进入PFM低功率模式。在PFM模式Rio MP3播放机功耗只有2mW~3mW。当MP3播放机工作时,MODE信号改变MAX1M器件到PWM模式。Rio MP3播放机工作状态时的总功率大约在180mW左右。

4 下一代MP3系统

下一代MP3系统将改变现在的系统,能提供更快的下载、更多的用于播放的音乐文件和更多的用户从接口/键面板选择。更快的下载可通过采用高速并行端口模式(见IEEE1284)或USB端口实现。采用高密度闪存连同本地SDRAM基歌曲高速缓冲存储器可提供更多音乐文件播放并可提供另外的选择,如快速播放、快进、慢播放、编程播放等。其他选择可包括红外收发器,可使用户从播放机到播放机来回发射数据或执行某些远程控制操作。整个系统可用一个FPGA实现,不需要CPU。在FPGA中的音频DAC控制器逻辑单元可提供I2C接口来控制音频DAC,音频DAC通过I2C接口取串行音频数据并变换为模拟音频提供给耳机。

其他新的压缩方法正在涌现,其中ATRAC3(Adaptive Transform Acoustic Coding—自适应变换声频编码)标准可压缩CD音乐数据10:1而又能保持CD音质。

ATRAC3特点是:

1、通过频带分裂滤波器和MDCT(Modified Discrete Cosine Transforms—改进式离散余弦变换)对信号分析获得的。

2、位率压缩。利用ATRAC3技术,能实现音乐信号的高效率压缩。

电子发烧友App

电子发烧友App

评论